# **SIEMENS**

|                                      | Preface, Contents                                |    |

|--------------------------------------|--------------------------------------------------|----|

|                                      | Introduction                                     | 1  |

|                                      | User Program                                     | 2  |

| SIMATIC S5                           | Program Execution                                | 3  |

|                                      | Operating Modes and Program<br>Processing Levels | 4  |

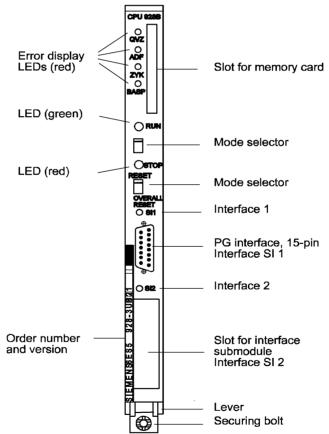

| S5-135U<br>CPU 928B - Version -3UB21 | Interrupt and Error Handling                     | 5  |

|                                      | Integrated Special Functions                     | 6  |

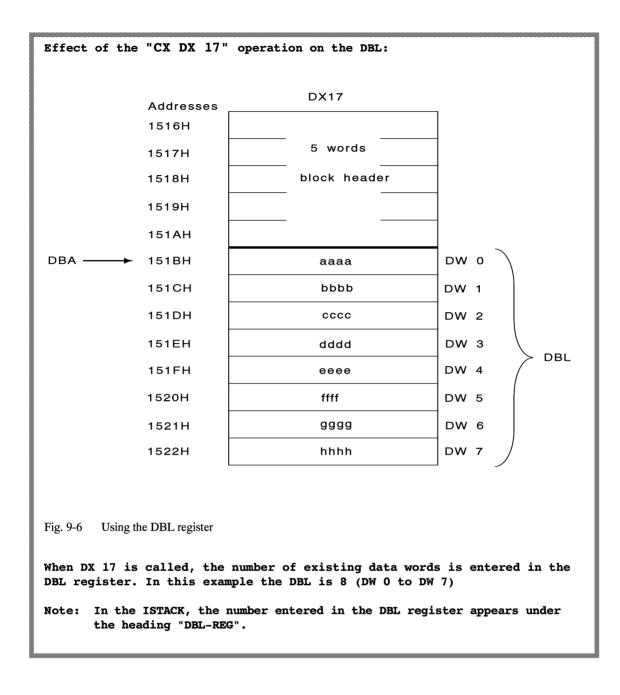

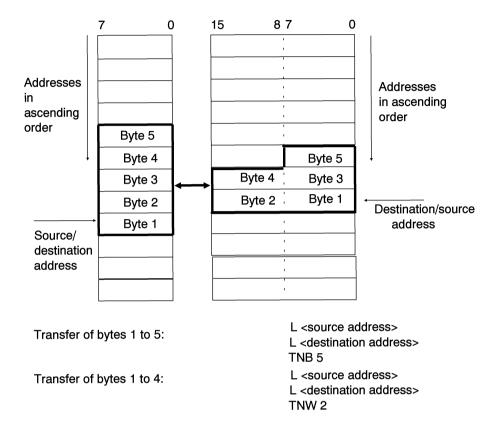

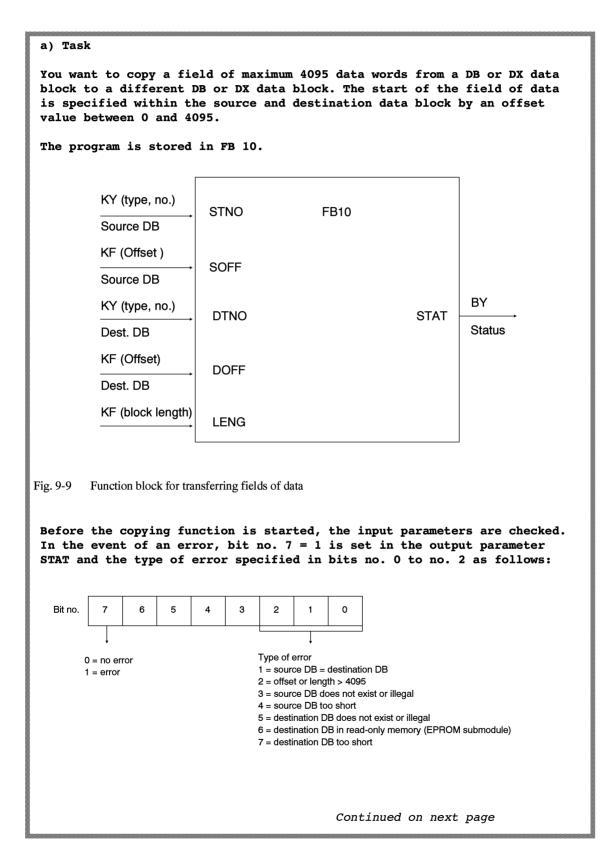

| Programming Guide                    | Extended Data Block DX 0                         | 7  |

|                                      | Memory Assignment and Memory Organization        | 8  |

|                                      | Memory Access Using Absolute<br>Addresses        | 9  |

|                                      | Multiprocessor Mode and Communication            | 10 |

|                                      | PG Interfaces and Functions                      | 11 |

|                                      | Appendix                                         | Α  |

|                                      | Further Reading                                  | B  |

|                                      | List of Abbreviations                            | С  |

|                                      | Glossary, Index                                  | _  |

The CPU 928/CPU 928B/CPU 948, List of Operations, order no. 6ES5 997-3UA23, Rel. 01 is included with this manual.

#### **Safety Guidelines**

This manual contains notices which you should observe to ensure your own personal safety, as well as to protect the product and connected equipment. These notices are highlighted in the manual by a warning triangle and are marked as follows according to the level of danger:

#### Danger

indicates that death, severe personal injury or substantial property damage will result if proper precautions are not taken.

#### Warning

indicates that death, severe personal injury or substantial property damage can result if proper precautions are not taken.

#### Caution

indicates that minor personal injury or property damage can result if proper precautions are not taken.

| Ν | 01 | te |

|---|----|----|

|   |    |    |

draws your attention to particularly important information on the product, handling the product, or to a particular part of the documentation.

Qualified Personnel The device/system may only be set up and operated in conjunction with this manual.

Only **qualified personnel** should be allowed to install and work on this equipment. Qualified persons are defined as persons who are authorized to commission, to ground, and to tag circuits, equipment, and systems in accordance with established safety practices and standards.

**Correct Usage**

#### Note the following:

$\triangle$

#### Warning

This device and its components may only be used for the applications described in the catalog or the technical description, and only in connection with devices or components from other manufacturers which have been approved or recommended by Siemens.

This product can only function correctly and safely if it is transported, stored, set up, and installed correctly, and operated and maintained as recommended.

Trademarks

SIMATIC® and SINEC® are registered trademarks of SIEMENS AG.

Third parties using for their own purposes any other names in this document which refer to trademarks might infringe upon the rights of the trademark owners.

#### Copyright © Siemens AG 1996 All rights reserved

The reproduction, transmission or use of this document or its contents is not permitted without express written authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved.

Siemens AG Automation Group Industrial Automation Systems Postfach 4848, D-90327 Nürnberg

#### **Disclaimer of Liability**

We have checked the contents of this manual for agreement with the hardware and software described. Since deviations cannot be precluded entirely, we cannot guarantee full agreement. However, the data in this manual are reviewed regularly and any necessary corrections included in subsequent editions. Suggestions for improvement are welcomed.

© Siemens AG 1996 Technical data subject to change.

Siemens Aktiengesellschaft

6ES5998-2PR22

## Preface

Scope of the<br/>ManualThis programming guide describes the CPU 928B-3UB21 and its system<br/>software.

| Overview of the<br>Chapters | <b>Chapter 1</b> informs you about the areas of application of the S5-135U programmable controller with the CPU 928B and its device structure. It explains the typical mode of operation of the CPU and illustrates how a CPU program is structured.                                      |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             | The chapter also contains suggestions about how to tackle programming and which characteristics of the CPU 928B-3UB21 are important for programming.                                                                                                                                      |

|                             | If you have already worked with the CPU 928B-3UB12 and want to know the differences between this CPU and the CPU 928B-3UB21 you will find this information in this chapter.                                                                                                               |

|                             | <b><u>Chapter 2</u></b> explains the components of a STEP 5 user program and how the program can be structured.                                                                                                                                                                           |

|                             | <b>Chapter 3</b> is intended for readers who do not yet have much experience of using the STEP 5 programming language. It therefore deals with the basics of STEP 5 programming and explains the STEP 5 operations in detail (with examples).                                             |

|                             | Experienced readers who may find that the information about specific operations in the pocket guide is inadequate, can use Section 3.5 as a reference section.                                                                                                                            |

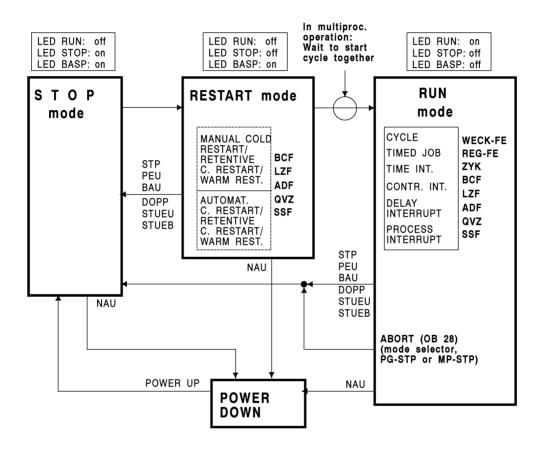

|                             | <b>Chapter 4</b> provides an overview of the modes and program execution levels of the CPU 928B. It provides you with detailed information about various start-up modes and the associated organization blocks in which you can program your routines for differrent start-up situations. |

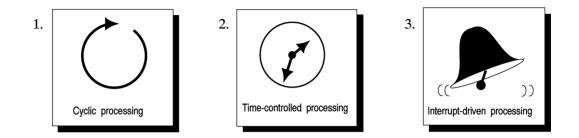

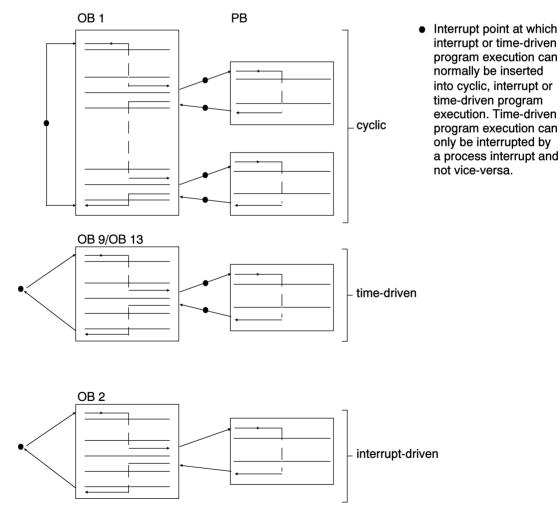

|                             | The chapter also explains the differences between the program execution levels "cyclic processing", "time-controlled processing" and "interrupt-driven processing" and which blocks are available for your user program.                                                                  |

|                             | <b><u>Chapter 5</u></b> informs you about errors to be avoided when planning and writing your STEP 5 programs.                                                                                                                                                                            |

|                             | The chapter tells you about the help you can obtain from the system program for<br>diagnosing errors and which reactions can be expected and informs you about the<br>blocks in which you can program reactions to certain errors.                                                        |

|                             | <b>Chapter 6</b> covers the special functions integrated in the system program. It tells you how to use the special functions and how to call and assign parameters to the special function OBs.                                                                                          |

|                             | The chapter also explains how to recognize and deal with errors in the processing of a special function.                                                                                                                                                                                  |

|                             |                                                                                                                                                                                                                                                                                           |

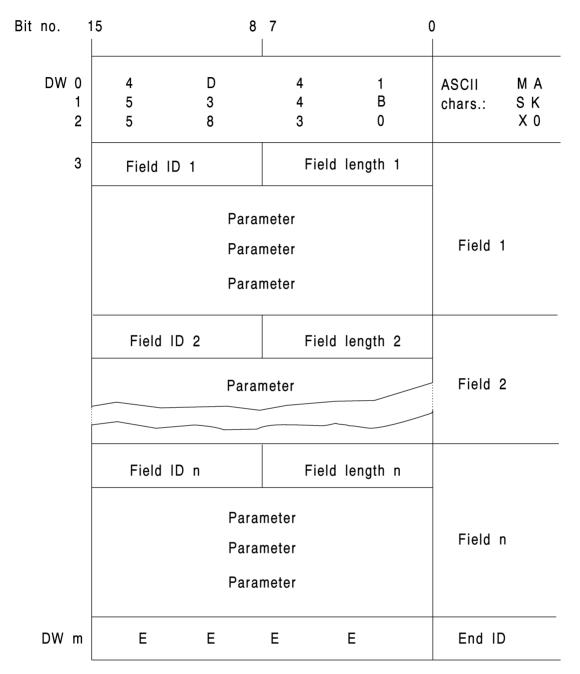

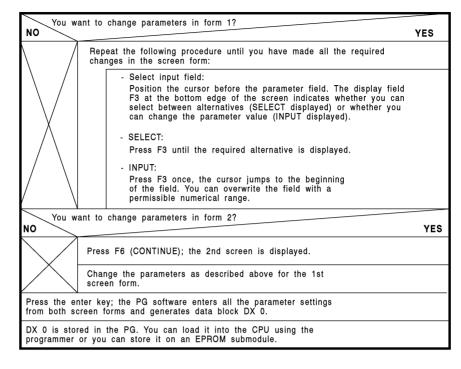

<u>Chapter 7</u> describes the use of data block DX 0 and its structure. The chapter informs you of the significance of the various DX 0 parameters. Based on examples, you will learn how to create data block DX 0 or how to assign the parameters in a screen form.

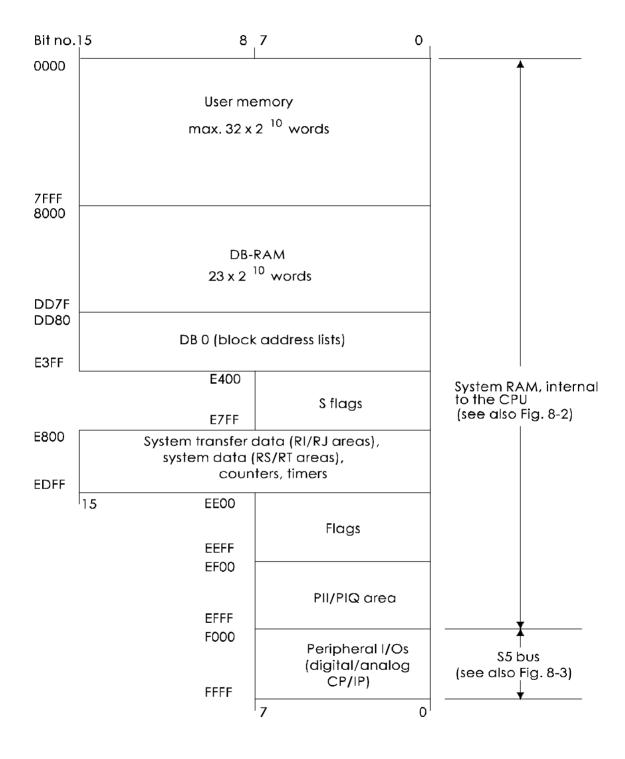

<u>Chapter 8</u> is a reference section for experienced system users. It provides information about the memory organization of the CPU 928B and certain system data words which contain information that can be called up by the user.

You will also learn how you can switch software protection for your CPU on and off via a system data word.

**<u>Chapter 9</u>** is also for experienced system users. The chapter explains how to address data in certain memory areas using absolute addresses.

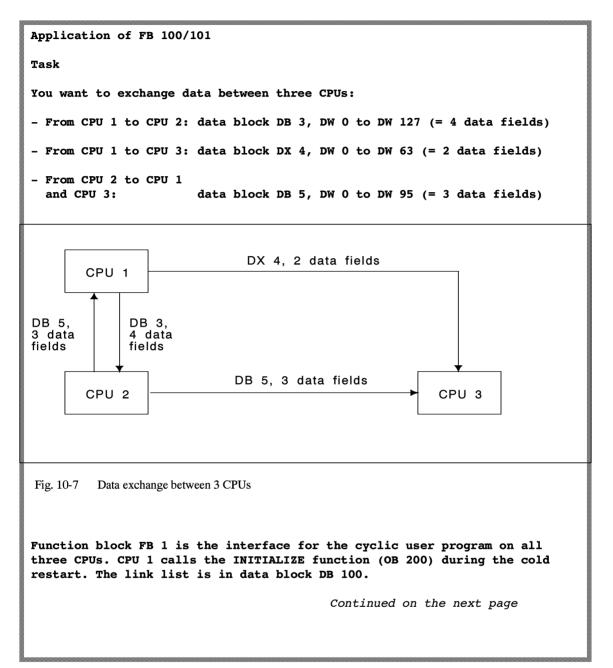

<u>Chapter 10</u> lists a number of points about using multiprocessor operation and the possibility of using it to exchange data between CPUs and CPs.

The chapter provides information about programming for multiprocessor operation.

The remainder of the chapter provides detailed information and application examples for exchanging larger amounts of data in the multiprocessor mode (multiprocessor communication).

<u>Chapter 11</u> tells you how to connect your CPU to a PG and the functions provided by the PG software to test your STEP 5 program.

<u>Appendix A</u> contains an overview of the characteristic technical data of the CPUs 928A, 928B und 948 for camparison purposes.

Appendix B lists documentation for further reading.

<u>Appendix C</u> is intended to help you find themes quickly and contains a list of abbreviations and a list of keywords.

*Conventions used in the text*

#### Second-level section numbering

Larger sub-chapters (e.g. 4.3) with second-level numbers start at the top of a new page with a bold heading and appear in the list of contents.

#### **Block labels**

Bold headings (block labels) appear in the margin on the left of the page to make it easier for you to find technical information.

#### <u>Notes</u>

**Note** Important information is indicated in this format.

#### Tables for reference

Table 3-2 Binary logic operations

| Operation | Operand        | Function                                           |

|-----------|----------------|----------------------------------------------------|

| А         |                | AND logic operation with scan for signal state "1" |

| 0         |                | OR logic operation with scan for signal state "1"  |

|           | I 0.0 to 127.7 | of an input in the PII<br>                         |

#### Examples

Examples, some of which cover several pages, are highlighted by a gray frame. When the examples cover more than one page this is clearly indicated.

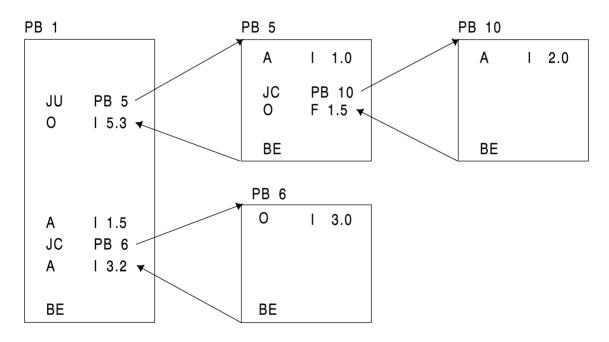

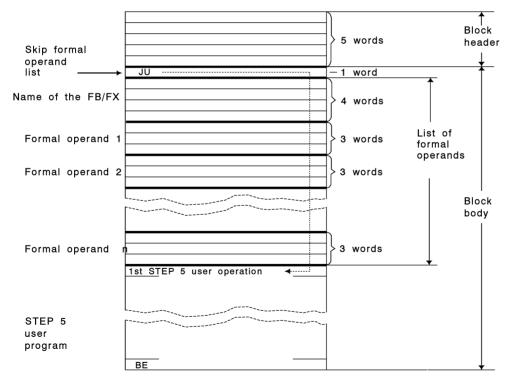

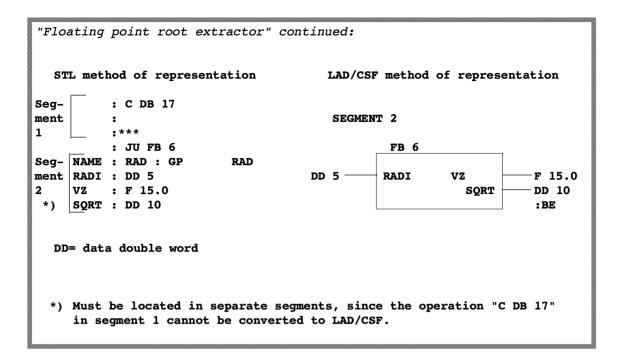

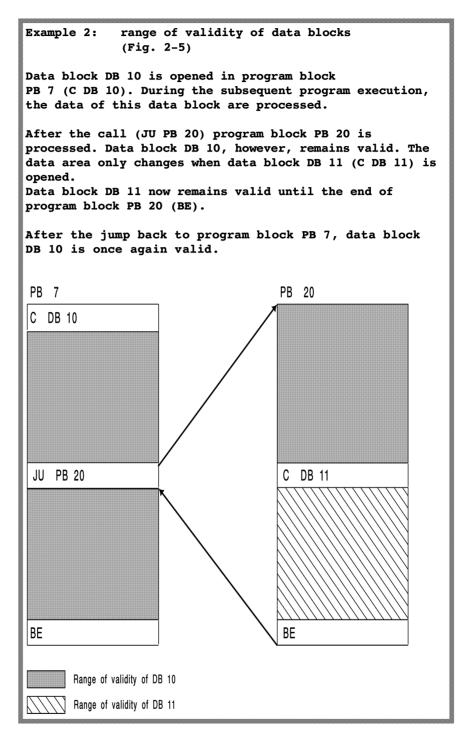

Example 1: Calling and assigning parameters to a function block in the methods of representation STL and LAD/CSF in a program block

Method of representation STL

• • • • • •

## Contents

| 1   | Introduction 1-1                                          |                                                                                                                                                                                          |

|-----|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1 | Area of Application for the S5-135U with the CPU 928B 1-2 |                                                                                                                                                                                          |

| 1.2 | Typical Mode of Operation of a CPU 1-3                    |                                                                                                                                                                                          |

| 1.3 | The Pro<br>1.3.1<br>1.3.2                                 | ograms in a CPU1-5System Program1-5User Program1-7                                                                                                                                       |

| 1.4 | Which                                                     | Operands are available to the User Program? 1-9                                                                                                                                          |

| 1.5 | Accessi                                                   | ing Operand Areas and Memory Areas 1-12                                                                                                                                                  |

| 1.6 | How to                                                    | Tackle Programming    1-13                                                                                                                                                               |

| 1.7 | Program                                                   | nming Tools 1-16                                                                                                                                                                         |

| 1.8 | What is                                                   | s New with the CPU 928B (-3UB21)? 1-17                                                                                                                                                   |

| 2   | User P                                                    | rogram                                                                                                                                                                                   |

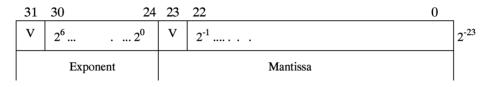

| 2.1 | STEP 5<br>2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>2.1.5       | 5 Programming Language2-2The LAD, CSF, STL Methods of Representation2-2Structured Programming2-4STEP 5 Operations2-5Number Representation2-6STEP 5 Blocks and Storing them in Memory2-10 |

| 2.2 | Program<br>2.2.1<br>2.2.2                                 | n, Organization and Sequence Blocks                                                                                                                                                      |

| 2.3 | Function<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.4              | on Blocks2-21Structure of Function Blocks2-22Programming Function Blocks2-24Calling Function Blocks and Assigning Parameters to them2-26Special Function Blocks2-31                      |

| 2.4 | Data B<br>2.4.1<br>2.4.2<br>2.4.3                         | locks2-33Creating Data Blocks2-35Opening Data Blocks2-36Special Data Blocks2-39                                                                                                          |

| 3   | Program                                             | m Execution                                                                                                                                                                                                                                                 |

|-----|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.1 | Principle of Program Execution 3-2                  |                                                                                                                                                                                                                                                             |

| 3.2 | Program                                             | a Organization                                                                                                                                                                                                                                              |

| 3.3 | Storing                                             | Program and Data Blocks                                                                                                                                                                                                                                     |

| 3.4 | Process<br>3.4.1                                    | ing the User Program                                                                                                                                                                                                                                        |

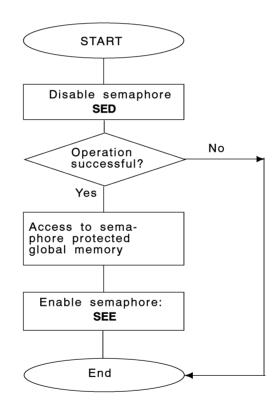

| 3.5 | STEP 5<br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4<br>3.5.5 | Operations with Examples3-13Basic Operations3-17Programming Examples in the STL, LAD and CSF Methods of Representation3-32Supplementary Operations3-47Executive Operations3-54Semaphore Operations3-67                                                      |

| 4   | Operat                                              | ing Modes and Program Processing Levels 4-1                                                                                                                                                                                                                 |

| 4.1 | Introdu                                             | ction and Overview                                                                                                                                                                                                                                          |

| 4.2 | Program                                             | n Processing Levels                                                                                                                                                                                                                                         |

| 4.3 | STOP N                                              | Mode                                                                                                                                                                                                                                                        |

|     | 4.3.1<br>4.3.2                                      | Characteristics and Indication of the Operating Mode                                                                                                                                                                                                        |

| 4.4 | RESTA<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4<br>4.4.5  | RT Mode4-15MANUAL and AUTOMATIC COLD RESTART4-16MANUAL and AUTOMATIC WARM RESTART4-16Comparison of the Different Restart Types4-18User Interfaces for Restart4-19Interruptions in the RESTART Mode4-22                                                      |

| 4.1 | RUN M                                               | Iode                                                                                                                                                                                                                                                        |

|     | 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5           | Cyclic Program Execution4-26Time-Driven Program Execution4-28CLOSED LOOP CONTROLLER INTERRUPT: Processing Closed Loop Controllers4-35PROCESS INTERRUPT: Interrupt-Driven Program Execution4-36Nested Interrupt-Driven and Time-Driven Program Execution4-39 |

| 5   | Interru                                             | pt and Error Handling 5-1                                                                                                                                                                                                                                   |

| 5.1 | Frequent Errors in the User Program 5-2             |                                                                                                                                                                                                                                                             |

| 5.2 | Error Information                                   |                                                                                                                                                                                                                                                             |

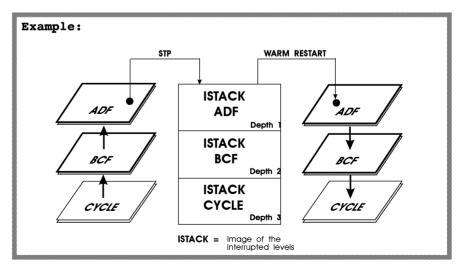

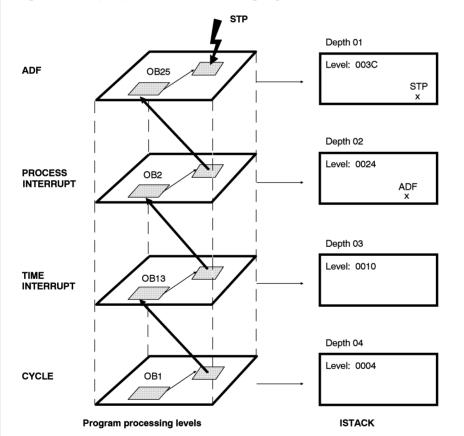

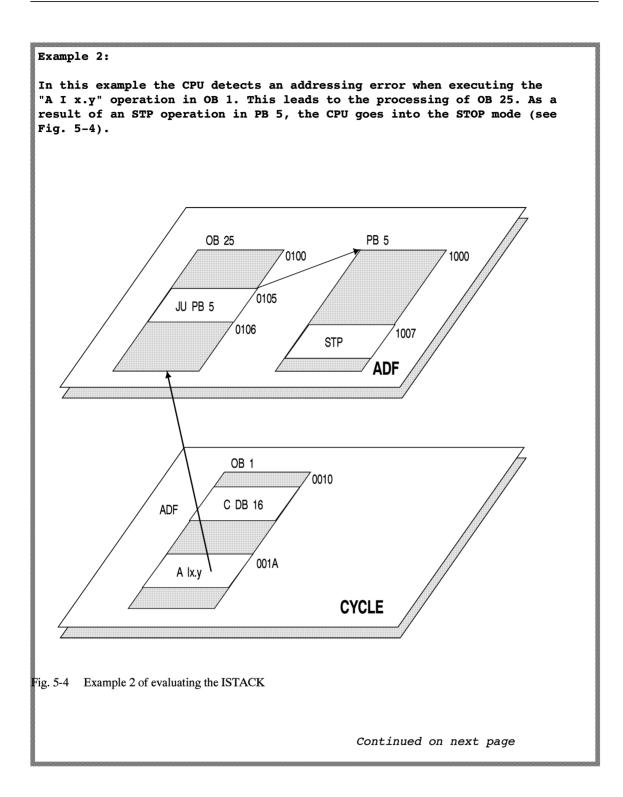

| 5.3 | Control<br>5.3.1<br>5.3.2<br>5.3.3                  | Bits and Interrupt Stack5-7Control Bits5-8ISTACK Content.5-13Example of Error Diagnosis using the ISTACK5-19                                                                                                                                                |

| 5.4 | Error H                                             | Iandling using Organization Blocks    5-22                                                                                                                                                                                                                  |

| 5.5  | Errors during RESTART 5-25                                                                                     |

|------|----------------------------------------------------------------------------------------------------------------|

|      | 5.5.1 DB0-FE (DB 0 Errors) 5-26                                                                                |

|      | 5.5.2 DB1-FE (DB 1 Errors)                                                                                     |

|      | 5.5.3 DB2-FE (DB 2 Errors)                                                                                     |

|      | 5.5.4       DX0-FE (DX 0 or DX 2 Errors)       5-29         5.5.5       MOD-FE (Memory Card Errors)       5-31 |

|      |                                                                                                                |

| 5.6  | Errors in RUN and in RESTART                                                                                   |

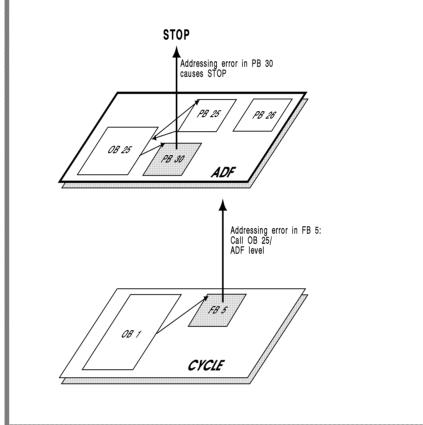

|      | 5.6.1 BCF (Operation Code Errors)                                                                              |

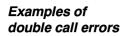

|      | 5.6.2       LZF (Runtime Errors)       5-37         5.6.3       ADF (Addressing Error)       5-45              |

|      | 5.6.3       ADF (Addressing Error)       5-45         5.6.4       QVZ (Timeout Error)       5-46               |

|      | 5.6.5 ZYK (Cycle Time Exceeded Error)                                                                          |

|      | 5.6.6 WECK-FE (Collision of Time Interrupts)                                                                   |

|      | 5.6.7 REG-FE (Controller Error) 5-50                                                                           |

|      | 5.6.8 ABBR (Abort) 5-52                                                                                        |

|      | 5.6.9 Communication Errors (FE-3) 5-53                                                                         |

| 6    | Integrated Special Functions                                                                                   |

|      | Introduction                                                                                                   |

| 6.1  |                                                                                                                |

| 6.2  | OB 110: Accessing the Condition Code Byte                                                                      |

| 6.3  | OB 111: Clear ACCUs 1, 2, 3 and 4 6-9                                                                          |

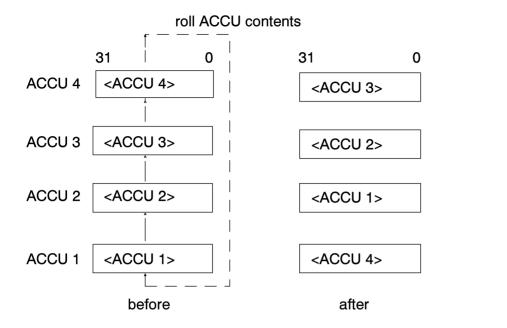

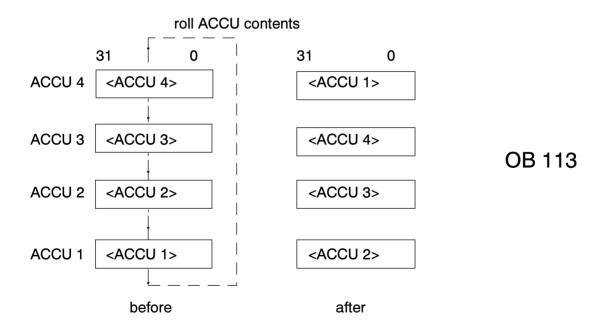

| 6.4  | OB 112/113: Roll Up ACCU and Roll Down ACCU                                                                    |

| 6.5  | OB 120: Enabling/Disabling of Interrupts 6-11                                                                  |

| 6.6  | OB 121: Enable/Disable Individual Time-Driven Interrupts                                                       |

| 6.7  | OB 122: Enable/Disable "Delay of All Interrupts"                                                               |

| 6.8  | OB 123: Enable/Disable "Delay of Individual Time-Driven Interrupts"                                            |

| 6.9  | OB 134, 135, 136 and 139 6-22                                                                                  |

| 6.10 | Setting/Reading the System Time (OB 150)                                                                       |

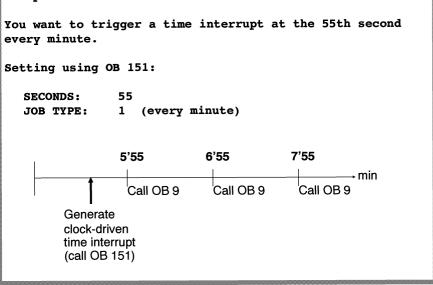

| 6.11 | OB 151: Setting/Reading the Time for Clock-Driven Interrupts                                                   |

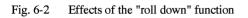

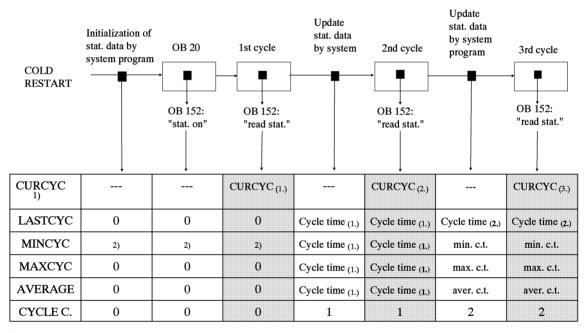

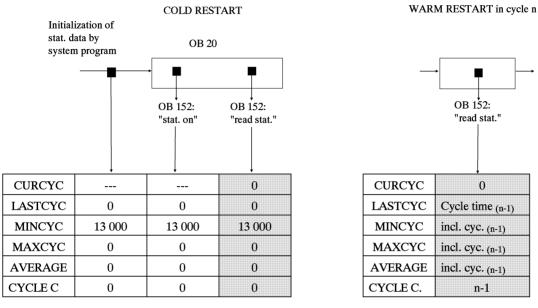

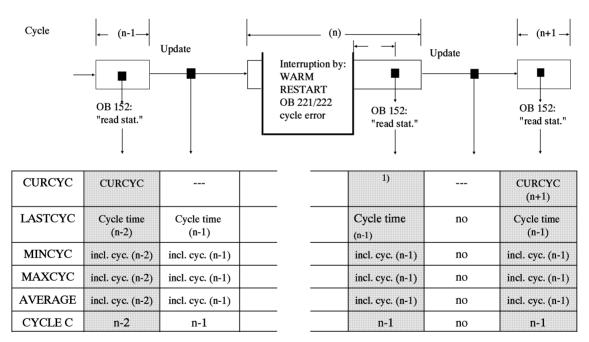

| 6.12 | OB 152: Cycle Statistics                                                                                       |

| 6.13 | OB 153: Set/Read Time for Delay Interrupt                                                                      |

| 6.14 | OB 160 to 163: Loop Counters                                                                                   |

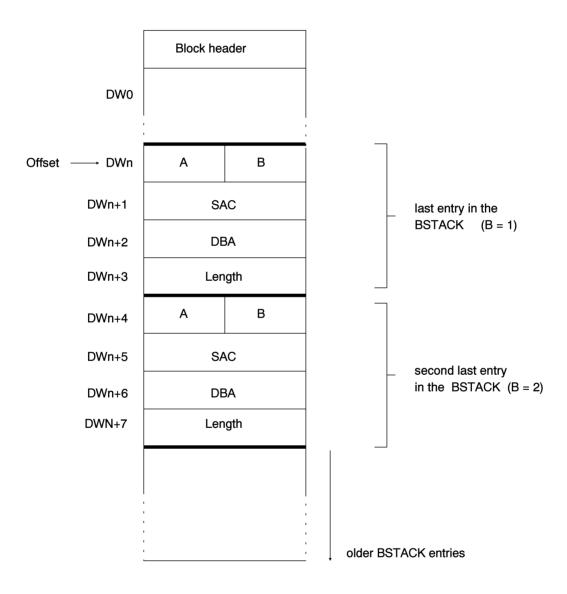

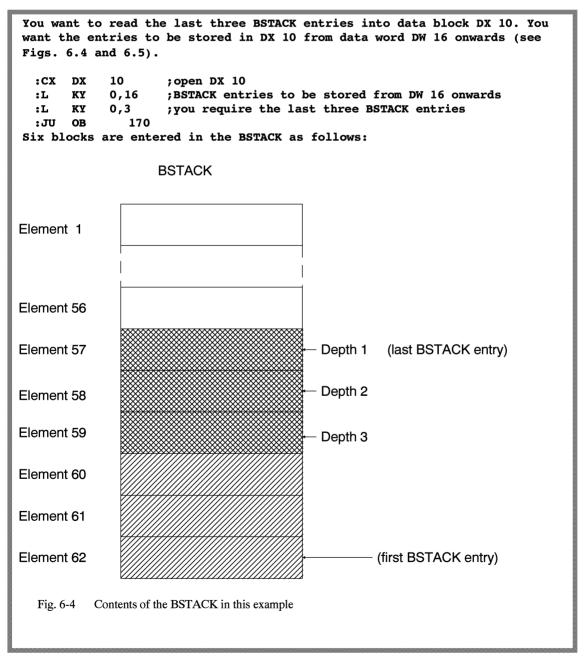

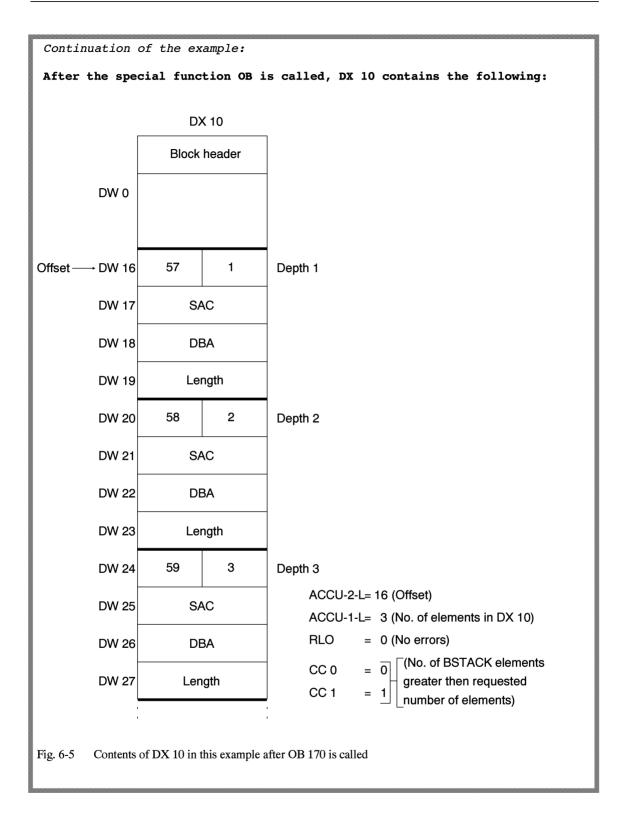

| 6.15 | OB 170: Read Block Stack (BSTACK)                                                                              |

| 6.16 | OB 180: Accessing Variable Data Blocks                                                                         |

| 6.17 | OB 181: Testing Data Blocks (DB/DX) 6-56                                                                       |

| 6.18 | OB 182: Copying a Data Area                                                                                    |

| 6.19 | OB 185: Setting Write Protection                                                                               |

| 6.20 | OB 186: Compressing Memory 6-62                                                                                |

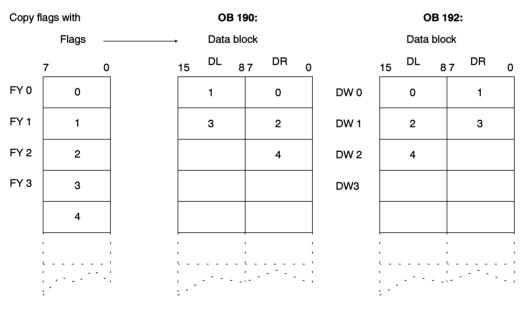

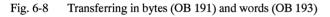

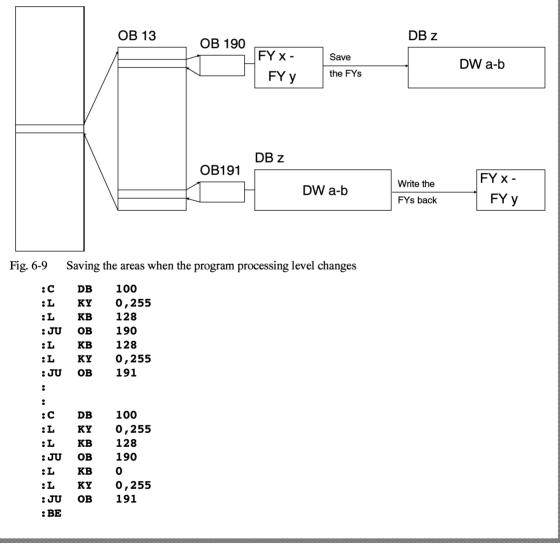

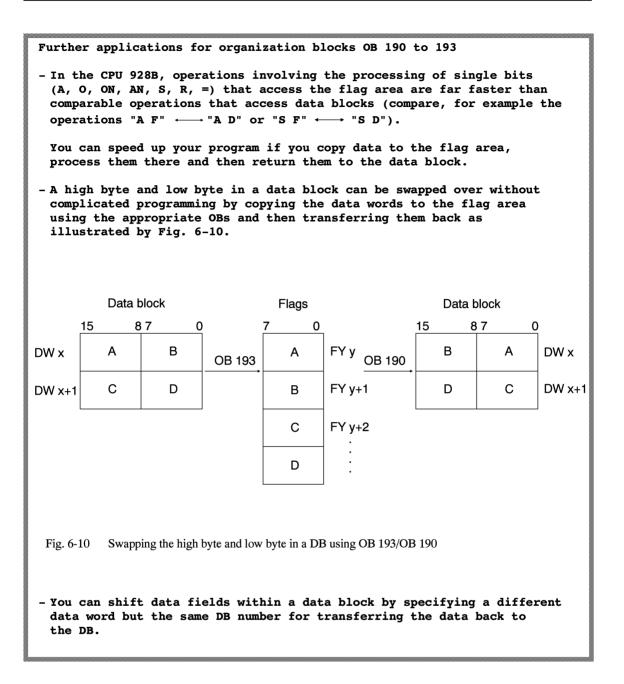

| 6.21 | OB 190/OB 192: Transferring Flags to a Data Block                                                              |

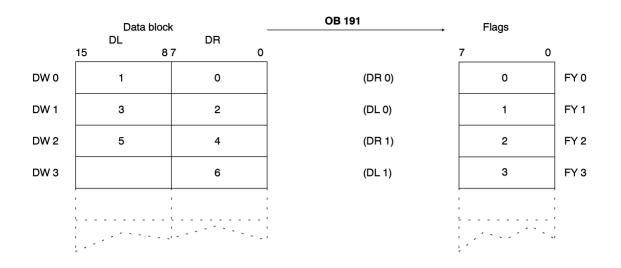

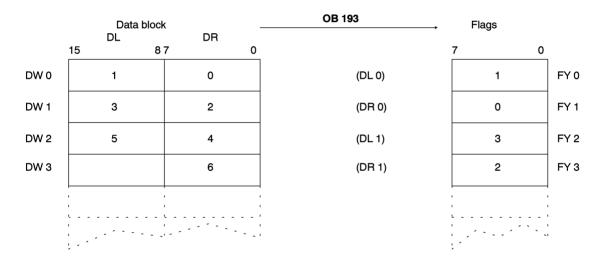

| 6.22 | OB 191/OB 193: Transferring Data Fields to a Flag Area                                                         |

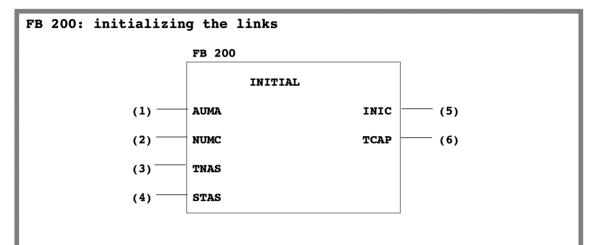

| 6.23 | OB 200 and OB 202 to 205: Multiprocessor Communication                                                         |

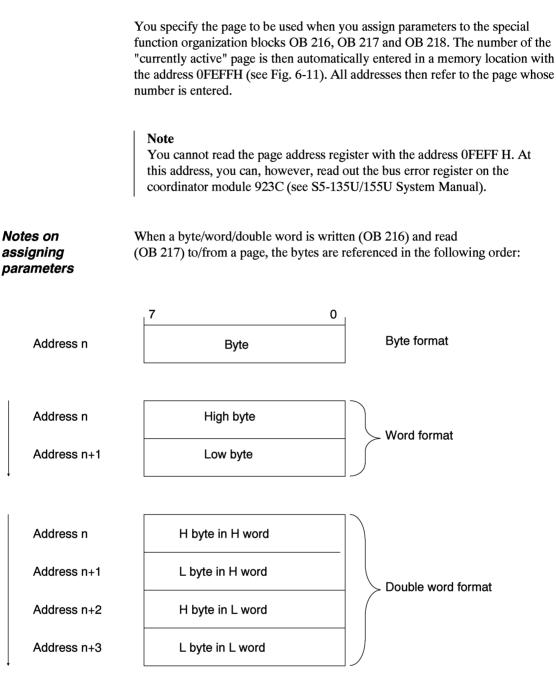

| 6.24 | OB 216 to 218: Page Access       6-71         6.24.1       OB 216: Writing to a Page       6-74         6.24.2       OB 217: Reading from a Page       6-76         6.24.3       OB 218: Reserving a Page       6-78         6.24.4       Program Example       6-80 |  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 6.25 | OB 220: Sign Extension                                                                                                                                                                                                                                               |  |

| 6.26 | OB 221: Setting the Cycle Monitoring Time                                                                                                                                                                                                                            |  |

| 6.27 | OB 222: Restarting the Cycle Monitoring Time                                                                                                                                                                                                                         |  |

| 6.28 | OB 223: Comparing Restart Types                                                                                                                                                                                                                                      |  |

| 6.29 | OB 224: Transferring Blocks of Interprocessor Communication Flags                                                                                                                                                                                                    |  |

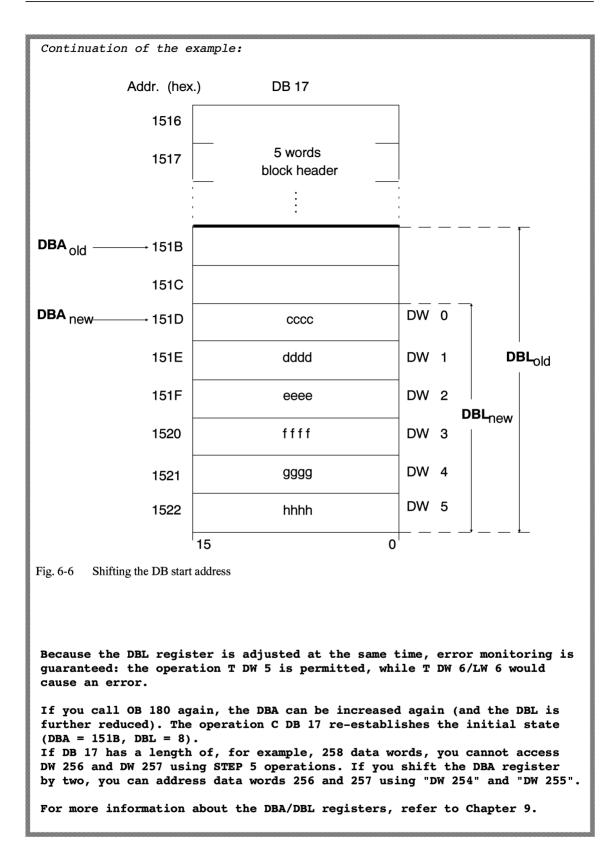

| 6.30 | OB 226, OB 227                                                                                                                                                                                                                                                       |  |

| 6.31 | OB 228: Reading Status Information of a Program Processing Level                                                                                                                                                                                                     |  |

| 6.32 | OB 230 to 237: Functions for Standard Function Blocks                                                                                                                                                                                                                |  |

| 6.33 | OB 240 to 242: Special Functions for Shift Registers                                                                                                                                                                                                                 |  |

| 6.34 | OB 240: Initializing Shift Registers                                                                                                                                                                                                                                 |  |

| 6.35 | OB 241: Processing Shift Registers                                                                                                                                                                                                                                   |  |

| 6.36 | OB 242: Deleting a Shift Register                                                                                                                                                                                                                                    |  |

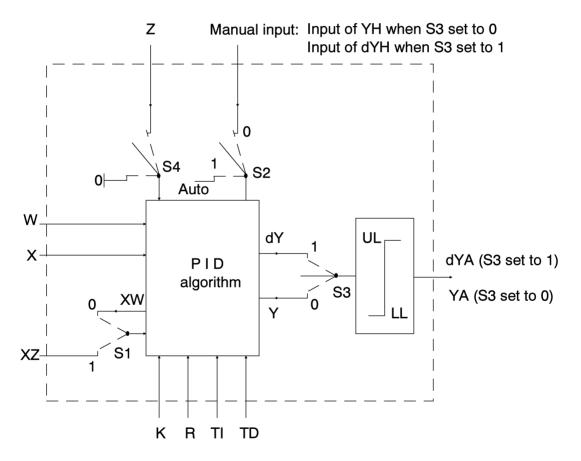

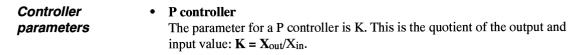

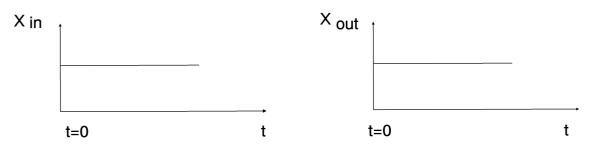

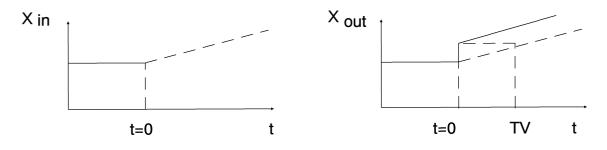

| 6.37 | OB 250/251: Closed-Loop Control/ PID Algorithm.6-996.37.1 Functional Description of the PID Controller6-996.37.2 PID Algorithm6-101                                                                                                                                  |  |

| 6.38 | OB 250: Initializing the PID Algorithm                                                                                                                                                                                                                               |  |

| 6.39 | OB 251: Processing the PID Algorithm                                                                                                                                                                                                                                 |  |

| 6.40 | OB 254, OB 255: Transferring a Data Block to the DB-RAM                                                                                                                                                                                                              |  |

| 7    | Extended Data Block DX 0 7-1                                                                                                                                                                                                                                         |  |

| 7.1  | Application 7-2                                                                                                                                                                                                                                                      |  |

| 7.2  | Structure of DX 0                                                                                                                                                                                                                                                    |  |

| 7.3  | Parameters for DX 0                                                                                                                                                                                                                                                  |  |

| 7.4  | Examples of Parameter Assignment                                                                                                                                                                                                                                     |  |

| 8    | Memory Assignment and Organization                                                                                                                                                                                                                                   |  |

| 8.1  | Structure of the Memory Area                                                                                                                                                                                                                                         |  |

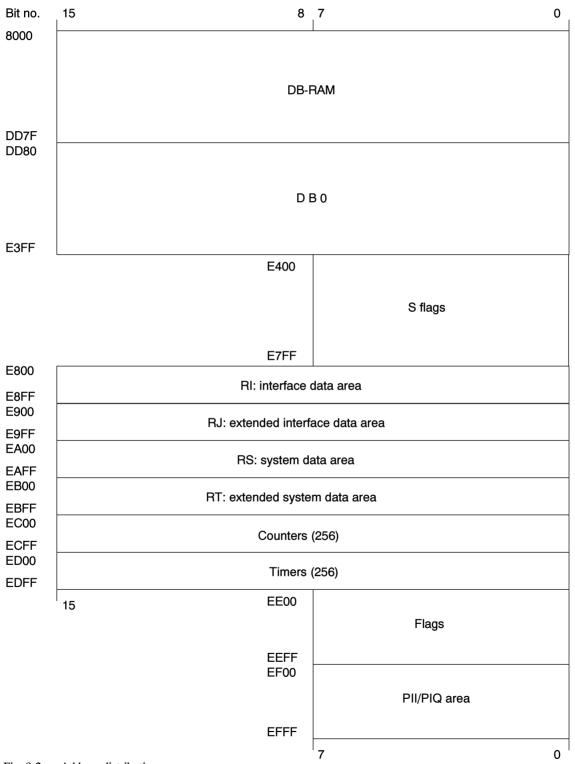

| 8.2  | Address Distribution in the CPU 928B-3UB21 8-3                                                                                                                                                                                                                       |  |

|      | 8.2.1Address Distribution.8-48.2.2Address Distribution of the Peripherals.8-5                                                                                                                                                                                        |  |

| 8.3  | User Memory Organization in the CPU 928B-3UB21                                                                                                                                                                                                                       |  |

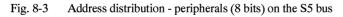

| 0.5  | 8.3.1       Block Headers in the User Memory       8-8                                                                                                                                                                                                               |  |

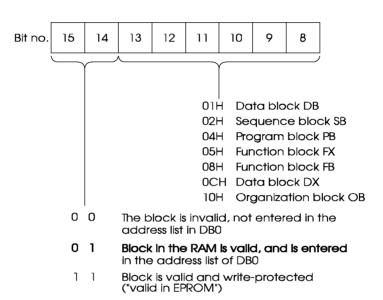

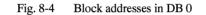

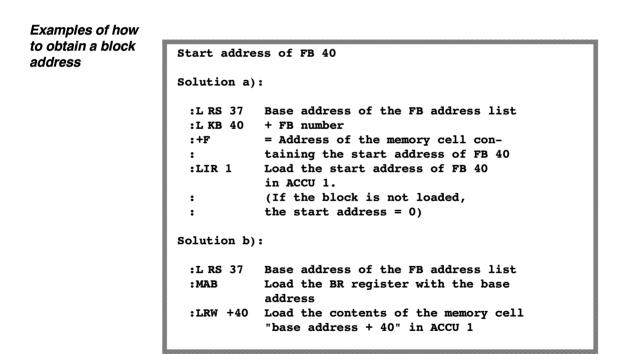

|      | 8.3.2 Block Address Lists in Data Block DB 0 8-9                                                                                                                                                                                                                     |  |

|      | 8.3.3       RI / RJ Area       8-12         8.3.4       RS / RT Area       8-13                                                                                                                                                                                      |  |

|      | 8.3.5 Bit Assignment of the System Data Words                                                                                                                                                                                                                        |  |

| 9    | Memory Access using Absolute Addresses 9-1                            |                                                                                                                                                                                      | . 9-1                                              |

|------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 9.1  | Introduction                                                          |                                                                                                                                                                                      | . 9-2                                              |

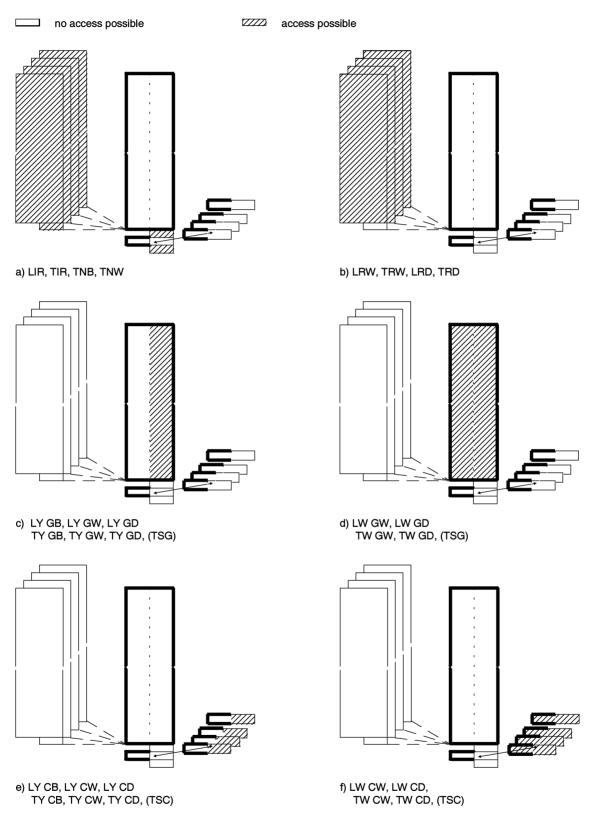

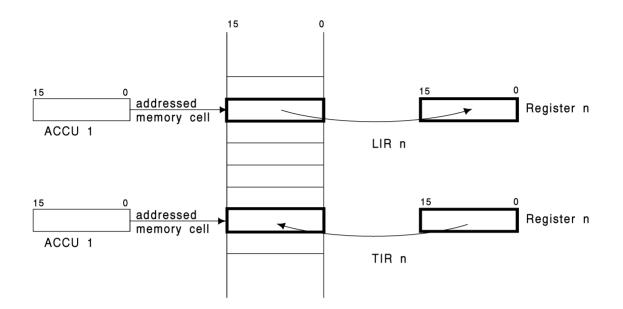

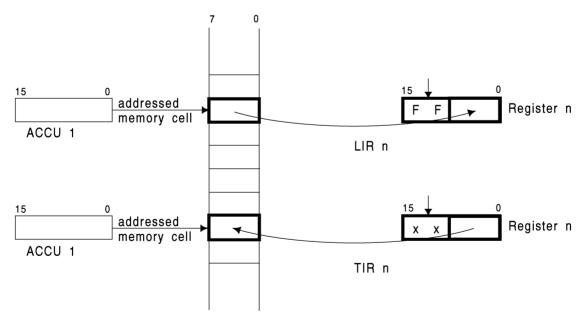

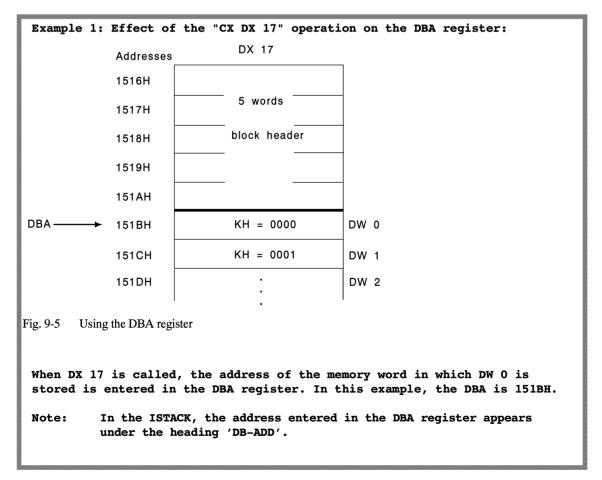

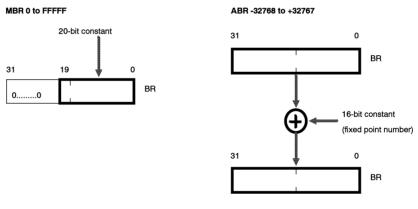

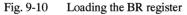

| 9.2  | 9.2.1 LI                                                              | ing the Address in ACCU 1<br>IR/TIR: Loading to or Transferring from a 16-Bit Memory Area Indirectly<br>xamples of using the Registers                                               | . 9-7                                              |

| 9.3  |                                                                       | ng Fields of Memory                                                                                                                                                                  |                                                    |

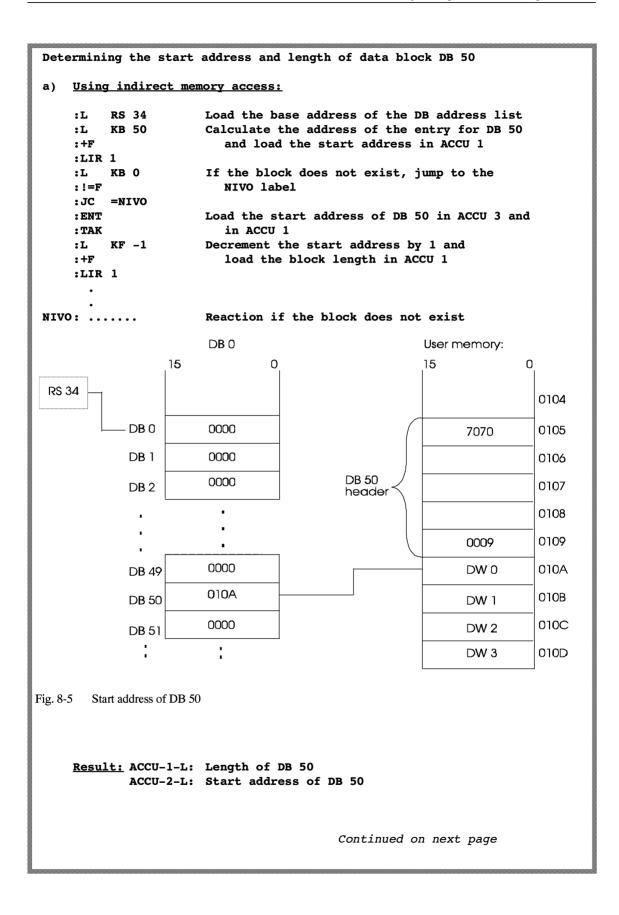

| 9.4  | 9.4.1 O<br>9.4.2 A<br>9.4.3 A                                         | s with the Base Address Register (BR Register)<br>perations for Transfer between Registers<br>accessing the Local Memory<br>accessing the Global Memory<br>accessing the Page Memory | 9-25<br>9-27<br>9-28                               |

| 10   | Multiproc                                                             | cessor Mode and Communication                                                                                                                                                        | . 10-1                                             |

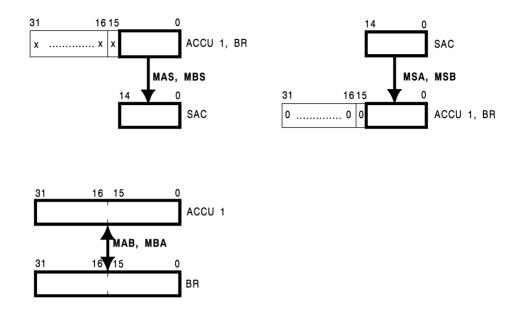

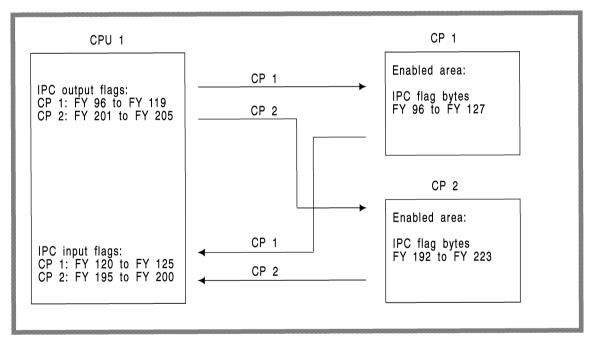

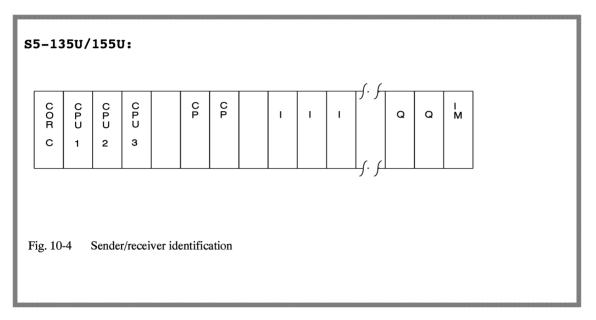

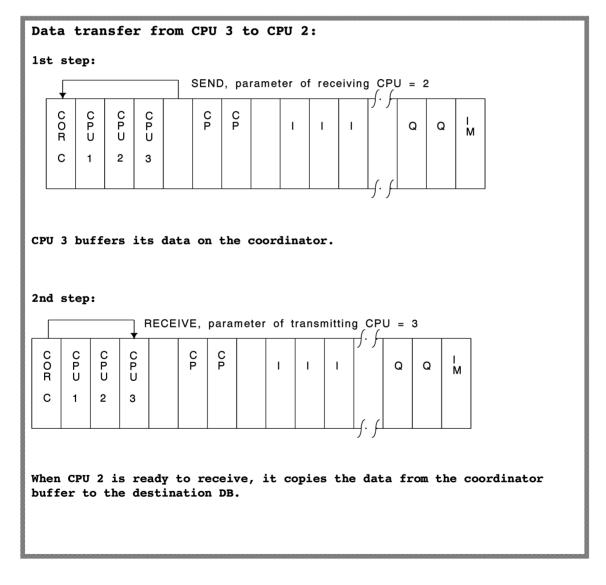

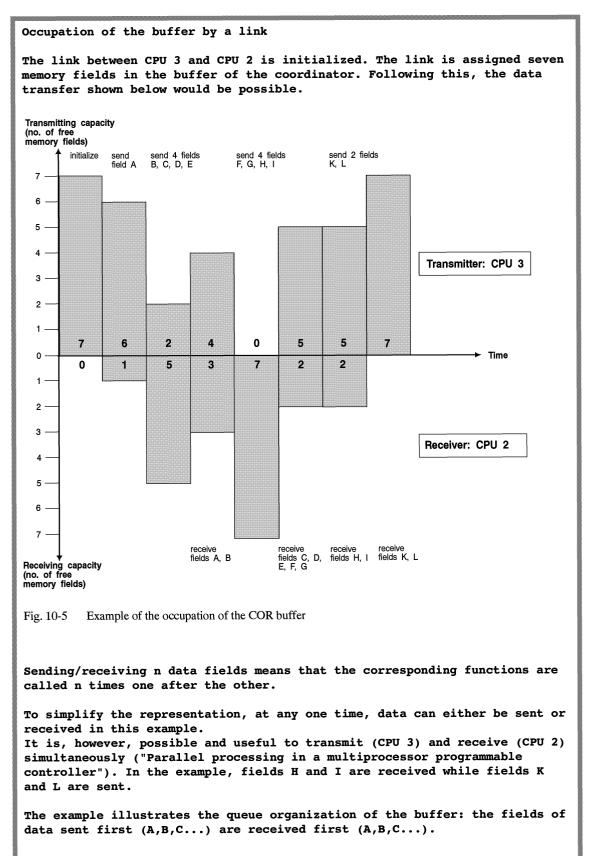

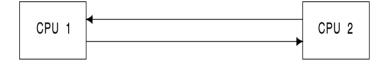

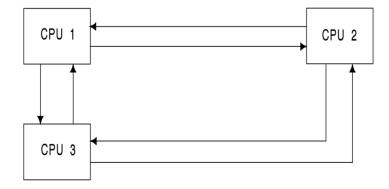

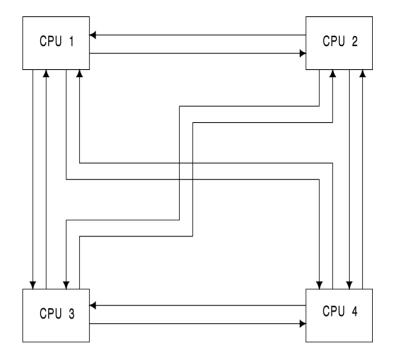

| 10.1 | 10.1.1 Ez<br>10.1.2 I/0                                               | essor Mode<br>xchanging Data via IPC Flags<br>O Flag Assignment and IPC Flag Assignment in Multiprocessor Mode (DB 1)<br>low to Create Data Block DB 1                               | . 10-4<br>. 10-8                                   |

| 10.2 | 10.2.1 H<br>10.2.2 W<br>10.2.3 H<br>10.2.4 Sy<br>10.2.5 C<br>10.2.6 H | essor Communication                                                                                                                                                                  | 10-15<br>10-16<br>10-17<br>10-20<br>10-21<br>10-22 |

| 10.3 | Runtimes                                                              | of the Communication OBs                                                                                                                                                             | 10-29                                              |

| 10.4 | 10.4.1 Fu<br>10.4.2 C<br>10.4.3 In                                    | ZE Function (OB 200)<br>unction<br>Call Parameters<br>uput Parameters<br>Dutput Parameters                                                                                           | 10-30<br>10-32<br>10-33                            |

| 10.5 | 10.5.1 Fr<br>10.5.2 C<br>10.5.3 In                                    | nction (OB 202)<br>function<br>Call Parameters<br>nput Parameters<br>Dutput Parameters                                                                                               | 10-38<br>10-39                                     |

| 10.6 | 10.6.1 Fr<br>10.6.2 C<br>10.6.3 In                                    | EST Function (OB 203)         Sunction         Call Parameters         nput Parameters         Output Parameters                                                                     | 10-43<br>10-43<br>10-43                            |

| 10.7 | 10.7.1 Fr<br>10.7.2 C<br>10.7.3 In                                    | E Function (OB 204)<br>Function<br>Call Parameters<br>nput Parameters<br>Dutput Parameters                                                                                           | 10-45<br>10-45<br>10-45                            |

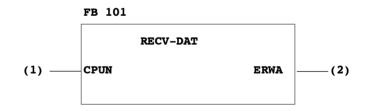

| 10.8        | RECEI<br>10.8.1<br>10.8.2<br>10.8.3<br>10.8.4                           | VE TEST Function (OB 205)       10-48         Function       10-48         Call Parameters       10-48         Input Parameters       10-48         Output Parameters       10-48 |

|-------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10.9        |                                                                         | tions                                                                                                                                                                             |

| 11          | PG Int                                                                  | erfaces and Functions 11-1                                                                                                                                                        |

| 11.1        | Overvie                                                                 | ew                                                                                                                                                                                |

| 11.2        | 11.2.1<br>11.2.2                                                        | Inctions11-3Information11-5Memory Functions and Transfer Functions11-5Program Test11-7                                                                                            |

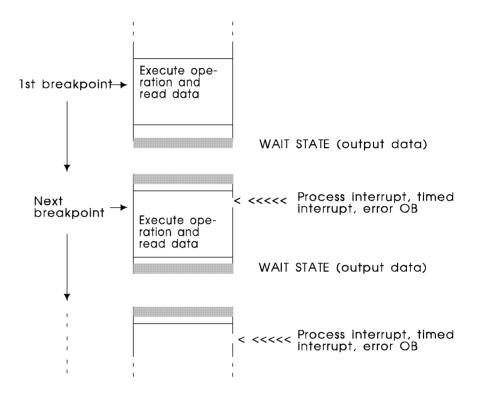

| 11.3        | Activiti                                                                | es at Checkpoints 11-15                                                                                                                                                           |

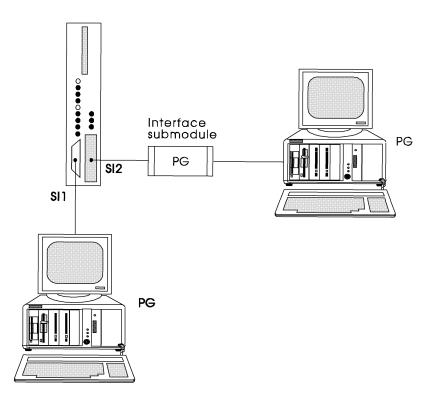

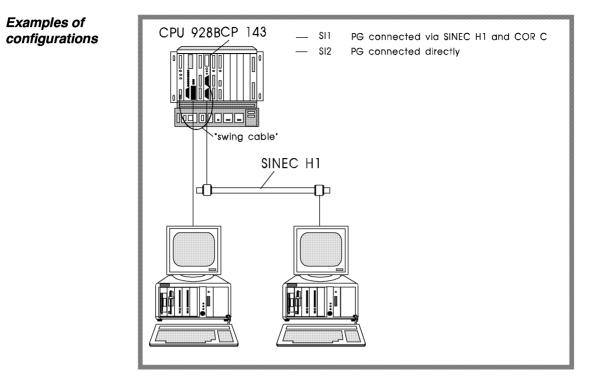

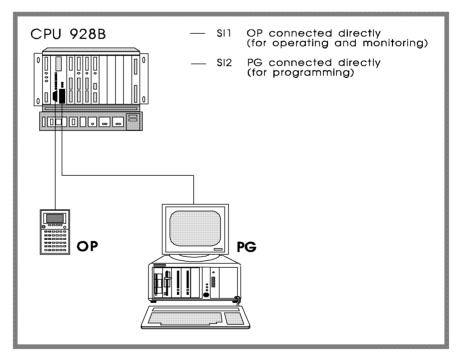

| 11.4        | Serial L                                                                | ink PG - PLC via 1st or 2nd Serial Interface 11-16                                                                                                                                |

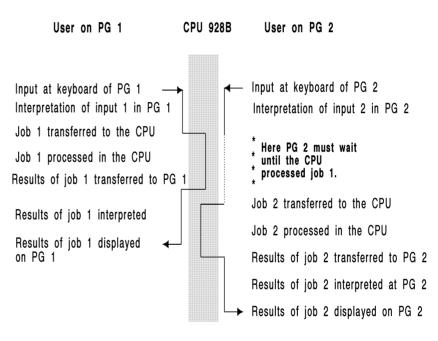

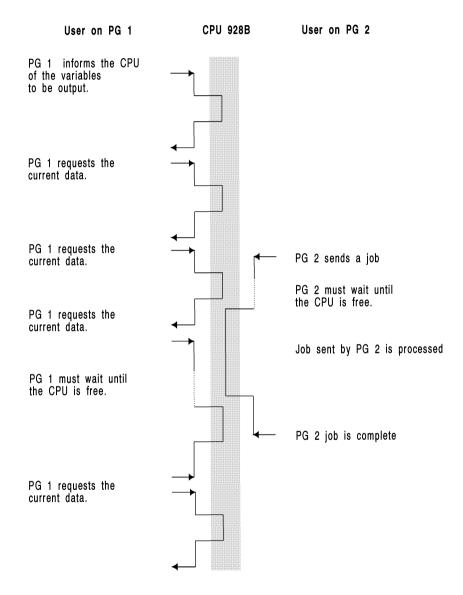

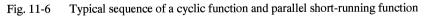

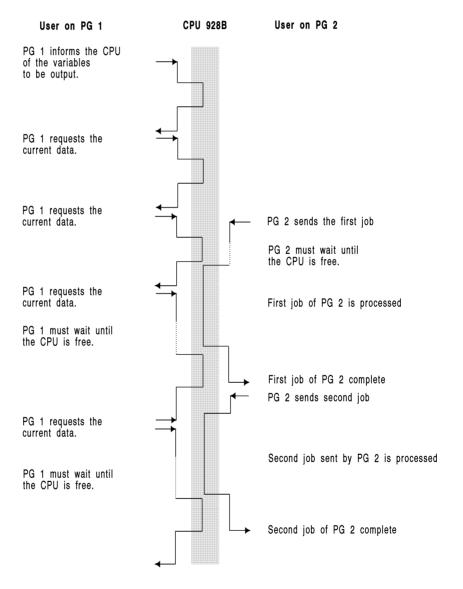

| 11.5        | Parallel<br>11.5.1<br>11.5.2<br>11.5.3                                  | Operation of Two Serial PG Interfaces11-17Installation11-19Operation11-19Sequence in Certain Operating Situations11-21                                                            |

| Α           | Append                                                                  | dix A-1                                                                                                                                                                           |

| <b>A.</b> 1 | Runtime Comparison between CPU 928-3UA21, CPU 928B-3UB21 and CPU 948A-2 |                                                                                                                                                                                   |

| A.2         | Error Identifiers                                                       |                                                                                                                                                                                   |

| A.3         | STEP 5 Operations not Contained in the CPU 928B A-12                    |                                                                                                                                                                                   |

| A.4         | Identifiers for the Program Processing Levels                           |                                                                                                                                                                                   |

| A.5         | Example "ISTACK Evaluation"                                             |                                                                                                                                                                                   |

| В           | Further reading                                                         |                                                                                                                                                                                   |

| С           | List of Abbreviations                                                   |                                                                                                                                                                                   |

# 1

### Introduction

## Contents of the chapter

This chapter explains how to use the manual and deals with the areas of application of the S5-135U programmable controller with the CPU 928B and its structure. The chapter explains the typical mode of operation of a CPU and the structure of the CPU program.

You will also find a few suggestions about how to tackle programming and will learn some of the features of the CPU 928B (-3UB21) which are important for programming.

If you have already worked with the CPU 928B (-3UB11 or -3UB12) and would like to know the differences between these modules and the CPU 928B (-3UB21), refer to Section 1.8.

## Overview of the chapter

| Section | Description                                           | Page |

|---------|-------------------------------------------------------|------|

| 1.1     | Area of Application for the S5-135U with the CPU 928B | 1-2  |

| 1.2     | Typical Mode of Operation of a CPU                    | 1-3  |

| 1.3     | The Programs in a CPU                                 | 1-5  |

| 1.3.1   | System Program                                        | 1-5  |

| 1.3.2   | User Program                                          | 1-7  |

| 1.4     | Which Operands are available to the User Program?     | 1-9  |

| 1.5     | Accessing Operand Areas and Memory Areas              | 1-12 |

| 1.6     | How to Tackle Programming?                            | 1-13 |

| 1.7     | Programming Tools                                     | 1-16 |

| 1.8     | What is New with the CPU 928B (-3UB21)?               | 1-17 |

### 1.1 Area of Application for the S5-135U with the CPU 928B

| Introduction to<br>the SIMATIC S5<br>family | The S5-135U programmable controller belongs to the family of SIMATIC S5 programmable controllers. With the CPU 928B, it is the most powerful multiprocessor unit for process automation (open and closed loop control, signalling, monitoring, logging).<br>Owing to its modularity and high performance, it can be used for medium to extremely large control systems as well as for complex automation tasks at the plant and process supervision level. |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Suitability                                 | The S5-135U with the CPU 928B is particularly suitable for the following:                                                                                                                                                                                                                                                                                                                                                                                  |

|                                             | • Tasks requiring fast bit and word-oriented processing and fast reaction times, i.e. with extremely fast open and closed loop controls.                                                                                                                                                                                                                                                                                                                   |

|                                             | Examples of this are fast processes in mechanical engineering (bottling plant, packing machines or similar systems) and in the automobile industry.                                                                                                                                                                                                                                                                                                        |

|                                             | • Tasks requiring an extremely high storage capacity and fast access times, e.g. in the automobile industry, process and plant engineering.                                                                                                                                                                                                                                                                                                                |

|                                             | • Tasks requiring fast communication with other CPUs installed in the PLC and operating in the multiprocessor mode and with CP modules (e.g. when connected to bus systems, host computers, for visualization, operation and monitoring).                                                                                                                                                                                                                  |

|                                             | • Complex tasks which can be handled efficiently and clearly using the high level languages C and SCL.                                                                                                                                                                                                                                                                                                                                                     |

#### **Typical Mode of Operation of a CPU** 1.2

Mode of The following modes of operation are possible in a CPU: operation of a CPU

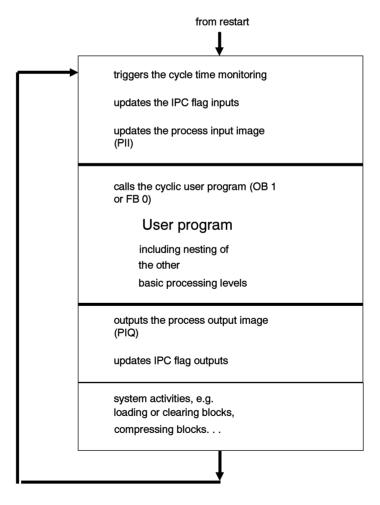

Cyclic processing

Phase

1

This is the main part of all activities in the CPU. As the name already says, the same operations are repeated in an endless cycle.

| Cyclic processing can be                                                                                                                                         | divided into three main phases             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| Sequence                                                                                                                                                         | СРИ                                        |

| All the input modules assigned to the CPU<br>are scanned by the system program and the<br>values read in are stored in the process<br>image of the inputs (PII). | Read in process image<br>of the inputs     |

| The values contained in the PII are<br>processed by the user program and the                                                                                     | Evaluate input signals, set output signals |

s, as follows:

Input I 1.4 Input I 1.5 2 ssed by the user program and the values to be output are entered in the process image of the outputs (PIQ). 1 1.3 Q 3.1 The values contained in the process image Output Q 2.0 Output process image of the outputs 3 of the outputs are output by the system Output Q 3.1 program to the output modules assigned to Output Q 4.7 the CPU.

Process

Input I 1.3

## Time-controlled processing

In addition to the cyclic processing, **time-controlled** processing is also available for processes requiring control signals at constant intervals, e.g. non-time critical monitoring functions performed every second.

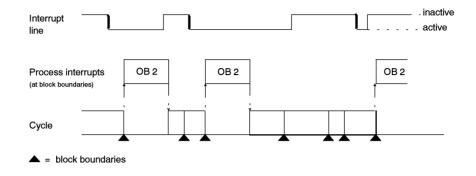

## Interrupt-driven processing

If the reaction to a particular process signal must be particularly fast, this should be handled with **interrupt-driven** processing. With, for example, a process interrupt, triggered via an interrupt generating module, you can activate a special processing section within your program.

#### Processing according to priority

$\bigcirc_{\nabla}$

The types of processing listed above are handled by the CPU according to their priority.

Since a fast reaction is required to a time or interrupt event, the CPU interrupts cyclic processing to handle a time or interrupt event. Cyclic processing therefore has the lowest priority.

#### 1.3 The Programs in a CPU

Introduction The program existing on every CPU is divided into the following:

• the system program

and

• the user program.

#### 1.3.1 System Program

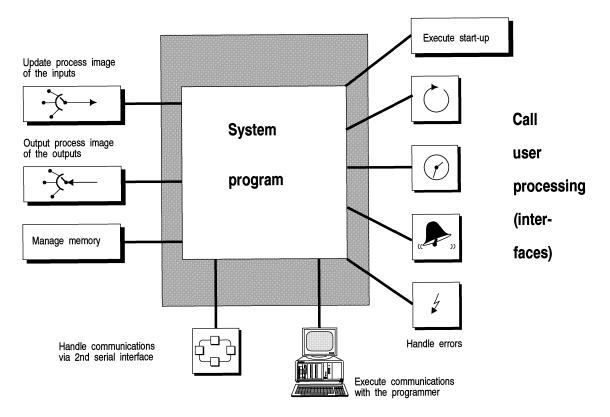

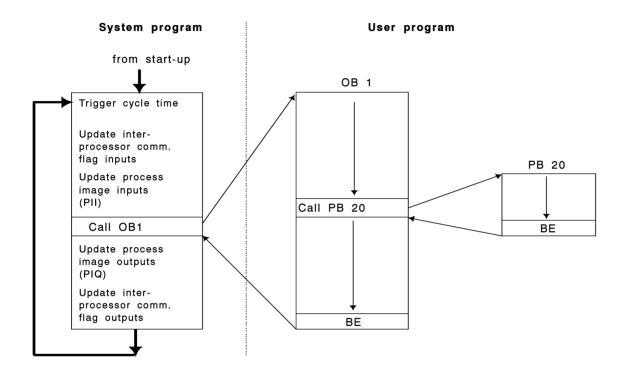

**Overview** The system program organizes all the functions and sequences of the CPU which do not involve a specific control task (refer to Fig. 1-1).

Fig. 1-1 Tasks of the system program

| Tasks                      | The tasks include the following: <sup>1)</sup>                                                                                                                                                                                                                       |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            | • cold and warm restart,                                                                                                                                                                                                                                             |

|                            | • updating the process image of the inputs and outputting the process image of the outputs,                                                                                                                                                                          |

|                            | • calling the cyclic, time-controlled and interrupt-driven programs,                                                                                                                                                                                                 |

|                            | • detection and handling of errors,                                                                                                                                                                                                                                  |

|                            | • memory management,                                                                                                                                                                                                                                                 |

|                            | • communication with the programmer (PG).                                                                                                                                                                                                                            |

|                            |                                                                                                                                                                                                                                                                      |

| User interfaces            | As the user, you can influence the reaction of the CPU to particular situations<br>and errors via special interfaces to the system program.                                                                                                                          |

| Default system<br>reaction | The following chapters, except for Chapter 7, describe the <b>default system reaction</b> to process events or errors. Depending on the defaults, the CPU changes to the stop mode if an operation code error occurs and the error organization block is not loaded. |

| Modifying the defaults     | You can modify the system response by assigning parameters for the data block DX 0.                                                                                                                                                                                  |

|                            | Chapter 7 describes the system response following modification.                                                                                                                                                                                                      |

|                            | <sup>1)</sup> When operating with several CPUs (multiprocessing) further tasks are involved.                                                                                                                                                                         |

#### 1.3.2 User Program

*Structure* Figure 1-2 shows the general structure of a STEP 5 user program.

|                                                      | User pro                                        | ogram                                                                                                                                                                                                      |                                                                                  |

|------------------------------------------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|                                                      | Code blo                                        | ocks                                                                                                                                                                                                       |                                                                                  |

| Organization<br>blocks<br>OB<br>STEP 5<br>operations | Program<br>blocks<br>PB<br>STEP 5<br>operations | Function<br>blocks<br>FB/FX<br>STEP 5<br>operations<br>FB 8<br>SEGMENT 1<br>NAME ::TRANS<br>0005 :L IB 3<br>0006 :T FW 200<br>0007 :C DB 5<br>0008 :DO FW 200<br>0009 :L DW 0<br>0000A :T QW 6<br>000B :BE | Sequence<br>blocks<br>SB<br>STEP 5<br>operations                                 |

|                                                      | Data block                                      | (S                                                                                                                                                                                                         |                                                                                  |

| DB<br>static or dynami<br>(bits, bytes, wor          |                                                 | 1:<br>2:<br>3:<br>4:<br>5:                                                                                                                                                                                 | KH = 0101;<br>KF = +120;<br>KS = xy;<br>KY = 4.5;<br>KG =<br>KM =                |

| DX<br>static or dynami<br>(bits, bytes, wor          | c data<br>ds, double words)                     | 1:<br>2:<br>3:<br>4:<br>5:<br>6:                                                                                                                                                                           | KH = FFFF;<br>KH = FFFF;<br>KH = FFFF;<br>KH = FFFF;<br>KH = FFFF;<br>KH = FFFF; |

Fig. 1-2 Structure of a STEP 5 user program

**Tasks**The user program contains all the functions required for processing a specific<br/>control task. In general terms, these functions can be assigned to the interface<br/>provided by the system program for the various types of processing, as follows:

| Type of processing          | Task                                                                                                                                                                                                                              |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cold and warm restart       | To provide the conditions under which the other<br>processing functions can start from a defined status<br>following a cold or warm restart of the control system<br>(e.g. assigning specific values to signals).                 |

| Cyclic processing           | Constantly repeated signal processing (e.g. logic<br>operations on binary signals, reading in and analyzing<br>analog values, specifying binary signals for output,<br>outputting analog values).                                 |

| Time-controlled processing  | <ul> <li>Time-dependent processing with the following time conditions:</li> <li>faster than the average cycle,</li> <li>at a time interval greater than the average cycle time,</li> <li>at a specified point in time.</li> </ul> |

| Interrupt-driven processing | Fast reactions to certain process signals.                                                                                                                                                                                        |

| Error reaction              | Handling problems within the normal sequence of the program.                                                                                                                                                                      |

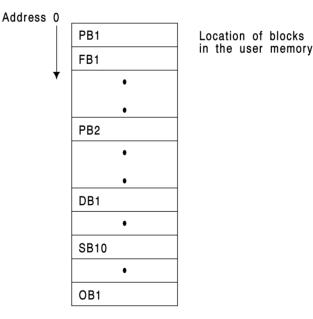

Storing the user program

The CPU 928B has two areas for storing blocks:

User memory: max. 64 Kbytes

The user memory is located on the main board (CPU).

Data block RAM (DB RAM): max. 46 Kbytes

The DB RAM makes up an additional memory area for storing data blocks and is located on the main board (CPU).

*Interfaces to the* **Organization** blocks are available as interfaces to the system program for the special types of processing.

#### 1.4 Which Operands are available to the User Program?

Overview

The CPU 928B provides the following operand areas for programming:

- process image and I/Os

- flags (F flags and S flags)

- timers/counters

- data blocks

Process image of the inputs and outputs PII/PIQ

| Characteristics                                                                                                                                             | Size                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| The user program can access the following data types in the process<br>image extremely quickly:<br>- single bits,<br>- bytes,<br>- words,<br>- double words | 128 bytes<br>each for<br>inputs and<br>outputs |

#### I/O area (P area)

| Characteristics                                                      | Size                  |

|----------------------------------------------------------------------|-----------------------|

| The user program can access the I/O modules directly via the S5 bus. | 256 bytes<br>each for |

| The following data types are possible:<br>- bytes,<br>- words.       | inputs and<br>outputs |

#### Extended I/O area (O area)

| Characteristics                                                                                                            | Size                                           |

|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| The user program can access the I/O modules directly via the S5 bus.<br>The following data types are possible:<br>- bytes, | 256 bytes<br>each for<br>inputs and<br>outputs |

| - words.                                                                                                                   | 1                                              |

#### F flags

| Characteristics                                                                                                                                                            | Size                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| The flag area is a memory area which the user program can access<br>extremely quickly with certain operations.                                                             | 2048 bits<br>(256 bytes) |

| The flag area should be used ideally for working data required often.                                                                                                      |                          |

| The following data types can be accessed:<br>- single bits,<br>- bytes,<br>- words,<br>- double words.                                                                     |                          |

| Single flag bytes can be used as <b>interprocessor communication flags</b> (IPC flags) to exchange data between the CPUs in the multiprocessor mode (refer to Chapter 10). |                          |

| IPC flags are updated by the system program at the end of the cycle via a buffer in the coordinator or CP/IP.                                                              |                          |

# S flags (extended flag area)

| Characteristics                                                                                                                                                                                                                     | Size                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| The CPU 928B also contains an additional flag area, the S flag area.<br>The user program can also access this area extremely quickly as with<br>the F flags.                                                                        | 8192 bits<br>(1024 bytes) |

| S flags <b>cannot</b> however by used as <b>actual operands</b> with function block calls nor as <b>IPC flags</b> for data exchange between the CPUs. The bit test operations of the CPU 948 can also not be used with the S flags. |                           |

| These flags can only be used with the PG system software "S5-DOS" from version 3.0 upwards or "S5-DOS/MT" from version 1.0 upwards.                                                                                                 |                           |

#### Timers (T)

| Characteristics                                                                                                                                                                                                     | Size               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| The user program loads timer cells with a time value between 10 ms and 9990 s and by means of a start operation, decrements the timer from this value at the preselected intervals until it reaches the value zero. | 256 timer<br>cells |

#### Counters (C)

| Characteristics                                                                                            | Size         |  |

|------------------------------------------------------------------------------------------------------------|--------------|--|

| The user program loads counter cells with a start value (max. 999) and then increments or decrements them. | 256 counters |  |

# Data words in the current data block

| Characteristics                                                                                                                                                                                                                                                                                                                                          | Size            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| <ul> <li>A data block contains constants and/or variables in the byte, word or double word format. With STEP 5 operations, you can always access the "current" data block (refer to Section 2.4).</li> <li>The following data types can be accessed: <ul> <li>single bits,</li> <li>bytes,</li> <li>words,</li> <li>double words.</li> </ul> </li> </ul> | 256 words<br>1) |

<sup>1)</sup> In data blocks with a length greater than 256 words, you can only access data words with the numbers > 255 with operations for absolute memory access (refer to Chapter 9) or with OB 180 (refer to Chapter 6).

### 1.5 Accessing Operand Areas and Memory Areas

| Introduction           | STEP 5 operations use two different mechanisms for accessing operand areas and the entire memory:                                                                                                                                                                                                                                                                                                                                             |  |  |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                        | • relative adressing                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|                        | • absolute addressing                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Relative<br>addressing | The majority of STEP 5 operations address a memory location relative to the beginning of the operand area. If these operations are used exclusively, code and data areas of the user program are protected against unintentional overwriting. At the same time, the user program is dependent on the CPU as long as the CPU has an appropriate operand area.                                                                                  |  |  |

| Absolute<br>addressing | Some STEP 5 operations work with absolute addresses. These operations can be used to access the entire memory area. They can only be used in function blocks and should only be used with great care due to the danger of data corruption. These operations are dependent on the CPU used.                                                                                                                                                    |  |  |

| Current data<br>block  | Data blocks are loaded into the user memory or the DB-RAM by the system<br>program. Their location depends on the memory space available in each case.<br>The lengths of the individual data blocks can vary and are set when<br>programming the data blocks.                                                                                                                                                                                 |  |  |

|                        | The current data block is the data block whose starting address and length are<br>entered in special registers. This entry is made via a special STEP 5 operation for<br>calling or "opening" a data block (like the page of book). Unless operations with<br>absolute addressing are used, the user program can only access the current data<br>block. The following data types are possible: single bits, bytes, words and double<br>words. |  |  |

### 1.6 How to Tackle Programming

| Introduction                  | If you are an experienced user, you have probably found the most suitable<br>method for creating programs for yourself and you can skip this section.                                |  |  |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                               | Less experienced readers will find tips for designing, programming, testing and starting up the STEP 5 program.                                                                      |  |  |

| Implementation<br>stages      | The implementation of the STEP 5 control program can be divided into three stages:                                                                                                   |  |  |

|                               | 1. determining the technological task                                                                                                                                                |  |  |

|                               | 2. designing the program                                                                                                                                                             |  |  |

|                               | 3. creating, testing and starting the program                                                                                                                                        |  |  |

| <i>Recursive</i><br>procedure | In practice, you will recognize that certain steps must be repeated (recursive procedure), e.g. when you realize that more signals are required to improve the handling of the task. |  |  |

| Implementation<br>stage 1     | Determining the technological task                                                                                                                                                   |  |  |

| Slaye I                       | This stage can be divided into three steps:                                                                                                                                          |  |  |

|                               | 1. creating a general block diagram outlining the control tasks of your process                                                                                                      |  |  |

|                               | 2. creating a list of the input and output signals required for the task                                                                                                             |  |  |

|                               | 3. improving the block diagram by assigning the signals and any particular time conditions and/or counter statuses to the individual blocks                                          |  |  |

| Implementation stage 2 | Designing the program                                                                                                                                                                         |

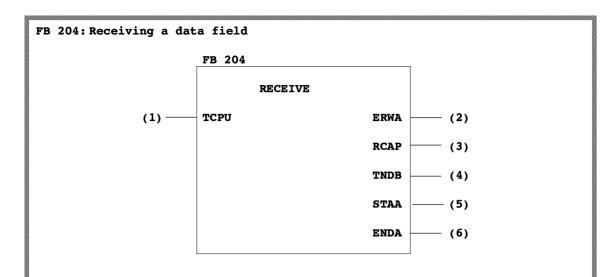

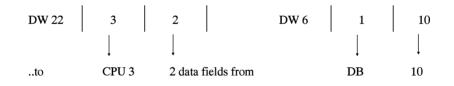

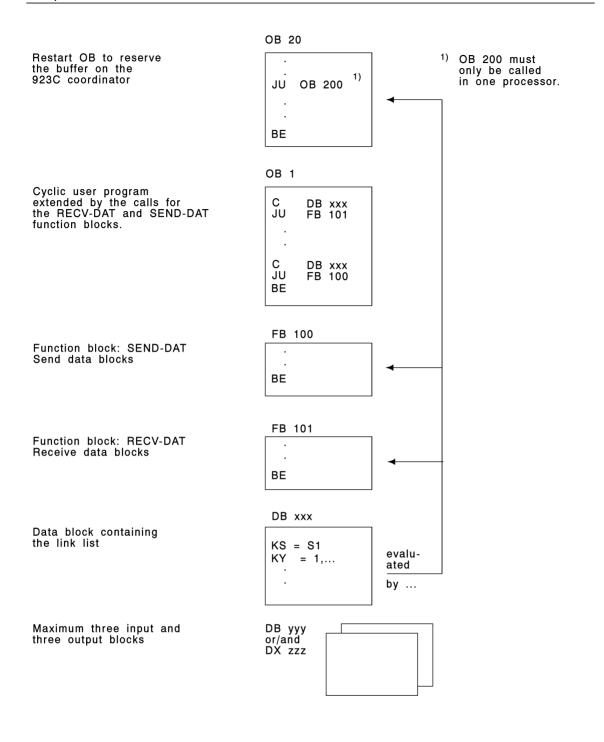

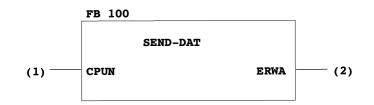

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|