# **ERTEC 200**

Enhanced Real-Time Ethernet Controller

# **PHY Description**

#### Edition (11/2007)

#### Disclaimer of Liability

We have checked the contents of this manual for agreement with the hardware and software described. Since deviations cannot be precluded entirely, we cannot guarantee full agreement. However, the data in this manual are reviewed regularly. Necessary corrections are included in subsequent editions. Suggestions for improvement are welcomed.

#### Copyright

© Siemens AG 2007. All rights reserved

The reproduction, transmission or use of this document or its contents is not permitted without express written authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved.

All product and system names are registered trademarks of their respective owner and must be treated as such.

Technical data subject to change.

# Preface

#### Target Audience of this Manual

This manual is intended for hardware developers who want to use the ERTEC 200 for new products. It describes the internal ERTEC PHY's.

This manual will be updated as required. You can find the current version of the manual on the Internet at http://www.siemens.com/comdec.

#### Guide

To help you quickly find the information you need, this manual contains the following aids:

- A complete table of contents as well as a list of all figures and tables in the manual are provided at the 0 beginning of the manual.

- A glossary containing definitions of important terms used in the manual is located following the appendices. 0

- References to other documents are indicated by the document reference number enclosed in slashes (/No./). 0 The complete title of the document can be obtained from the list of references at the end of the manual.

#### Additional Support

If you have questions regarding use of the described block that are not addressed in the documentation, please contact your Siemens representative.

Please send your written questions, comments, and suggestions regarding the manual to the hotline via the email address indicated above.

In addition, you can receive general information, current product information, FAQs, and downloads pertaining to your application on the Internet at:

http://www.siemens.com/comdec

#### **Technical Contacts for Germany / Worldwide**

| Siemens AG                                    | Phone: 0911/750-2736                                                     |  |

|-----------------------------------------------|--------------------------------------------------------------------------|--|

| Automation &<br>Drives                        | Phone: 0911/750-2080<br>Fax: 0911/750-2100<br>E-mail: ComDeC@siemens.com |  |

| ComDeC                                        |                                                                          |  |

| Street address:                               | Mailing address:                                                         |  |

| Würzburgerstr.121                             | P.O. Box 2355                                                            |  |

| 90766 Fürth<br>Federal Republic of<br>Germany | 90713 Fürth<br>Federal Republic of Germany                               |  |

| ical Contacts for USA                         |                                                                          |  |

Techni

**PROFI Interface Center: One Internet Plaza** PO Box 4991 Johnson City, TN 37602-4991 Fax: (423)- 262- 2103 Phone: (423)- 262- 2576 E-mail: profibus.sea@siemens.com

## Contents

| M | lultiport | Ethernet PHY's for ERTEC200                                | 6  |

|---|-----------|------------------------------------------------------------|----|

|   | 1.1 Intro | duction                                                    | 6  |

|   | 1.2 PHY   | Interface Pin Functions                                    | 7  |

|   |           | ctional Description                                        |    |

|   | 1.3.1     | 10BASE-T Operation                                         | 8  |

|   | 1.3.2     | 100BASE-TX Operation                                       |    |

|   | 1.3.3     | 100BASE-FX Operation                                       | 13 |

|   | 1.3.4     | Auto Negotiation                                           |    |

|   | 1.3.5     | Miscellaneous Functions                                    |    |

|   |           | Related Interfaces                                         |    |

|   | 1.5 PHY   | Register Description                                       | 25 |

|   | 1.5.1     | Basic Control Register                                     |    |

|   | 1.5.2     | Basic Status Register                                      |    |

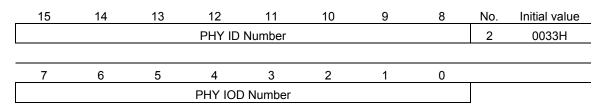

|   | 1.5.3     | PHY Identifier Register REG2OUIIN                          |    |

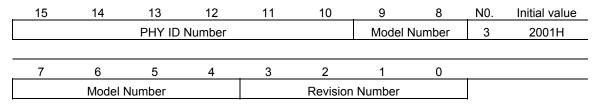

|   | 1.5.4     | PHY Identifier Register REG3OUIIN                          |    |

|   | 1.5.5     | Auto Negotiation Advertisment Register                     | 33 |

|   | 1.5.6     | Auto Negotiation Link Partner Ability Register – Base Page | 35 |

|   | 1.5.7     | Auto Negotiation Link Partner Ability Register – Next Page | 38 |

|   | 1.5.8     | Auto Negotiation Expansion Register                        |    |

|   | 1.5.9     | Auto Negotiation Next Page Transmit Register               |    |

|   | 1.5.10    | Silicon Revision Register                                  |    |

|   | 1.5.11    | Mode Control/Status Register                               |    |

|   | 1.5.12    | Special Mode Register                                      |    |

|   | 1.5.13    | Special Conrol/Status Indication Register                  |    |

|   | 1.5.14    | Interrupt Source Flag Register                             |    |

|   | 1.5.15    | Interrupt Mask Register                                    |    |

|   |           | PHY Special Control/Status Register                        |    |

|   |           | rd Design Recommendations                                  |    |

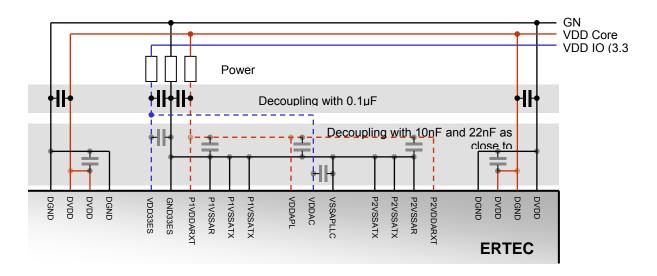

|   | 1.6.1     | Supply Voltage Circuitry                                   |    |

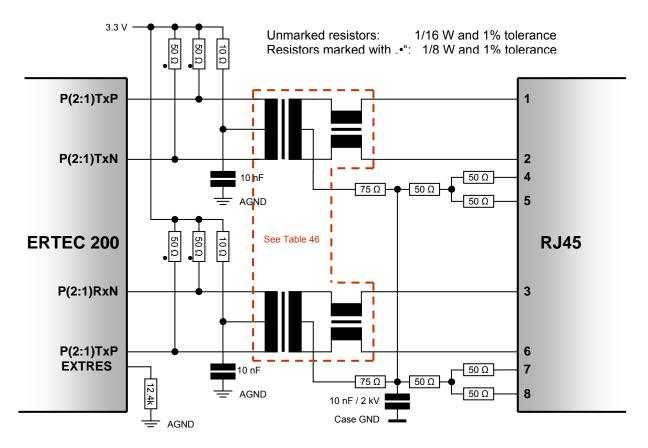

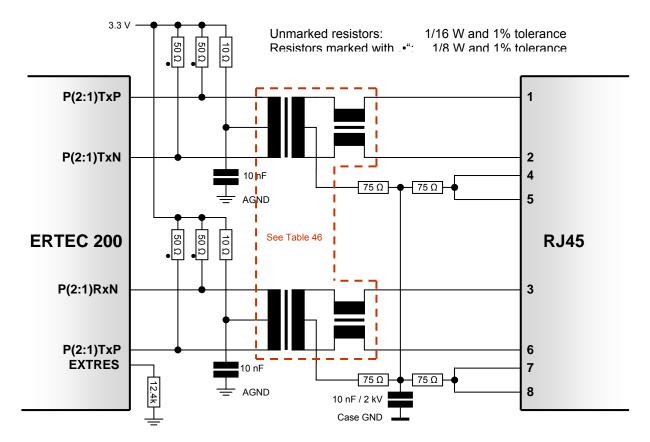

|   | 1.6.2     | 10BASE-T and 100BASE-TX Mode Circuitry                     |    |

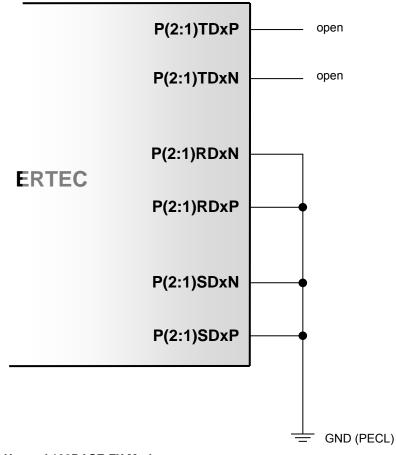

| _ | 1.6.3     | 100BASE-FX Circuitry                                       |    |

| 2 |           | cellaneous                                                 |    |

|   | 2.1 Refe  | erences:                                                   | 57 |

## List of Figures

| Figure 1: PHY Block Diagram                                   | 8 |

|---------------------------------------------------------------|---|

| Figure 2: MLT-3 Encoding Example                              |   |

| Figure 3: Internal and Remote Loopback Modes                  |   |

| Figure 4: Phase Offset Indicator Function                     |   |

| Figure 5: PHY Related Interfaces                              |   |

| Figure 6: Decoupling Capacitor Usage                          |   |

| Figure 7: 10BASE-T and 100BASE-TX Interface Circuit Example 1 |   |

| Figure 8: 10BASE-T and 100BASE-TX Interface Circuit Example 2 |   |

| Figure 9: Circuit for Unused 100BASE-FX Mode                  |   |

| Figure 10: 100BASE-FX Interface Example                       |   |

## List of Tables

| Table 1: ERTEC 200 Pin function for PHY interface                                | 7  |

|----------------------------------------------------------------------------------|----|

| Table 2: 4B/5B Code Table                                                        | 11 |

| Table 3: Assignment of LED Signals to GPIO Pins                                  | 16 |

| Table 4: PHY Interrupt Events.                                                   | 20 |

| Table 5: MII (Diagnosis) Interface Signals                                       | 23 |

| Table 6: SMI (Diagnosis) Interface Signals                                       | 23 |

| Table 7: MDI Interface Signals                                                   |    |

| Table 8: Other PHY Related Signals                                               | 25 |

| Table 9: PHY internal Registers                                                  | 25 |

| Table 10: Initial Parameter Settings for PHYs                                    | 26 |

| Table 11: Basic Control Register Overview                                        |    |

| Table 12: Basic Control Register Description                                     |    |

| Table 13: Basic Status Register Overview                                         | 29 |

| Table 14: Basic Status Register Description                                      | 31 |

| Table 15: NEC OUI Composition                                                    | 31 |

| Table 16: PHY ID Number Composition                                              |    |

| Table 17: PHY Identifier Register REG2OUIIN Overview                             | 32 |

| Table 18: PHY Identifier Register REG2OUIIN Description                          |    |

| Table 19: PHY Identifier Register REG3OUIIN Overview                             | 32 |

| Table 20: PHY Identifier Register REG3OUIIN Description                          | 32 |

| Table 21: Auto-Negotiation Advertisement Register Overview                       | 33 |

| Table 22: Auto-Negotiation Advertisement Register Description                    |    |

| Table 23: Auto-Negotiation Link Partner Ability Register Overview – Base Page    |    |

| Table 24: Auto-Negotiation Link Partner Ability Register Description - Base Page |    |

| Table 25: Auto-Negotiation Link Partner Ability Register Overview - Next Page    |    |

| Table 26: Auto-Negotiation Link Partner Ability Register Description - Next Page | 38 |

| Table 27: Auto-Negotiation Expansion Register Overview                           |    |

| Table 28: Auto-Negotiation Expansion Register Description                        |    |

| Table 29: Auto-Negotiation Next Page Transmit Register Overview                  |    |

| Table 30: Auto-Negotiation Next Page Transmit Register Description               |    |

| Table 31: Silicon Revision Register Overview                                     | 42 |

| Table 32: Silicon Revision Register Description                                  | 42 |

| Table 33: Mode Control/Status Register Overview                                  |    |

| Table 34: Mode Control/Status Register Description                               |    |

| Table 35: Special Mode Register Overview                                         | 45 |

| Table 36: Special Mode Register Description                                      | 46 |

| Table 37: Special Control/Status Indication Register Overview                    | 47 |

| Table 38: Special Control/Status Indication Register Description                 |    |

| Table 39: Interrupt Source Flag Register Overview                                | 48 |

| Table 40: Interrupt Source Flag Register Description                             | 49 |

| Table 41: Interrupt Mask Register Överview                                       | 50 |

| Table 42: Interrupt Mask Register Description                                    |    |

| Table 43: PHY Special Control/Status Register Overview                           |    |

| Table 44: PHY Special Control/Status Register Description                        |    |

| Table 45: Generation of PHY-specific Supply Voltages                             | 52 |

| Table 46: Examples for Magnetics Selection                                       | 54 |

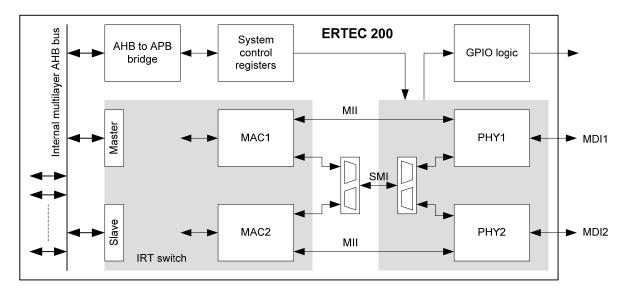

## Multiport Ethernet PHY's for ERTEC200

## 1.1 Introduction

ERTEC 200 has integrated a 2 channel multiport Ethernet PHY (Physical Layer Transceiver), that supports the following transmission modes:

- 10BASE-T

- 100BASE-TX

- 100BASE-FX

It can be connected to unshielded twisted-pair (UTP) cable via external magnetics or to optical fiber via fiber PMD modules. Internally on the ERTEC 200 it interfaces to the MAC layer through the IEEE 802.3 Standard Media Independent Interface (MII).

The core has a DSP-based architecture for signal equalization and baseline wander correction. This helps to achieve high noise immunity and to extend UTP cable lengths. The transmission modes can be configured for each port individually. Beside these basic modes, the following (configurable) features are supported as well:

- Auto-negotiation

- Auto-MDI/MDIX detection

- Auto polarity

The PHYs comply to the following standards:

- IEEE802.3

- IEEE802.3u

- ANSI X3.263-1995

- ISO/IEC9314

Communication between the integrated PHYs and the integrated Ethernet MACs is realized with onchip MII interfaces. Internal registers of the PHYs can be accessed via the common (on-chip) serial management interface (SMI). Furthermore certain set-ups for the PHYs can be programmed using the system control registers that are described in **\1\ Chapter 4.8**. A couple of output signals per channel is available to reflect the connection status via LEDs; these signals are shared with GPIO pins. The PHYs need a 25 MHz clock that can be provided on two alternative ways:

- connect a 25 MHz quartz to the CLKP\_A and CLKP\_B pins

- connect a 25 MHz oscillator to the CLKP\_A pin.

In order to reduce power consumption, the PHYs can be driven to a power down mode either manually or automatically, if there is no activity on the Ethernet line.

## 1.2 PHY Interface Pin Functions

| Pin Name          | I/O | Function                                       | Number of pins |

|-------------------|-----|------------------------------------------------|----------------|

| P(2:1)TxN         | 0   | Differential transmit data output              | 2              |

| P(2:1)TxP         | 0   | Differential transmit data output              | 2              |

| P(2:1)TDxN        | 0   | Differential FX transmit data output           | 2              |

| P(2:1)TDxP        | 0   | Differential FX transmit data output           | 2              |

| P(2:1)RxN         | I   | Differential receive data input                | 2              |

| P(2:1)RxP         | I   | Differential receive data input                | 2              |

| P(2:1)RDxN        | I   | Differential FX receive data input             | 2              |

| P(2:1)RDxP        | I   | Differential FX receive data input             | 2              |

| P(2:1)SDxN        | I   | Differential FX signal detect input            | 2              |

| P(2:1)SDxP        | I   | Differential FX signal detect input            | 2              |

| EXTRES            | I/O | External reference resistor (12.4 k $\Omega$ ) | 1              |

| DVDD(4:1)         | I   | Digital power supply, 1.5 V                    | 4              |

| DGND(4:1)         | I   | Digital GND                                    | 4              |

| P(2:1)VSSATX(2:1) | I   | Analog port GND                                | 4              |

| P(2:1)VDDARXTX    | I   | Analog port RX/TX power supply, 1.5 V          | 2              |

| P(2:1)VSSARX      | I   | Analog port GND                                | 2              |

| VDDAPLL           | I   | Analog central power supply, 1.5 V             | 1              |

| VDDACB            | I   | Analog central power supply, 3.3 V             | 1              |

| VSSAPLLCB         | 1   | Analog central GND                             | 1              |

| VDD33ESD          | I   | Analog test power supply, 3.3 V                | 1              |

| VSS33ESD          | I   | Analog test GND                                | 1              |

| total             |     |                                                | 42             |

The on-chip PHYs of ERTEC 200 use the following pins:

#### Table 1: ERTEC 200 Pin function for PHY interface

Note that Table 1 includes the specific power supply pins that are needed for operation of the PHYs, however it does not include the status indication signals that are shared with GPIO pins. For the status indication signals see /1/

## 1.3 Functional Description

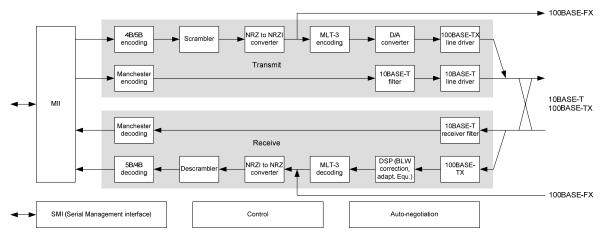

This chapter gives a functional description of the integrated PHYs on ERTEC 200 based on the block diagram shown in **Figure 1**. **Figure 1** shows a single channel; both channels have identical structure. The subsequent chapters will frequently refer to signals that are present on the MII interface between on-chip PHY and on-chip MAC. In these cases the signal names that have been introduced in **\1\Table 1.5.7 and 1.5.8** will be used. Note that these signals can be externally monitored when ERTEC 200 has been configured to MII diagnosis mode with the CONFIG(6:1) pins.

Figure 1: PHY Block Diagram

## 1.3.1 10BASE-T Operation

A 10BASE-T transceiver is implemented for a 10 Mbps CSMA/CD LAN over two pairs of twisted-pair wires according to the specifications given in clause 14 of the IEEE 802.3 standard. During transmission, 4-bit nibble data comes from the MII interface at a rate of 2.5 MHz and is converted into a 10 Mbps serial data stream. The data stream is then Manchester-encoded and sent to the analog transmitter which drives a signal to the twisted pair cable via external magnetics.

In order to comply with legacy 10BASE-T MAC/Controllers, the transmitted data is looped back to the receive path, if the PHY is configured to work in half-duplex mode.

On the receiver side, the receive clock is recovered from the incoming signal. The received Manchester-encoded analog signal from the cable is recovered to the NRZI data stream using the clock. Then the 10 Mbps serial data stream is again converted to 4-bit data that are passed to the MAC across the MII interface at a rate of 2.5 MHz. The PHY realizes a complete 10BASE-T transceiver function. It includes the receiver, transmitter and the following functions.

- <1> Filter and squelch

- <2> Jabber detection

- <3> Signal quality error (SQE) message test function

- <4> Timing recovery from received data

- <5> Manchester encoding/decoding

- <6> Full-duplex or Half-duplex mode In half-duplex mode, the PHY transmits and simultaneously receives in order to provide loopback of the transmitted signal. (Refer to section 14.2.1.3 of IEEE802.3)

- <7> Collision presence function (half duplex mode only)

- <8> Carrier Sense Detection CRS is asserted only to receive activity for Full-Duplex mode. CRS is asserted during either packet transmission or reception for half-duplex mode.

## (1) Filter and Squelch

The Manchester encoded signal from the cable is fed into the transceiver's receive path via 1:1 ratio magnetics (see **Chapter 1.6.2** for details of the circuit). It is first filtered to reduce any out-of-band noise. It then passes through a squelch circuit - a set of amplitude and timing comparators that normally reject differential voltage levels below 300 mV and detect and recognize differential voltages above 585 mV.

## (2) Jabber detection

Jabber is a condition in which a station transmits for a period of time longer than the maximum permissible packet length - usually due to a fault condition - that results in holding the TX\_EN\_P(2:1) signal active for a long period. Special logic is used to detect the jabber state and to abort the transmission to the line within 45 ms. The maximum time of of unjab is 350 ms. Once TX\_EN\_P(2:1) is deasserted, the logic resets the jabber condition. Basic status register 1 indicates that a jabber condition was detected; details about the register functions are given in **Chapter 1.5**.

## (3) SQE test function

The PHYs on ERTEC 200 support a signal quality error (SQE) test function. This function controls if data transmission is successful; successful transmission is indicated by activating the COL\_P(2:1) signal for 1  $\mu$ s, 2  $\mu$ s after TX\_EN\_P(2:1) has been deasserted. This signal is also referred to as "heartbeat" signal.

If desired, the SQE test function can be disabled by setting the SQEOFF bit in control/status register 27 to  $1_b$ . The setting of the SQEOFF bit is irrelevant when the PHY is working in 100BASE-TX or -FX modes.

## (4) Manchester encoding/decoding

When encoding, the 4-bit nibble data, that is coming from the MII interface, is converted to a 10 Mbps serial NRZI data stream. The 10M PLL locks onto the external clock and produces a 20 MHz clock signal. which is used to Manchester encode the NRZ data stream.

When no data is being transmitted, normal link pulses (NLPs) are output to maintain communications with the remote link partner.

When decoding, the 10M PLL is locked onto the received Manchester signal and from this, the internal 20 MHz receive clock is generated. Using this clock, the Manchester encoded data is extracted and converted to a 10 MHz NRZI data stream. This stream is then converted from serial to 4-bit nibble data.

## 1.3.2 100BASE-TX Operation

100BASE-TX specifies operation over two copper media: two pairs of shielded twisted-pair cable (STP) and two pairs of unshielded twisted-pair cable (Category 5 UTP). 100BASE-TX function includes the physical coding sub-layer (PCS), the physical medium attachment (PMA) and physical medium dependent sub-layer (PMD).

When transmitting, 4-bit data nibbles come from the MII interface at a rate of 25 MHz and are converted to 5-bit encoded data. The data is then serialized and scrambled, subsequently converted to a NRZI data stream and MLT-3 encoded.

In the receive path the ADC samples the incoming MLT-3 signal at a sampling frequency of 125 MHz. The resulting MLT-3 signal is reconverted to the NRZI data stream, and then the descrambler performs the inverse function of the scrambler in the transmit path and parallelizes the data. The 4B/5B decoder completes the processing and supplies the data ready for transmission over the MII interface.

This section describes the main functions of the 100BASE-TX portion of the PHYs.

- <1> Full-duplex or Half-duplex mode

- <2> Collision detect indication

- <3> Carrier Sense detection

- <4> MLT-3 to (from) NRZ Decoding/Encoding

- <5> 4B/5B Encoding/Decoding

- <6> Scrambler/Descrambler

- <7> Adaptive Equalization(DSP)

- <8> Baseline Wander Correction

- <9> Timing recovery from received data

- <10> Support MII, RMII and Symbol interface

## (1) Timing recovery

The 125M PLL locks onto the 25 MHz reference clock and generates an internal 125 MHz clock used to drive the 125 MHz logic and the 100BASE-TX transmitter. The PLL generates multiple phases of the 125 MHz clock. A multiplexer, controlled by the timing unit of the DSP block, selects the optimum phase for sampling the data. This is used as the recovered receive clock, which is then used to extract the serial data from the received signal.

#### (2) Adaptive equalizer

The adaptive equalizer compensates phase and amplitude distortion caused by the physical transmission channel consisting of magnetics, connectors, and CAT-5 cable. Thus, the supported cable length is increased.

#### (3) Baseline wander correction

If the DC content of the signal is such that the low-frequency components fall below the low frequency pole of the isolation transformer, then the droop characteristics of the transformer will become significant and baseline wander (BLW) on the received signal will result. To prevent corruption of the received data, the PHY corrects the baseline wander effects using DSP algorithms.

#### (4) 4B/5B encoding/decoding

In 100BASE-TX mode, 4B/5B coding is used. The 4B/5B encoder converts 4-bit nibbles coming from the MII interface to 5-bit symbols that are referred to as "code-groups". The relation between original and encoded data is shown in Table 2.

For testing purposes the encoder and decoder can be bypassed with the Enable 4B5B bit in the PHY special control/status register. In this case the 5th bit of the output pattern reflects the current level of the TX\_ERR\_P(2:1) signal of the MII interface.

| Code group | Name | Transmitter                                                                                                                           |                  | Receiver                                                                                                                                        |                |  |

|------------|------|---------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|

|            |      | from MAC via MII Interpretation                                                                                                       |                  | Interpretation                                                                                                                                  | to MAC via MII |  |

| 11110      | 0    | 0000 Data 0                                                                                                                           |                  | Data 0                                                                                                                                          | 0000           |  |

| 01001      | 1    | 0001 Data 1                                                                                                                           |                  | Data 1                                                                                                                                          | 0001           |  |

| 10100      | 2    | 0010                                                                                                                                  | Data 2           | Data 2                                                                                                                                          | 0010           |  |

| 10101      | 3    | 0011                                                                                                                                  | Data 3           | Data 3                                                                                                                                          | 0011           |  |

| 01010      | 4    | 0100                                                                                                                                  | Data 4           | Data 4                                                                                                                                          | 0100           |  |

| 01011      | 5    | 0101                                                                                                                                  | Data 5           | Data 5                                                                                                                                          | 0101           |  |

| 01110      | 6    | 0110                                                                                                                                  | Data 6           | Data 6                                                                                                                                          | 0110           |  |

| 01111      | 7    | 0111                                                                                                                                  | Data 7           | Data 7                                                                                                                                          | 0111           |  |

| 10010      | 8    | 1000                                                                                                                                  | Data 8           | Data 8                                                                                                                                          | 1000           |  |

| 10011      | 9    | 1001                                                                                                                                  | Data 9           | Data 9                                                                                                                                          | 1001           |  |

| 10110      | Α    | 1010                                                                                                                                  | Data A           | Data A                                                                                                                                          | 1010           |  |

| 10111      | В    | 1011                                                                                                                                  | Data B           | Data B                                                                                                                                          | 1011           |  |

| 11010      | С    | 1100                                                                                                                                  | Data C           | Data C                                                                                                                                          | 1100           |  |

| 11011      | D    | 1101                                                                                                                                  | Data D           | Data D                                                                                                                                          | 1101           |  |

| 11100      | E    | 1110                                                                                                                                  | Data E           | Data E                                                                                                                                          | 1110           |  |

| 11101      | F    | 1111                                                                                                                                  | Data F           | Data F                                                                                                                                          | 1111           |  |

| 11111      | I    | Sent after /T and /<br>until TX_EN_P(<br>aga                                                                                          | 2:1) is asserted | ld                                                                                                                                              | le             |  |

| 11000      | J    | Sent, when TX<br>asse                                                                                                                 | ` '              | 1 <sup>st</sup> nibble of start of stream data<br>(SSD); translates to 0101 if<br>received after "idle"; otherwise<br>RX_ERR_P(2:1) is asserted |                |  |

| 10001      | к    | Sent a                                                                                                                                | fter /J          | 2 <sup>nd</sup> nibble of SSD; translates to<br>0101 if received after /J; otherwise<br>RX_ERR_P(2:1) is asserted                               |                |  |

| 01101      | Т    | Sent when TX_E                                                                                                                        | — • /            | 1 <sup>st</sup> nibble of end of stream data<br>(ESD): translates to 1010 and                                                                   |                |  |

| 00111      | R    | 2 <sup>st</sup> nibble of ESD; tran<br>1010 and causes deas<br>Sent after /T<br>CRS_P(2:1) when prec<br>otherwise RX_ERR_<br>asserted |                  | D; translates to<br>s deassertion of<br>n preceded by /T;<br>ERR_P(2:1) is                                                                      |                |  |

| 00100      | н    | Sent when TX_ERR_P(2:1) is<br>asserted                                                                                                |                  | Transmit error                                                                                                                                  | Undefined      |  |

| all others | V    | Invalid code Invalid code; RX_ERR_P(2:1)<br>Invalid code Asserted if received while<br>RX_DV_P(2:1) is active                         |                  |                                                                                                                                                 | ceived while   |  |

Table 2: 4B/5B Code Table

## (5) Scrambling/Descrambling

Scrambling the data before transmission helps to eliminate large narrow-band signal power peaks for repeated data patterns, and spreads the signal power more uniformly over the entire channel band-width.

The scrambler encodes a plaintext NRZ bit stream by addition (modulo 2) of 2047 bits generated by the recursive linear function X[n]=X[n-11] + X[n-9] (modulo 2). The scrambler generates the specified non-zero key stream whenever the active output interface is required to transmit a scrambled data stream. The seed for the scrambler is generated from the PHY address, ensuring that in multiple-PHY applications each PHY will have its individual scrambler sequence.

The descrambler descrambles the NRZ ciphertext bit stream coming from the MLT-3 decoder by addition (modulo 2) of a key stream to re-produce a plaintext bit stream. During the reception of IDLE symbols, the descrambler synchronizes its descrambler key to the incoming stream. Once synchronization is achieved, the descrambler locks on this key and is able to descramble incoming data.

Special logic in the descrambler ensures synchronization with the remote PHY by searching for IDLE symbols within a window of 4000 bytes (40us). This window ensures that a maximum packet size of 1514 bytes, allowed by the IEEE 802.3 standard, can be received with no interference.

This core has a scrambler and descrambler bypass mode for testing purposes.

## (6) MLT3 Encoding/Decoding

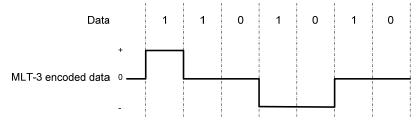

In the transmit direction, the serial 125 MHz NRZI data stream is encoded to MLT-3. MLT-3 is a trilevel code where a change in the logic level represents a code bit "1" and the logic output remaining at the same level represents a code bit "0".

In the receive direction, the MLT-3 code is converted to an NRZI data stream. The NRZI to MLT-3 conversion is illustrated in **Figure 2**.

Figure 2: MLT-3 Encoding Example

## (7) Receive Data Valid / Receive Error

The receive data valid signal RX\_DV\_P(2:1) indicates that recovered and decoded nibbles are being presented on the RXD\_P1(3:0) respectively RXD\_P2(3:0) outputs synchronous to RX\_CLK\_P(2:1). RX\_DV\_P(2:1) becomes active after the /J/K/ delimiter has been recognized and RXD\_P(2:1) is aligned to nibble boundaries. It remains active until either the /T/R/ delimiter is recognized or link test indicates failure.

RXDV is asserted when the first nibble of translated /J/K/ is ready for transfer over the Media Independent Interface (MII).

During a frame, unexpected code-groups are considered as receive errors. Expected code groups are the data set (0H through FH), and the /T/R/(ESD) symbol pair. When a receive error occurs, the RX\_ERR\_P(2:1) signal is asserted and arbitrary data is driven onto the RXD lines. Should an error be detected during the time that the /J/K/ delimiter is being decoded (bad SSD error), RX\_ERR(2:1) is asserted true and the value  $1110_b$  is driven onto the RXD\_P(2:1) lines. Note that the valid vata signal is not yet asserted when the bad SSD error occurs.

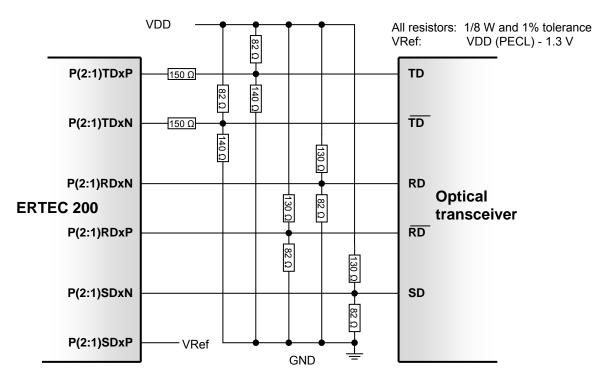

## 1.3.3 100BASE-FX Operation

This section describes main functions within the PHY in 100BASE-FX operation.

- <1> NRZI to(from) NRZ converter

- <2> Far End Fault Indication

- <3> Timing recovery from received data

- <4> Support MII,RMII, SMII and Symbol interface

The 100BASE-FX shares logic with 100BASE-TX; the differences between 100BASE-FX mode and 100BASE-TX mode are following,

- <1> Transmit output/receive input is not scrambled or MLT3 encoded.

- <2> All analog circuits except for the PLL are powered-down.

- <3> Auto-Negotiation is disabled.

- <4> The transmit data is output to a FX transmitter.

- <5> The receive data is input to the FX ECL level detector instead of the equalizer.

- <6> The FX interface has a signal detect input.

## (1) Signal Detect

The signal detect signals P(2:1)SDxP/N are input signals to the PHY from the PMD FX transceiver. Assertion of P(2:1)SDxP/N indicates a valid FX signal on the fiber. When SD is deactivated, the LINK goes down and no data is sent to the controller.

## (2) Far End Fault indication

Far End fault indication (FEFI) is a mechanism used to communicate physical status across a fiber link. Each PHY monitors the status of its receive link using the Signal Detect input. If the PHY detects a problem with its receive link, it communicates that to its link partner using the FEFI mechanism.

FEFI consists of a modification to the IDLE code patterns. In this mode, every 16 IDLE code groups are followed by a data-0 code group. If the PHY detects a FEFI pattern in its receive stream, it deasserts its link status and transmits only IDLE patterns (not FEFI) on its transmit stream.

A full description of the Far End Fault Function is given in Section 24.3.2.1 in the IEEE 802.3 standard.

## 1.3.4 Auto Negotiation

The objective of the Auto-Negotiation function is to provide the means to exchange information between two devices that share a link segment and to automatically configure both devices to take maximum advantage of their abilities.

The auto-negotiation protocol is a purely physical layer activity and proceeds independently of the MAC controller. The auto-negotiation function sends fast link pulse (FLP) bursts for exchanging information with its link partner. A FLP burst consists of 33 pulse positions. The 17 odd-numbered pulse positions shall contain a link pulse and represent clock information. The 16 even-numbered pulse positions represent data information. The data transmitted by an FLP burst is known as a "Link Code Word". These are fully defined in clause 28 of the IEEE 802.3 specification.

This core supports auto-negotiation and implements the "Base page", defined by IEEE 802.3. It also supports the optional "Next page" function to get the remote fault number code.

#### (1) Parallel detection

The parallel detection function allows detection of Link Partners that support 100BASE-TX and/or 10BASE-T, but do not support Auto-Negotiation. The PHY is able to determine the speed of the link based on either 100M MLT-3 symbols or 10M Normal Link Pulses. If the PHY detects either mode, it automatically reverts to the corresponding operating mode. In this case the link is presumed to be half duplex.

If a link is established via parallel detection, then Bit 0 of the Auto-Negotiation Expansion register is cleared to indicate that the link partner is not capable of auto-negotiation. The controller has access to this information via the management interface. If a fault occurs during parallel detection, bit 4 of the Auto-Negotiation Expansion register is set.

The Auto-Negotiation Link Partner Ability register is used to store the link partner ability information, which is coded in the received FLPs. If the link partner is not auto-negotiation capable, then the Auto-Negotiation Link Partner Ability register is updated after completion of parallel detection to reflect the speed capabilities of the link partner.

## (2) Re-negotiation

Auto-negotiation is started by one of the following events:

- <1> H/W reset

- <2> S/W reset

- <3> setting the Auto-Negotiation Enable bit in the Basic Control register from low to high

When auto-negotiation is enabled, it is re-started by one of the following events:

- <1> Link status is down.

- <2> Setting the Auto-Negotiation Restart bit in the Basic Control register to high.

## (3) Priority Resolution

If two Ethernet communication partners negotiate their capabilities, there are four possible matches of the technology abilities. In the order of priority these are:

- 100M full Duplex (highest priority)

- 100M Half Duplex

- 10M full Duplex

- 10M Half Duplex (lowest priority)

Since two devices (local device and remote device) may have multiple abilities in common, a prioritization scheme exists to ensure that the highest common denominator ability is chosen. Full duplex solutions are always higher in priority than their half duplex counterparts. 10BASE-T is the lowest common denominator and therefore has the lowest priority.

If a link is formed via parallel detection, then the Link Partner Auto-negotiation Able bit in the Auto Negotiation Expansion register is cleared to indicate that the link partner is not capable of autonegotiation. The controller has access to this information via the management interface. If a fault occurs during parallel detection, the Parallel Detection Fault bit in the same register is set. The Auto-Negotiation Link Partner Ability register 5 is used to store the link partner's ability information, which was decoded from the received FLPs. If the link partner is not auto-negotiation capable, then the Auto-Negotiation Link Partner Ability register is updated after completion of parallel detection to reflect the speed capability of the link partner.

## (4) Next Page function

Additional information, exceeding that required by base page exchange, is also sent via "Next Pages"; this PHY supports the optional "Next page" function. Next page exchange occurs after the base page has been exchanged. Next page exchange consists of using the normal Auto-Negotiation arbitration process to send next page messages. Two kinds of message encodings are defined: Message Pages, which contain predefined 11 bit codes, and unformatted pages.

Next page transmission ends when both ends of a link segment set their Next Page bits to logic zero, indicating that neither has anything additional to transmit. It is possible for one device to have more pages to transmit than the other device. Once a device has completed transmission of its next page information, it shall transmit message pages with Null message codes and the NP bit set to logic zero while its link partner continues to transmit valid next pages.

Devices, that are able of auto-negotiation, shall recognize reception of message pages with Null message codes as the end of its link partner's next page information. The default value of the next page support is disable (Next Page bit in Auto-Negotiation Advertisement register). To enable next page support, the Next Page bit should be set to  $1_b$ . Auto-Negotiation should be restarted and the message code to be transmitted to the remote link partner should be written to bit(10:0) of the Auto-Negotiation Next Page Transmit register .

## (5) Disabling Auto-Negotiation

Auto-negotiation can be disabled by setting the Auto-Negotiation Enable bit in the Basic Control register. When Auto-negotiation is disabled, the speed and duplex mode settings are configured via the serial management interface.

#### 1.3.5 Miscellaneous Functions

This chapter summarizes some additional functions of the PHYs.

## (1) LED indicators

Six LED signals are provided per PHY. These provide a convenient means to determine the operation mode of the PHYs. All LED signals are active low. The LED signals are made available through the GPIO pins of the ERTEC 200. The functions of the LED signals are as follows:

• 100BASE-TX/FX status

This signal shows, that operation speed is 100Mbps or during Auto-Negotiation; this signal will go inactive when the operating speed is 10Mbps or during line isolation.

• 10BASE-T status

This signal shows, that operation speed is 10Mbps; this signal will go inactive when the operating speed is 100Mbps or during line isolation.

Link status

This signal shows, that the PHY detects a valid link. The use of the 10Mbps or 100Mbps link test status is determined by the condition of the internally determined speed selection.

• Full/Half Duplex

This signal shows, whether the established link is operating in full or half duplex mode; it is active in full duplex mode.

Transmit Activity

This signal shows, that CRS\_P(2:1) is active (high) at transmit. When CRS becomes inactive, the transmit activity LED output is extended by 128ms in order to improve visibility.

Receive Activity

This signal shows, that CRS\_P(2:1) is active (high) at receive. When CRS becomes inactive, the receive activity LED output is extended by 128ms in order to improve visibility. In loopback mode, this LED is not active.

Table 3 illustrates how the LED signals are made available at the GPIO pins.

| CPIO nin | Function                  |                  |                 |  |  |  |  |

|----------|---------------------------|------------------|-----------------|--|--|--|--|

| GPIO pin | 1                         | 2                | 3               |  |  |  |  |

| GPIO0    | P1-DUPLEX-LED_N           | -                | -               |  |  |  |  |

| GPIO1    | P2-DUPLEX-LED_N           | -                | -               |  |  |  |  |

| GPIO2    | P1-SPEED-100LED_N (TX/FX) | P1-SPEED-10LED_N | -               |  |  |  |  |

| GPIO3    | P2-SPEED-100LED_N (TX/FX) | P2-SPEED-10LED_N | -               |  |  |  |  |

| GPIO4    | P1-LINK-LED_N             | -                | -               |  |  |  |  |

| GPIO5    | P2-LINK-LED_N             | -                | -               |  |  |  |  |

| GPIO6    | P1-RX-LED_N               | P1-TX-LED_N      | P1-ACTIVE-LED_N |  |  |  |  |

| GPIO7    | P2-RX-LED_N               | P2-TX-LED_N      | P2-ACTIVE-LED_N |  |  |  |  |

Table 3: Assignment of LED Signals to GPIO Pins

## (2) MDI/MDI-X crossover detection

The PHYs automatically detect and correct MDI/MDI-X crossover. This function can be disabled by setting the AutoMDIX\_en bit in the Mode Control/Status register to  $0_b$ . When it is disabled, crossover must be corrected manually by setting the MDI mode bit in the same register accordingly.

## (3) Polarity

This core automatically detects and corrects polarity reversal in wiring in 10BASE-T mode. The result of polarity detection is indicated by the XPOL bit in the Special Control/Status Indications register. Polarity is checked at end of packets in 10BASE-T. When a packet is corrupted by noise, the PHY may mis-interprete information inside the packet as end of packet. In this case, the PHY may invert the polarity and a maximum of three packets is be needed to detect the valid polarity again.

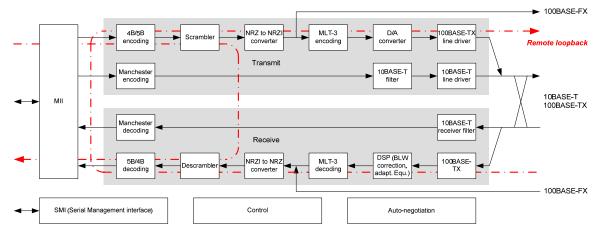

## (4) Loopback mode

This ERTEC 200 PHYs support two loopback modes: internal loopback and remote loopback. **Figure 3** illustrates the differences between these two modes.

Figure 3: Internal and Remote Loopback Modes

## (a) Internal loopback

This loopback mode is defined in the IEEE 802.3 specification; it is enabled by setting the Loopback bit in the Basic Control register to  $1_b$ . In this mode, the scrambled transmit data is looped into the receive logic. The COL\_P(2:1) signal will be inactive in this mode, unless the Collision Test bit in the Basic control register is active.

When the internal loopback mode is active, the receive circuitry should be isolated from the network medium. In this mode, the assertion of TX\_EN\_P(2:1) at the MII interface does not result in the transmission of data on the network medium, and transmitters are powered down.

## (b) Remote loopback

This mode is enabled by setting the FARLOOP BACK bit in the Mode Control/Status register to  $1_b$ . This mode can be used only when the PHYs are in 100BASE-TX or 100BASE-FX mode. In this mode, packets that arrive at the receiver are looped back out to the transmitter. In 100BASE-TX mode, the data path includes the ADC, DSP, PCS circuits; in 100BASE-FX mode, the data path includes the PECL logic, clock recovery and PCS logic. As long as no data is received, IDLE symbols are transmitted.

In this mode, the complete preamble, SFD and EFD are re-generated by the PHY so that always complete packets are transmitted, even if received packets lack part of the preamble. The Isolate bit in the Basic Control register needs to be cleared to work in remote loopback mode.

#### (5) Power Down Modes

#### (a) Hardware power down

This state is entered after a hardware reset of ERTEC 200. The PHYs are switched off and their power consumption is almost 0 W. This state is left by setting the P1/2\_PHY\_ENB bits in the PHY\_CONFIG register. All analog and digital blocks in the PHYs are initialized and the predefined configuration in the PHY\_CONFIG register is copied to the PHYs. Then, the PHY-internal registers can be configured as well.

Setting the P1/2\_PHY\_ENB bits extends the internal reset signal in the PHYs to 5.2 ms in order to stabilize the PLL and all analog and digital blocks. When the PHYs are ready to operate, this is automatically indicated in the PHY\_STATUS registers with the P1/2\_PWRUPRST bits (set to  $1_b$ ).

#### (b) Software power down

This state is entered by writing a  $1_b$  into the PowerDown bit of the Basic Control register of the PHYs. The affected PHY will then go into a low power state, where the MDIO interface is still active, but where no activity is possible on the MII interface. The power consumption of the PHYs in low power state is around 15 mW per PHY.

The low power mode is left by writing a  $0_b$  into the PowerDown bit. The digital parts of the circuitry are re-initialised, however the start-up configuration, that is stored in the PHY\_CONFIG register, is not copied again into the PHYs and the PHY registers are not set to their initial values. Leaving the low power state generates an internal reset for the PHYs with a duration of 256  $\mu$ s for PLL stabilization.

#### (c) Automatic power down

The PHYs support an automatic power down mode, that is entered, if there is no activity on the Ethernet line. To enable this mode, a  $1_b$  must be written into the EDPWRDOWN bit of the Mode Control/Status register of the PHYs. No activity on the line will then automatically drive the PHY into the low power mode with approximately 15 mW power consumption per PHY. If link pulses or data packets are detected, the low power mode is automatically left with an internal reset of 256 µs and re-initialization of the circuitry. The first and possibly the second packet may be lost during the energy detection process. No configuration data is copied from the PHY\_CONFIG register to the PHY at this point.

Automatic power down cannot be used as long as Auto-negotiation is enabled; therefore the Auto-Negotiation Enable bit in the Basic Control register must be set to  $0_b$  for automatic power down.

#### (6) Resetting the PHYs

#### (a) Hardware reset

There are two methods to issue a hardware reset to the ERTEC 200 on-chip PHYs; the reset source can be selected using the PHY\_RES\_SEL bit in the PHY\_CONFIG register:

| $PHY_RES_SEL = 0_b$          | PowerOn reset via RESET_N input resets the PHYs           |

|------------------------------|-----------------------------------------------------------|

| PHY_RES_SEL = 1 <sub>b</sub> | Internal RES_PHY_N signal from IRT switch resets the PHYs |

If the PowerOn reset is used, the PHYs are active after reset; if RES\_PHY\_N is used, the PHYs remain in power down mode after reset and must subsequently be activated with the PowerDown bit in the Basic Control register. The HW reset must be present for at least 100 µs. These reset signals are internally extended by 5.2 ms to ensure that the PHY is properly reset. All analog circuits and all digital logic including management registers are initialized. After initialization, the respective PWRUPRST signal in the PHY\_STATUS register is set.

- **Notes: 1.** During the hardware reset and its extension, the clock signal for the PHYs must be supplied.

- **2.** A hardware reset is commonly issued to both PHYs.

## (b) Software reset

Resetting the PHYs core can also be accomplished by setting the Reset bit in the respective Basic Control register to  $1_b$ . This signal is self-clearing. After the register has been written, the internal software reset is extended by 256 µs for PLL stabilization before the logic is released from reset. A software reset affects the PHY registers and resets them to their initial values except where noted.

**Note:** A software reset can be issued separately for each PHY.

## (c) Reset by software and energy detect power down

When the PHYs come out of software and energy detect power down, they are automatically activated. After exiting the power down mode, the PHY-internal power-down reset is extended by 256 µs for PLL stabilization before logic is released from reset.

**Note:** This PHY-internal power down reset does not affect the PHY management registers.

## (7) Half/Full Duplex

In half duplex mode, stations contend for the use of the physical medium, using the CSMA/CD algorithms specified. Half duplex mode is required on those media that are not capable of supporting simultaneous transmission and reception without interference like 10BASE-2 and 100BASE-T4.

The full duplex operation mode can be used when all of the following conditions are fulfilled:

- <1> The physical medium is capable of supporting simultaneous transmission and reception without interference.

- <2> There are exactly two stations on the LAN. This allows the physical medium to be treated as a full duplex point-to-point link between the stations.

- <3> Both stations on the LAN are capable of and have been configured to use full duplex operation.

## (8) Interrupt handling

Each PHY can generate a collective interrupt that can be triggered by several PHY-internal events; these two interrupts are routed with a wired-OR to the common IRQ9 input of the ERTEC 200 interrupt controller. Table 4 shows the events that can generate an interrupt from the PHYs:

| Interrupt number | Interrupt Event                 |  |

|------------------|---------------------------------|--|

| INT8             | not used                        |  |

| INT7             | ENERGYON generated              |  |

| INT6             | Auto-negotiation complete       |  |

| INT5             | Remote fault detected           |  |

| INT4             | Link down                       |  |

| INT3             | Auto-negotiation LP acknowledge |  |

| INT2             | Parallel detection fault        |  |

| INT1             | Auto-negotiation page received  |  |

#### Table 4: PHY Interrupt Events

Each of the interrupt events above is described in the protocol of the Interrupt Source Flag register in the PHYs; it can as well be masked or unmasked individually in the Interrupt Mask register in the PHYs (see Table 42: Interrupt Mask Register Description).

## (9) Isolate Mode

The PHY data path may be electrically isolated from the MII by setting the Isolate bit in the Basic Control register to  $1_b$ . In isolate mode, the internal MII interface of the respective PHY is made inactive. However the PHYs still respond to management transactions. Isolation provides a means for multiple PHYs to be connected to the same MII without contention occurring and it is not really required to use on ERTEC 200. The PHYs are not in isolate mode on power-up.

## (10) Link integrity Test

The PHYs perform a link integrity test as outlined in the IEEE 802.3 Link Monitor state diagram. The link status is multiplexed with the 10Mbps link status to form the reportable Link Status bit in the Basic Control register 1, and is driven to the P(2:1)-LINK-LED\_N output.

The DSP block indicates a valid MLT-3 waveform present on the P(2:1)RxP and P(2:1)RxN inputs as defined by the ANSI X3.263 TP-PMD standard, to the link monitor state-machine, using an internal signal called DATA\_VALID. When it is asserted the control logic moves into a link-ready state, and waits for an enable from the auto-negotiation block. When received, the link-up state is entered, and the transmit and receive logic blocks become active.Should auto-negotiation be disabled, the link integrity logic moves immediately to the link-up state, when the DATA\_VALID signal is asserted.

Note that to allow the link to stabilize, the link integrity logic will wait a minimum of 330 µsec from the time DATA\_VALID is asserted until the link-ready state is entered. Should the DATA\_VALID input be negated at any time, this logic will immediately negate the link signal and enter the link-down state. When the 10/100 digital block is in 10BASE-T mode, the link status generated from the 10BASE-T receiver logic.

## (11) Link Lockup Protection

During the reception of 10BASE-T data, the link partner may switch to 100BASE-TX without starting auto-negotiation. In this case, the PHY must recognize this, de-assert the link status, and switch to 100BASE-TX mode.

To achieve this, a counter is activated at the beginning of every 10BASE-T packet. When the counter reaches the count of 157 msec and no end of packet was recognized, then the link will be de-asserted and the PHY will restart either auto-negotiation (if enabled) or try to achieve a 10BASE-T link again.

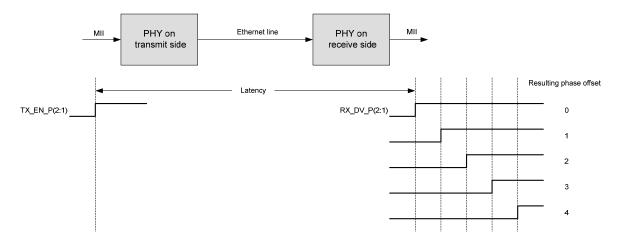

## (12) Phase Offset Indicator

The latency between transmitter and receiver can lead to 5 different phase variations of 125Mbps received packets against the 25Mbps data on the MII interface (only in 100BASE-TX/FX mode). It corresponds to the system latency between MII TX\_EN\_P(2:1) and MII RX\_DV\_P(2:1) and it is measured based on the first packet after link-up. This value is then stored in the PHASE\_OFFSET field of the Special Controls/Status Indications register. **Figure 4** illustrates this function.

Figure 4: Phase Offset Indicator Function

## 1.4 PHY Related Interfaces

Like any other peripheral on the ERTEC 200 the PHYs have internal registers that allow control over their behaviour and that reflect their operation status; however in contrast to the other peripherals, the PHY control registrs are not memory mapped and not directly accessible for the ARM CPU core or any other AHB master within ERTEC 200. This is due to the standardized MII/SMI interface between the PHYs and the MACs that are integrated in the IRT switch. **Figure 5** shows the different paths into the PHYs.

#### Figure 5: PHY Related Interfaces

The control and communication paths into and out of the PHYs can be categorized in four respectively five groups.

## (1) MII Interface

The media independent interface (MII) is the data communication interface between MAC and PHY; each PHY (respectively each MAC) has its own MII interface. The two MII interfaces on ERTEC 200 are on-chip interfaces however they can be externally monitored, if ERTEC 200 is configured to MII diagnosis mode. LBU interface pins are used for this purpose.

Table 5 lists the signals that belong to the MII diagnosis interface and the "normal" usage of the same pins for LBU signals.

| PHY   | Pin Name <sup>Note</sup> | I/O | Function                  | Alternate Function <sup>Note</sup> |

|-------|--------------------------|-----|---------------------------|------------------------------------|

|       | TXD_P2(3:0)              | 0   | Transmit data port 2 bits | LBU_D(9:6)                         |

|       | RXD_P23                  | 0   | Receive data port 2 bit 3 | LBU_A11/PIPESTA2                   |

|       | RXD_P22                  | 0   | Receive data port 2 bit 2 | LBU_A10/TRACESYNC                  |

|       | RXD_P21                  | 0   | Receive data port 2 bit 1 | LBU_A9/TRACEPKT0                   |

|       | RXD_P20                  | 0   | Receive data port 2 bit 0 | LBU_A8/TRACEPKT1                   |

|       | TX_EN_P2                 | 0   | Transmit enable port 2    | LBU_D10                            |

| PHY 2 | CRS_P2                   | 0   | Carrier sense port 2      | LBU_A12                            |

|       | RX_ER_P2                 | 0   | Receive error port 2      | PIPESTA0                           |

|       | TX_ERR_P2                | 0   | Transmit error port 2     | LBU_D11                            |

|       | RX_DV_P2                 | 0   | Receive data valid port 2 | LBU_A14                            |

|       | COL_P2                   | 0   | Collision port 2          | LBU_A15                            |

|       | RX_CLK_P2                | 0   | Receive clock port 2      | LBU_BE1_N                          |

|       | TX_CLK_P2                | 0   | Transmit clock port 2     | LBU_RD_N                           |

|       | TXD_P1(3:0)              | 0   | Transmit data port 1 bits | LBU_D(3:0)                         |

|       | RXD_P13                  | 0   | Receive data port 1 bit 3 | LBU_A3/TRACEPKT6                   |

|       | RXD_P12                  | 0   | Receive data port 1 bit 2 | LBU_A2/TRACEPKT7                   |

|       | RXD_P11                  | 0   | Receive data port 1 bit 1 | LBU_A1/ETMEXTIN1                   |

|       | RXD_P10                  | 0   | Receive data port 1 bit 0 | LBU_A0/ETMEXTOUT                   |

|       | TX_EN_P1                 | 0   | Transmit enable port 1    | LBU_D4                             |

| PHY1  | CRS_P1                   | 0   | Carrier sense port 1      | LBU_A4/TRACEPKT5                   |

|       | RX_ER_P1                 | 0   | Receive error port 1      | LBU_A5/TRACEPKT4                   |

|       | TX_ERR_P1                | 0   | Transmit error port 1     | LBU_D5                             |

|       | RX_DV_P1                 | 0   | Receive data valid port 1 | LBU_A6/TRACEPKT3                   |

|       | COL_P1                   | 0   | Collision port 1          | LBU_A7/TRACEPKT2                   |

|       | RX_CLK_P1                | 0   | Receive clock port 1      | LBU_BE0_N                          |

|       | TX_CLK_P1                | 0   | Transmit clock port 1     | LBU_WR_N                           |

#### Table 5: MII (Diagnosis) Interface Signals

**Note:** MII diagnosis interface pins are alternatively used as local bus interface or trace pins; in this table the I/O type is listed for the MII diagnosis function

## (2) SMI Interface

The serial management interface (SMI) between MAC and PHY gives access to the PHY's internal control registers. There is a common SMI interface for both PHYs; the two PHYs have hardwired addresses, that are part of the protocol over the SMI interface. The SMI signals can as well be monitored together with the MII signals in MII diagnosis mode.

Table 6 lists the signals that belong to the SMI (diagnosis) interface and the "normal" usage of the same pins for LBU signals.

| Pin Name <sup>Note</sup> | I/O | Function                                      | Alternate Function <sup>Note</sup> |

|--------------------------|-----|-----------------------------------------------|------------------------------------|

| SMI_MDC                  | 0   | Serial management interface clock             | LBU_D12                            |

| SMI_MDIO                 | 0   | Serial management interface data input/output | LBU_D13                            |

#### Table 6: SMI (Diagnosis) Interface Signals

**Note:** SMI diagnosis interface pins are alternatively used as local bus interface or trace pins; in this table the I/O type is listed for the SMI diagnosis function

#### (3) MDI Interface

The media dependent interface (MDI) is the PHY's data communication interface to the Ethernet network in 10BASE-T, 100BASE-TX or 100BAE-FX mode. It is partly analog and partly digital; the circuitry that is connected to the MDI interfaces must be carefully selected. Proposals can be found in Chapter 1.6.

| Pin Name   | I/O | Function                             | Operation mode |

|------------|-----|--------------------------------------|----------------|

| P(2:1)TxN  | 0   | Differential transmit data output    |                |

| P(2:1)TxP  | 0   | Differential transmit data output    | 10BASE-TX      |

| P(2:1)RxN  | I   | Differential receive data input      | 100BASE-TX     |

| P(2:1)RxP  | I   | Differential receive data input      |                |

| P(2:1)TDxN | 0   | Differential FX transmit data output |                |

| P(2:1)TDxP | 0   | Differential FX transmit data output |                |

| P(2:1)RDxN | I   | Differential FX receive data input   |                |

| P(2:1)RDxP | I   | Differential FX receive data input   | 100BASE-FX     |

| P(2:1)SDxN | I   | Differential FX signal detect input  |                |

| P(2:1)SDxP | I   | Differential FX signal detect input  |                |

Table 7 shows the MDI interface signals arranged for the various supported operation modes.

Table 7: MDI Interface Signals

#### (4) System control register interface

A few general controls for the PHYs can be directly set via a subset of the system control registers that are described in **\1\Chapter 4.8**.

- select the reset source for the PHYs

- enable auto-MDIX mode

- select the initial start up mode of the PHY, after they have been reset

- enable 100BASE-FX mode

- enable PHYs and release them from power down mode

- check operation status of PHYs

#### (5) Status LED Outputs

Each PHY provides six status LED outputs; four of these can be made simultaneously available on GPIO(7:0). The following status can be visualized in parallel:

| P1/2_DUPLEX_N      | Half duplex, full duplex                         |

|--------------------|--------------------------------------------------|

| P1/2_SPEED_N       | 10BASE-T, 100BASE-TX, 100BASE-FX                 |

| P1/2_LINK_STATUS_N | Link up, link down                               |

| P1/2_ACTIVITY_N    | Receive activity, transmit activity, no activity |

Table 3 shows the assignment of GPIO pins to these status informations.

#### (6) Other Signals

There are a few other signals - mainly supply voltages - related to the PHYs summarized in Table 8.

| Pin Name <sup>Note</sup> | I/O | Function                                                       | Alternate Function <sup>Note</sup> |

|--------------------------|-----|----------------------------------------------------------------|------------------------------------|

| RES_PHY_N                | 0   | Reset signal to PHYs                                           | LBU_D14                            |

| EXTRES                   | I/O | External reference resistor (12.4 k $\Omega$ ) <sup>Note</sup> | -                                  |

| DVDD(4:1)                | Ι   | Digital power supply, 1.5 V                                    | -                                  |

| DGND(4:1)                | I   | Digital GND                                                    | -                                  |

| P(2:1)VSSATX(2:1)        | I   | Analog port GND                                                | -                                  |

| P(2:1)VDDARXTX           | I   | Analog port RX/TX power supply, 1.5 V                          | -                                  |

| P(2:1)VSSARX             | I   | Analog port GND                                                | -                                  |

| VDDAPLL                  | I   | Analog central power supply, 1.5 V                             | -                                  |

| VDDACB                   | I   | Analog central power supply, 3.3 V                             | -                                  |

| VSSAPLLCB                | I   | Analog central GND                                             | -                                  |

| VDD33ESD                 | 1   | Analog test power supply, 3.3 V                                | -                                  |

| VSS33ESD                 | I   | Analog test GND                                                | -                                  |

#### Table 8: Other PHY Related Signals

**Note:** The external resistor must have a maximum tolerance of 1%.

## 1.5 PHY Register Description

Via the SMI interface access is given to the internal registers listed in Table 9. Note that these registers are implemented for each PHY. During write or read accesses the registers are selected using their register number as an address. The PHY internal registers are not memory mapped.

| Register number | Description                                                | Group           |  |  |

|-----------------|------------------------------------------------------------|-----------------|--|--|

| 0               | Basic control register                                     | Dasia           |  |  |

| 1               | Basic status register                                      | Basic           |  |  |

| 2               | PHY identifier 1                                           |                 |  |  |

| 3               | PHY identifier 2                                           |                 |  |  |

| 4               | Auto negotiation advertisement register                    |                 |  |  |

| 5               | Auto negotiation link partner ability register (base page) | Extended        |  |  |

|                 | Auto negotiation link partner ability register (next page) |                 |  |  |

| 6               | Auto negotiation expansion register                        |                 |  |  |

| 7               | Next page transmit register                                |                 |  |  |

| 8-15            | Reserved                                                   | -               |  |  |

| 16              | Silicon revision register                                  |                 |  |  |

| 17              | Mode control/status register                               |                 |  |  |

| 18              | Special mode register                                      |                 |  |  |

| 19-26           | Reserved                                                   |                 |  |  |

| 27              | Special control/status indication register                 | Vendor specific |  |  |

| 28              | Reserved                                                   |                 |  |  |

| 29              | Interrupt source register                                  |                 |  |  |

| 30              | Interrupt mask register                                    |                 |  |  |

| 31              | PHY special control/status register                        |                 |  |  |

#### Table 9: PHY internal Registers

During a hardware reset or when the PHYs are driven out of the power down state (by setting the P1/2\_PHY\_ENB bits in the PHY\_CONFIG register to  $1_b$ ), a pre-defined configuration is set in the registers. This configuration is partly hardwired and affects the initial settings of PHY-internal registers. Table 10 shows these settings; the initial configuration can be altered later by writing to the PHY-internal registers.

| Name                 | Description                                       | Port 1                              | Port 2               |  |  |  |  |  |

|----------------------|---------------------------------------------------|-------------------------------------|----------------------|--|--|--|--|--|

| P1/2_PHYADDRESS(4:0) | PHY address                                       | 00000 <sub>b</sub>                  | 00001 <sub>b</sub>   |  |  |  |  |  |

| P1/2_PHYMODE(2:0)    | PHY mode                                          | FIG register setting                |                      |  |  |  |  |  |

| P1/2_MIIMODE(1:0)    | Interface mode of PHY                             | permanently set to MII              | mode                 |  |  |  |  |  |

| P1/2_SMIISOURCESYNC  | SMII source mode permanently set to normal mode   |                                     |                      |  |  |  |  |  |

| P1/2_FXMODE          | 100BASE-FX mode depends on PHY_CONFIG register se |                                     |                      |  |  |  |  |  |

| P1/2_AUTOMDIXEN      | Enable AutoMDIX state machine                     | depends on PHY_CON                  | FIG register setting |  |  |  |  |  |

| P1/2_NPMSGCODE(2:0)  | Test of next page function                        | permanently set to 000 <sub>b</sub> |                      |  |  |  |  |  |

| P1/2_PHYENABLE       | Enables the PHYs                                  | depends on PHY_CON                  | FIG register setting |  |  |  |  |  |

| REG2OUIIN(15:0)      | Default value for SMII register 2                 | 0033H                               |                      |  |  |  |  |  |

| REG3OUIIN(15:0)      | Default value for SMII register 3                 | 2001H                               |                      |  |  |  |  |  |

Table 10: Initial Parameter Settings for PHYs

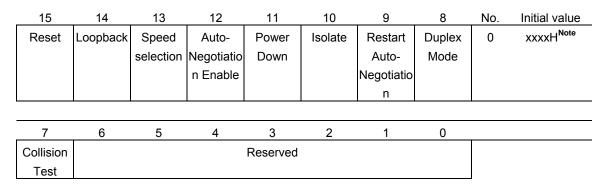

#### 1.5.1 Basic Control Register

#### Table 11: Basic Control Register Overview

**Note:** The initial value depends on the setting of the P(2:1)\_PHY\_MODE(2:0) bits in the PHY1/2 Configuration Register in the System Control Register block.

| Bit position | Bit name              | R/W |         |                                                                            | Function                                                                                                 |  |  |  |  |  |  |

|--------------|-----------------------|-----|---------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 15           | Reset                 | R/W | Reset   |                                                                            |                                                                                                          |  |  |  |  |  |  |

|              |                       |     | Resets  | s the complete PH                                                          | łY                                                                                                       |  |  |  |  |  |  |

|              |                       |     |         | Reset                                                                      | Software reset                                                                                           |  |  |  |  |  |  |

|              |                       |     |         | Ob                                                                         | Normal operation (initial value)                                                                         |  |  |  |  |  |  |

|              |                       |     |         | 1 <sub>b</sub>                                                             | Execute a software reset for the affected PHY                                                            |  |  |  |  |  |  |

|              |                       |     | Note:   | This bit is self-o                                                         | clearing; it is automatically set to $0_b$ by the reset pro                                              |  |  |  |  |  |  |

| 14           | Loopback              | R/W | Loopb   | ack                                                                        |                                                                                                          |  |  |  |  |  |  |

|              |                       |     | Contro  | ols internal loopba                                                        | ick mode                                                                                                 |  |  |  |  |  |  |

|              |                       |     |         | Loopback                                                                   | Internal loopback mode                                                                                   |  |  |  |  |  |  |

|              |                       |     |         | 0 <sub>b</sub>                                                             | Disable internal loopback mode (initial value)                                                           |  |  |  |  |  |  |

|              |                       |     |         | 1 <sub>b</sub> Enable internal loopback mode                               |                                                                                                          |  |  |  |  |  |  |