# SIEMENS

# SIMATIC TI505

## Programming Reference

User Manual

Order Number: PPX:505-8104-5 Manual Assembly Number: 2586546-0051 Fifth Edition This manual contains the following notices intended to ensure personal safety, as well as to protect the products and connected equipment against damage.

## **DANGER**

**DANGER** indicates an imminently hazardous situation that, if not avoided, will result in death or serious injury.

DANGER is limited to the most extreme situations.

### **WARNING**

**WARNING** indicates a potentially hazardous situation that, if not avoided, could result in death or serious injury, and/or property damage.

##

**CAUTION** indicates a potentially hazardous situation that, if not avoided, could result in minor or moderate injury, and/or damage to property.

CAUTION is also used for property-damage-only accidents.

#### Copyright 1995 by Siemens Industrial Automation, Inc. All Rights Reserved — Printed in USA

Reproduction, transmission or use of this document or contents is not permitted without express consent of Siemens Industrial Automation, Inc. All rights, including rights created by patent grant or registration of a utility model or design, are reserved.

Since Siemens Industrial Automation, Inc. does not possess full access to data concerning all of the uses and applications of customer's products, we do not assume responsibility either for customer product design or for any infringements of patents or rights of others which may result from our assistance.

### MANUAL PUBLICATION HISTORY

SIMATIC TI505 Programming Reference Manual Order Manual Number: PPX:505-8104-5

Refer to this history in all correspondence and/or discussion about this manual.

| Event          | Date  | Description                                          |

|----------------|-------|------------------------------------------------------|

| Original Issue | 12/89 | Original Issue (2592436–0001)                        |

| Second Edition | 03/90 | Second Edition (2592436–0002)                        |

| Errata Package | 05/90 | Corrections to Chapters 2, 11, and 13 (2592435–0001) |

| Third Edition  | 04/92 | Third Edition (2592436–0003)                         |

| Fourth Edition | 05/93 | Fourth Edition (2592436–0004)                        |

| Fifth Edition  | 02/95 | Fifth Edition (2592436–0005)                         |

### LIST OF EFFECTIVE PAGES

| Pages                   | Description | Pages | Description |

|-------------------------|-------------|-------|-------------|

| Cover/Copyright         | Fifth       |       |             |

| History/Effective Pages | Fifth       |       |             |

| iii — xxxvi             | Fifth       |       |             |

| 1-1 — 1-27              | Fifth       |       |             |

| 2-1 — 2-7               | Fifth       |       |             |

| 3-1 — 3-16              | Fifth       |       |             |

| 4-1 — 4-11              | Fifth       |       |             |

| 5-1 — 5-43              | Fifth       |       |             |

| 6-1 — 6-185             | Fifth       |       |             |

| 7-1 — 7-74              | Fifth       |       |             |

| 8-1 — 8-15              | Fifth       |       |             |

| 9-1 — 9-33              | Fifth       |       |             |

| A-1 — A-13              | Fifth       |       |             |

| B-1 — B-6               | Fifth       |       |             |

| C-1 — C-27              | Fifth       |       |             |

| D-1 — D-4               | Fifth       |       |             |

| E-1 — E-43              | Fifth       |       |             |

| F-1 — F-1               | Fifth       |       |             |

| G-1 — G-36              | Fifth       |       |             |

| H-1 — H-17              | Fifth       |       |             |

| Index-1 — Index-10      | Fifth       |       |             |

| Registration            | Fifth       |       |             |

# Contents

#### Preface

| Chap | oter 1 Series 505/500 System Overview                                          |              |

|------|--------------------------------------------------------------------------------|--------------|

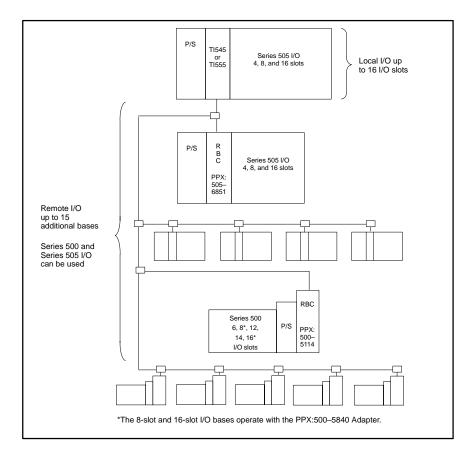

| 1.1  | The TI545 and TI555 Systems                                                    | 1-2          |

|      | System Components<br>Local and Remote I/O                                      | 1-2<br>1-2   |

|      | Assigning I/O Point Numbers                                                    | 1-2          |

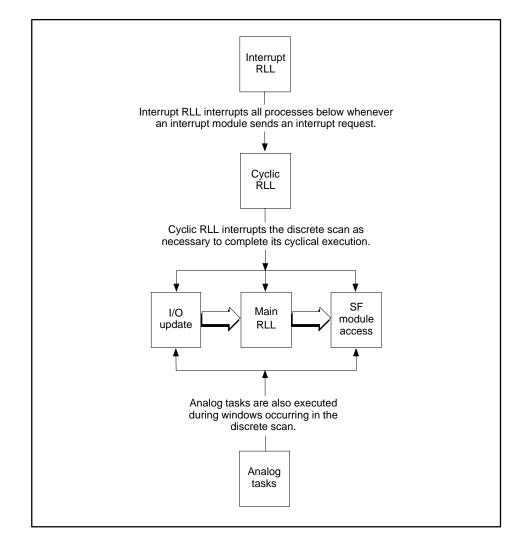

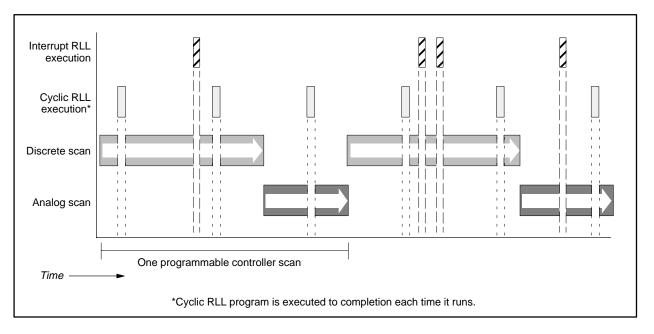

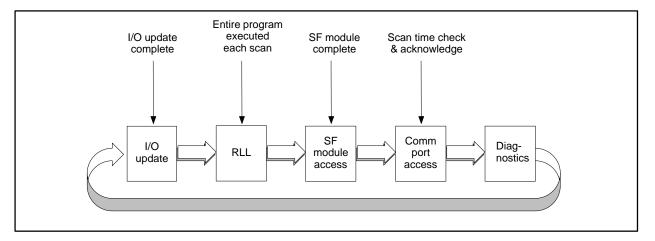

|      | Program Execution Interrupt RLL Execution                                      | 1-4<br>1-4   |

|      | Cyclic RLL Execution                                                           | 1-4          |

|      | Discrete Scan                                                                  | 1-4          |

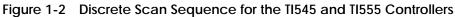

|      | Analog Task Processing                                                         | 1-6          |

|      | Cyclic Analog Tasks                                                            | 1-6          |

|      | Non-cyclic Analog Tasks                                                        | 1-7          |

|      | Setting the Scan                                                               | 1-8          |

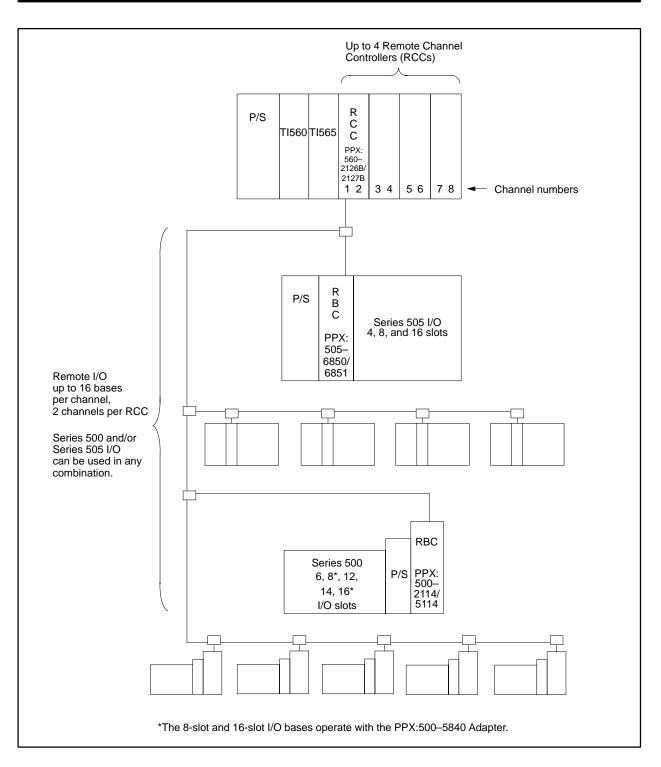

| 1.2  | The TI560/TI565 System                                                         | 1-10         |

|      | TI560/TI565 System Components                                                  | 1-10         |

|      | TI560/TI565 Remote I/O                                                         | 1-10         |

|      | Assigning I/O Point Numbers                                                    | 1-12         |

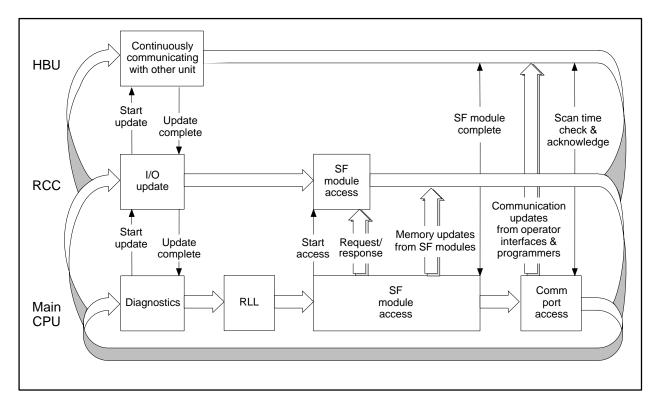

|      | TI560 Scan Operation                                                           | 1-12         |

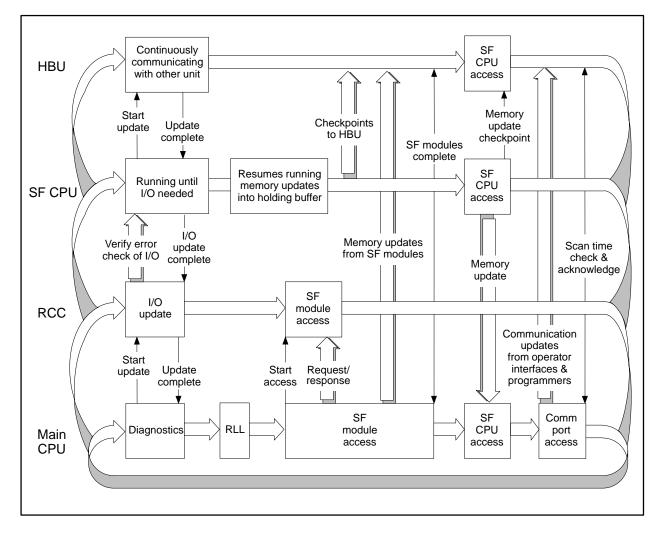

|      | TI565 CPU Functions                                                            | 1-14         |

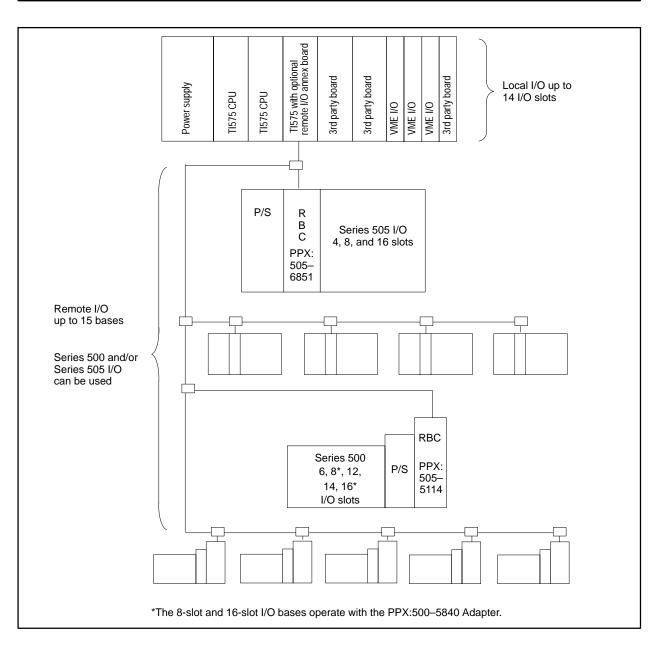

| 1.3  | The TI575 System                                                               | 1-16         |

|      | TI575 System Components                                                        | 1-16         |

|      | TI575 Local and Remote I/O                                                     | 1-16         |

|      | TI575 Scan Operation                                                           | 1-16         |

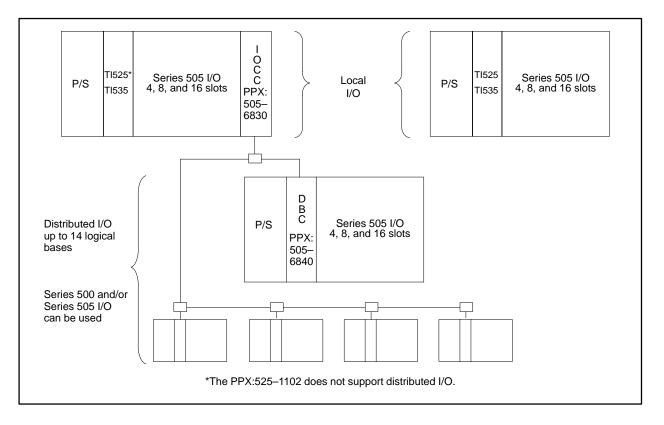

| 1.4  | The TI525/TI535 Systems                                                        | 1-18         |

|      | System Components                                                              | 1-18         |

|      | Local and Distributed I/O                                                      | 1-18         |

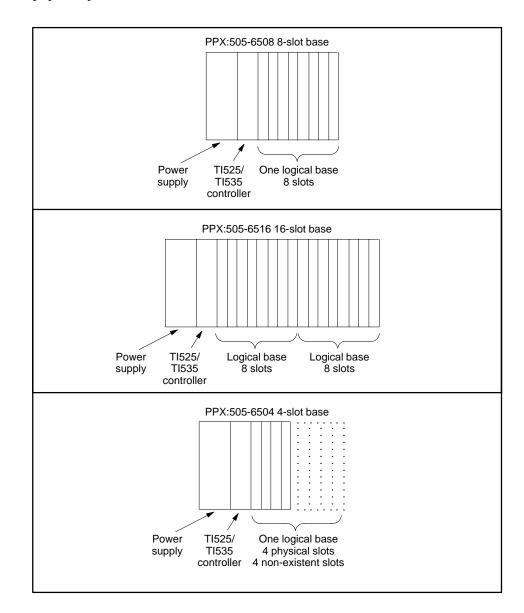

|      | Series 505 Logical Base                                                        | 1-19         |

|      | Assigning I/O Point Numbers                                                    | 1-20         |

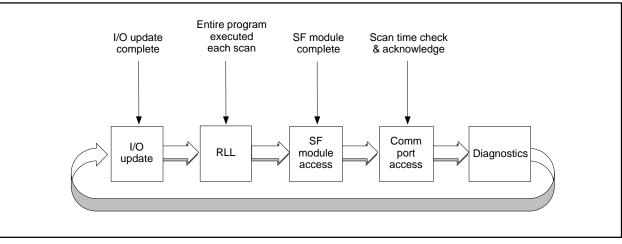

|      | Scan Operation                                                                 | 1-21         |

| 1.5  | The TI520C/TI530C/TI530T Systems                                               | 1-22         |

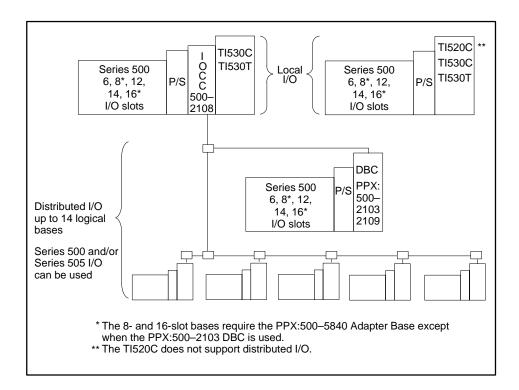

|      | System Components                                                              | 1-22         |

|      | Local and Distributed I/O                                                      | 1-22         |

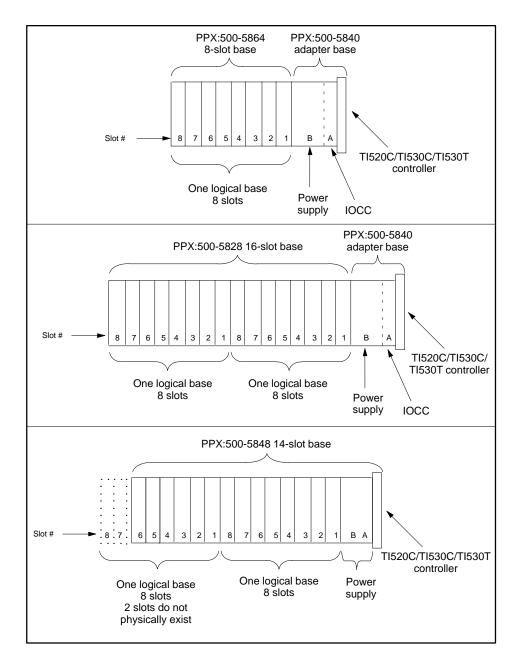

|      | Series 500 Logical Base                                                        | 1-23         |

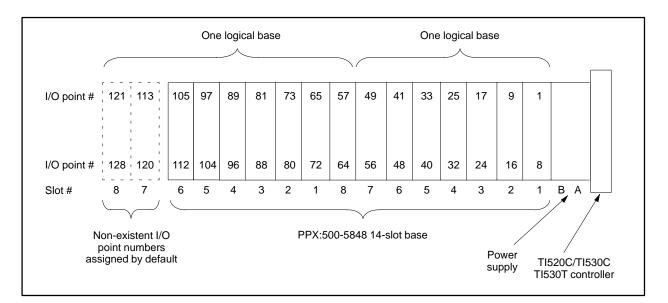

|      | Assigning I/O Point Numbers                                                    | 1-24<br>1-25 |

|      | Using Default I/O Numbers<br>Using Default Numbers with 6-, 12-, 14-Slot Bases | 1-25<br>1-26 |

|      | Scan Operation                                                                 | 1-27         |

|      |                                                                                | -            |

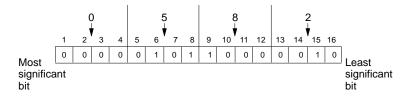

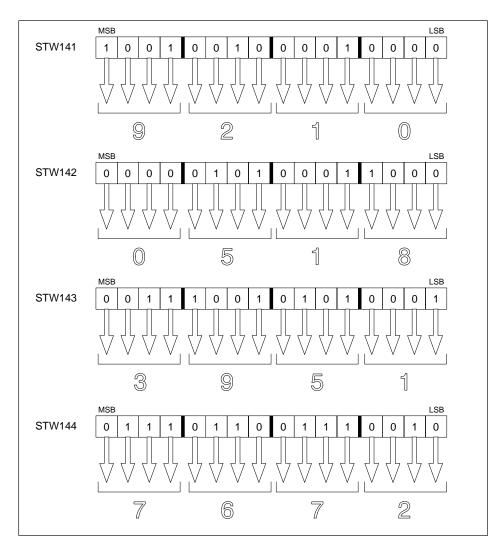

### Chapter 2 Data Representation

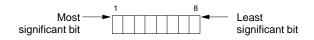

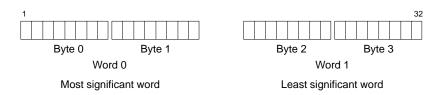

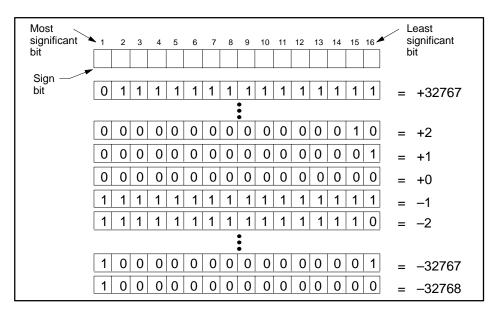

| 2.1  | Definitions                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-2                                                                              |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 2.2  | Integers                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-3                                                                              |

| 2.3  | Real Numbers and Binary-Coded Decimal         Real Numbers         Binary Coded Decimal                                                                                                                                                                                                                                                                                                                                           | <b>2-5</b><br>2-5<br>2-5                                                         |

| 2.4  | Format for an Address Stored in a Memory Location                                                                                                                                                                                                                                                                                                                                                                                 | 2-6                                                                              |

| Chap | oter 3 I/O Concepts                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

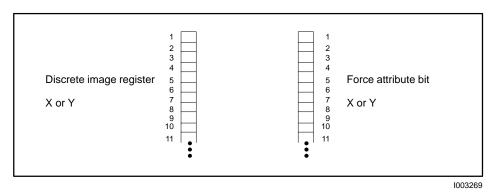

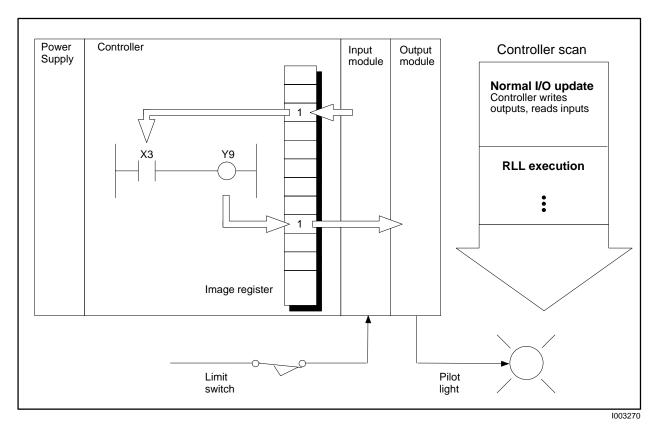

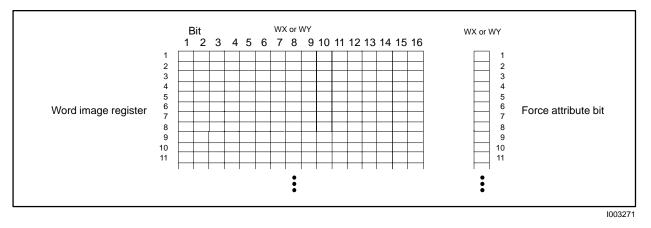

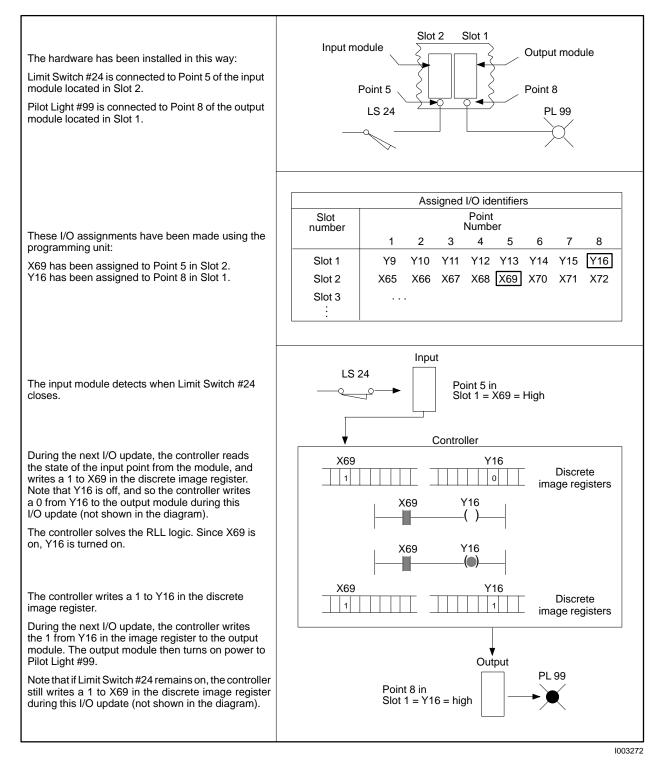

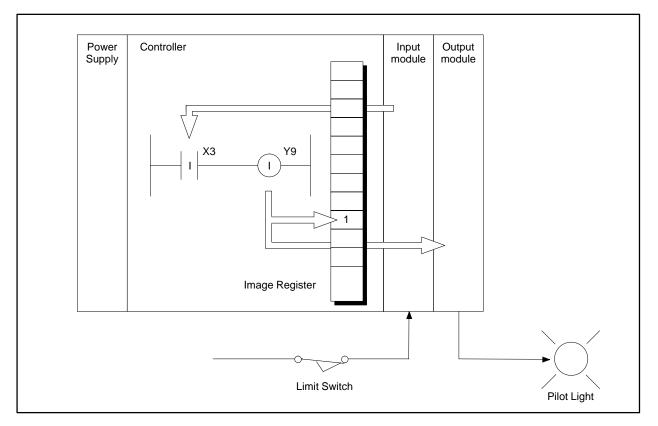

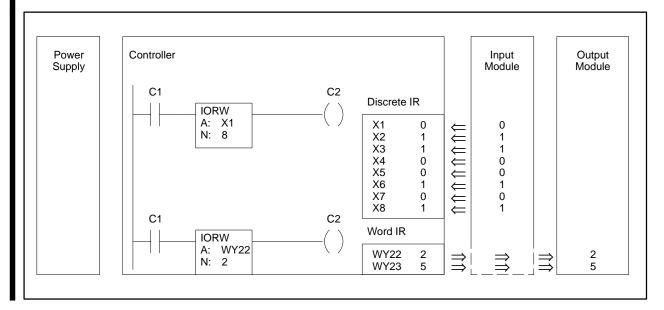

| 3.1  | Reading and Updating the I/O<br>Discrete Image Register<br>Word Image Register                                                                                                                                                                                                                                                                                                                                                    | <b>3-2</b><br>3-2<br>3-5                                                         |

| 3.2  | Normal I/O Updates<br>Discrete Control<br>Analog Control                                                                                                                                                                                                                                                                                                                                                                          | <b>3-6</b><br>3-6<br>3-6                                                         |

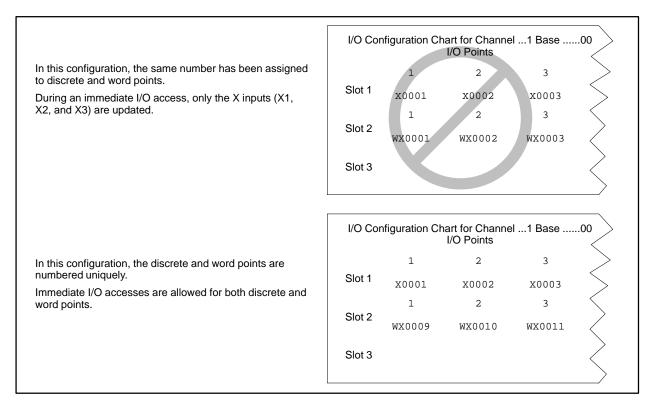

| 3.3  | High Speed I/O Updates         Immediate I/O         Modules that Support Immediate I/O         Configuring Immediate I/O                                                                                                                                                                                                                                                                                                         | <b>3-8</b><br>3-8<br>3-10<br>3-11                                                |

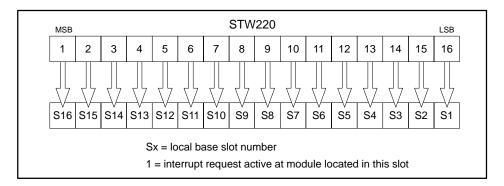

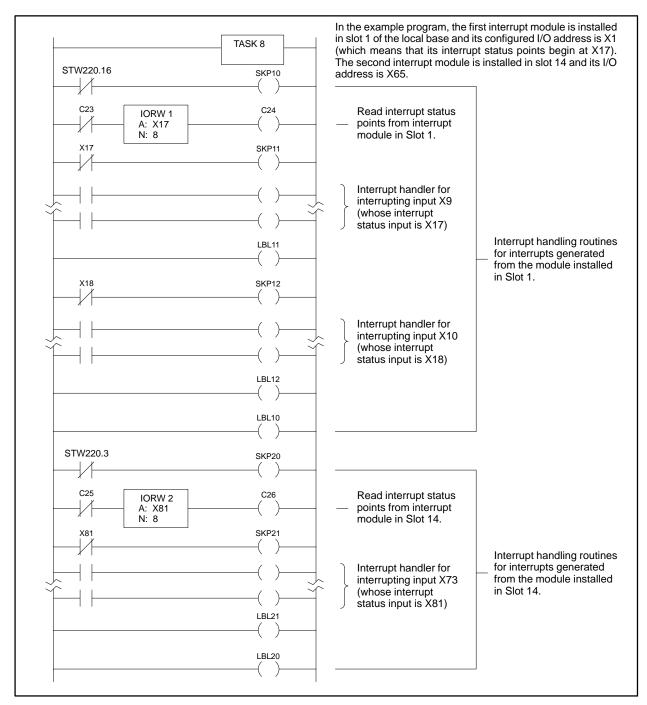

| 3.4  | Interrupt I/O Operation<br>Overview<br>Configuring the Interrupt Input Module                                                                                                                                                                                                                                                                                                                                                     | <b>3-12</b><br>3-12<br>3-12                                                      |

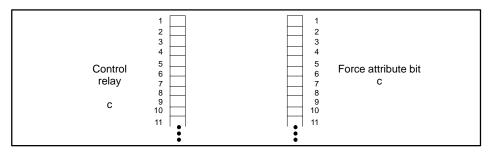

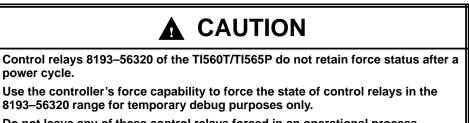

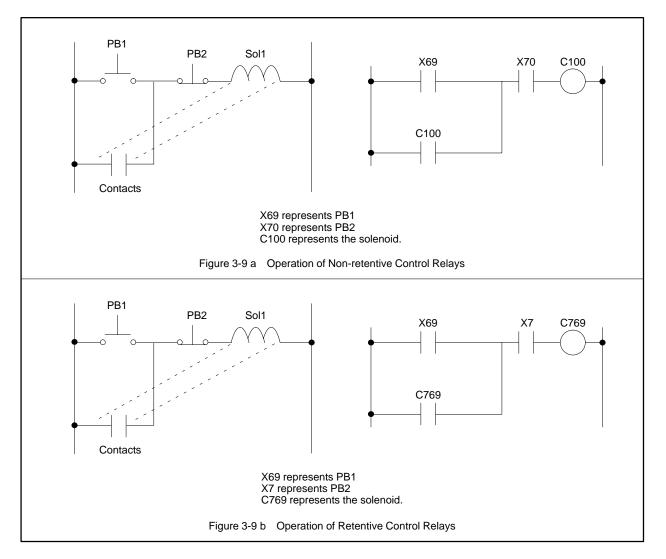

| 3.5  | Control Relays<br>Using Retentive and Non-retentive Control Relays                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

| Chap | oter 4 Controller Memory                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |

| 4.1  | Introduction to Controller Memory          RLL Access to the Memory Types                                                                                                                                                                                                                                                                                                                                                         | <b>4-2</b><br>4-3                                                                |

| 4.2  | Controller Memory Types<br>Ladder Memory<br>Image Register Memory<br>Control Relay Memory<br>Special Memory: TI545, TI555, TI565, TI575 Controllers Only<br>Temporary Memory: TI545, TI555, TI565, TI575 Controllers Only<br>Variable Memory<br>Constant Memory: TI545, TI555, TI560/TI565, TI575 Controllers Only<br>Status Word Memory<br>Timer/Counter Memory<br>Table Move Memory<br>One Shot Memory<br>Shift Register Memory | <b>4-4</b><br>4-4<br>4-4<br>4-4<br>4-4<br>4-4<br>4-5<br>4-5<br>4-5<br>4-5<br>4-5 |

| Drum Memory                                                           | . 4-9  |

|-----------------------------------------------------------------------|--------|

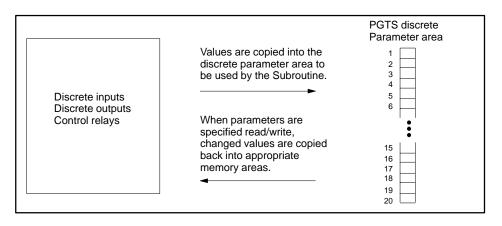

| PGTS Discrete Parameter Area: TI545, TI555, TI575, TI560/TI565        | . 4-10 |

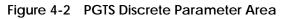

| PGTS Word Parameter Area: TI545, TI555, TI575, TI560/TI565            | . 4-10 |

| User External Subroutine Memory: TI545, TI555, TI575 Controllers Only | . 4-11 |

| Global Memory: TI575 Only                                             | . 4-11 |

| VME Memory: TI575 Only                                                | . 4-11 |

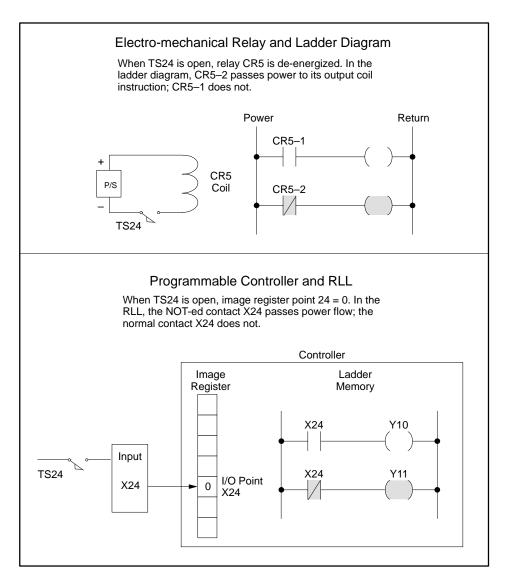

### Chapter 5 Programming Concepts

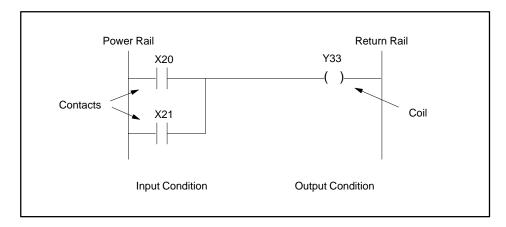

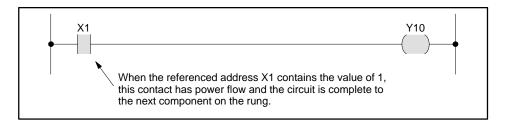

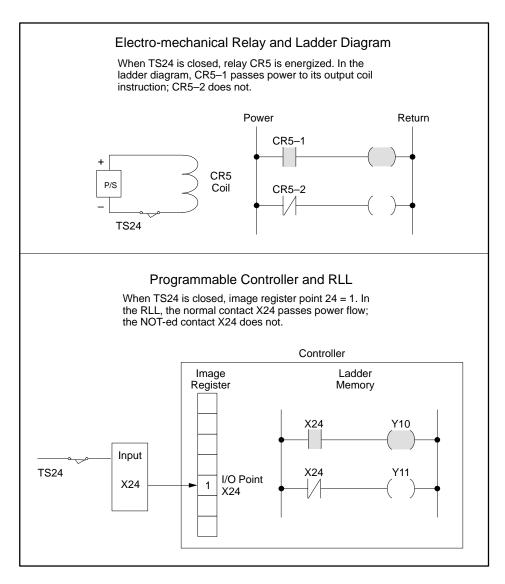

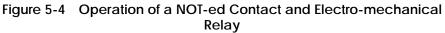

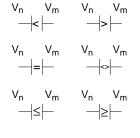

| 5.1 | RLL Components                                                                                                                                                                                                  | 5-2                                 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

|     | RLL Concept<br>RLL Contact<br>RLL Coil                                                                                                                                                                          | 5-3<br>5-4<br>5-10                  |

|     | RLL Box Instruction                                                                                                                                                                                             | 5-14<br>5-14<br>5-15                |

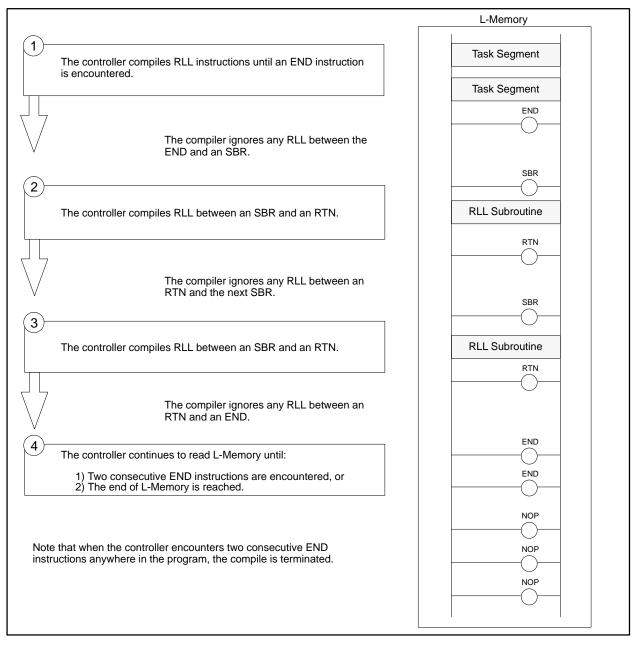

| 5.2 | Program Compile Sequence                                                                                                                                                                                        | 5-16                                |

| 5.3 | Using Subroutines (TI545, TI555, TI560/TI565, and TI575)<br>RLL Subroutine Programs<br>SF Programs<br>External Subroutines                                                                                      | <b>5-18</b><br>5-18<br>5-19<br>5-19 |

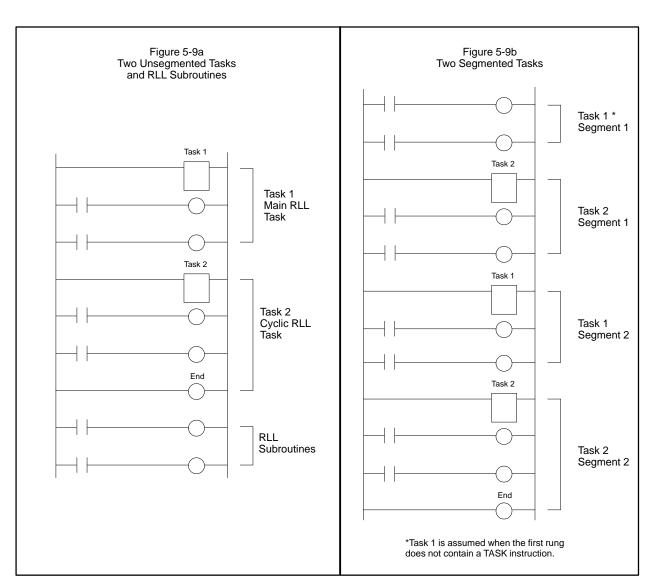

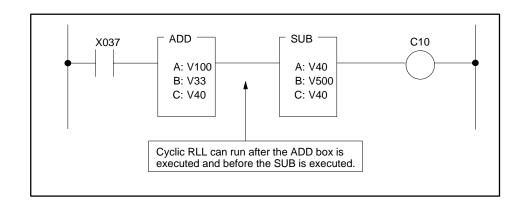

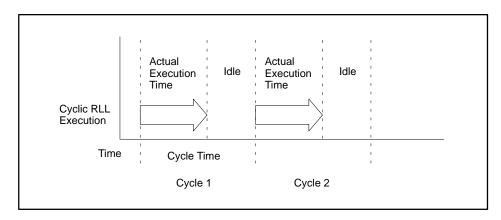

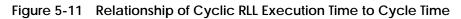

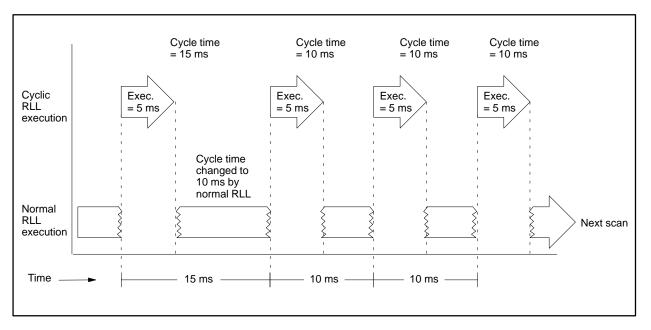

| 5.4 | Cyclic RLL<br>Overview<br>Cyclic RLL Execution                                                                                                                                                                  | <b>5-20</b><br>5-20<br>5-22         |

| 5.5 | Interrupt RLL                                                                                                                                                                                                   | 5-24                                |

|     | The Interrupt RLL Program<br>Operation<br>Performance Characteristics<br>Troubleshooting                                                                                                                        | 5-24<br>5-27<br>5-28<br>5-29        |

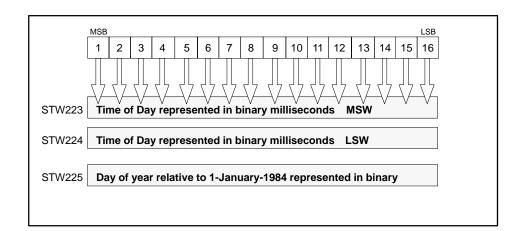

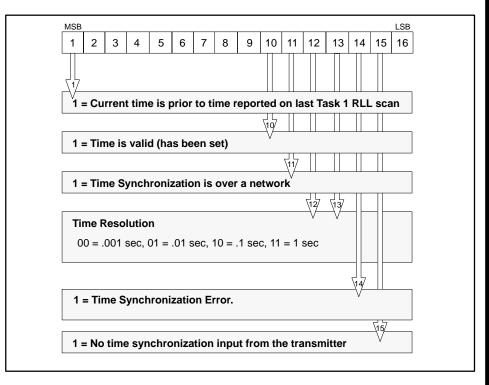

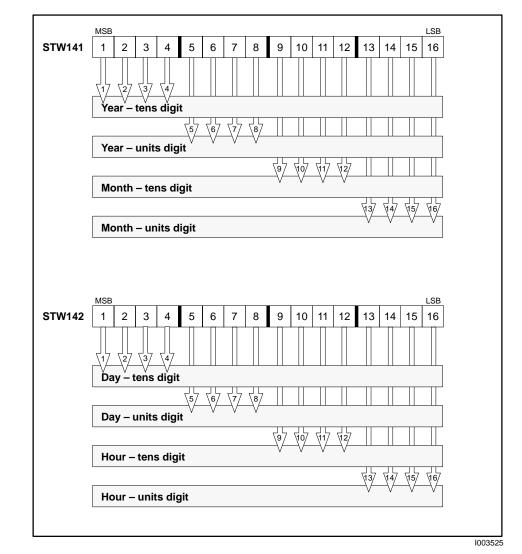

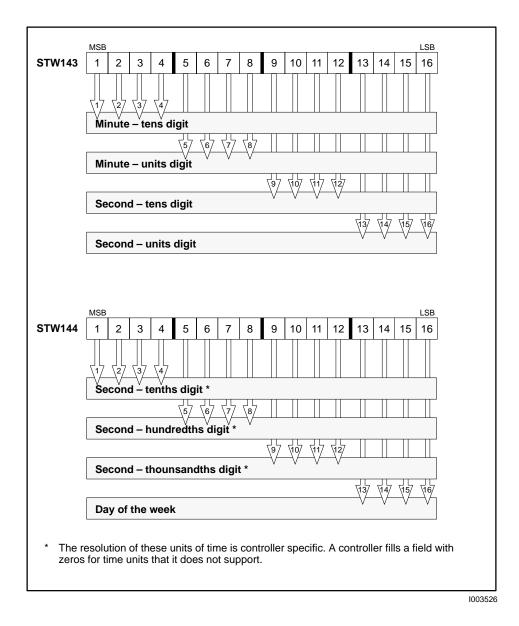

| 5.6 | Using Real-Time Clock Data (TI545, TI555, TI560/TI565, TI575)                                                                                                                                                   | 5-30                                |

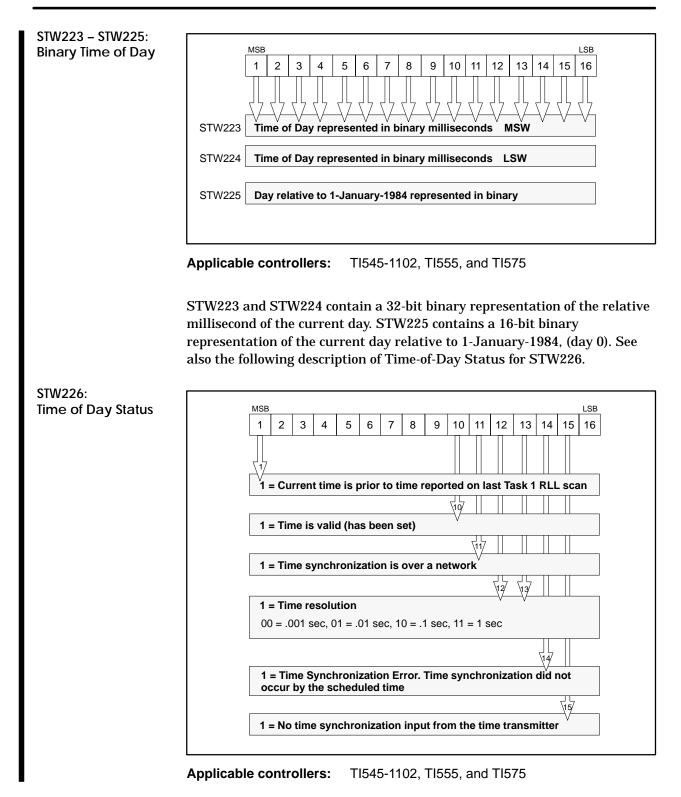

|     | BCD Time of Day<br>Binary Time of Day<br>Time of Day Status                                                                                                                                                     | 5-30<br>5-32<br>5-33                |

| 5.7 | Entering Relay Ladder Logic                                                                                                                                                                                     | 5-34                                |

|     | Using APT<br>Using TISOFT                                                                                                                                                                                       | 5-34<br>5-34                        |

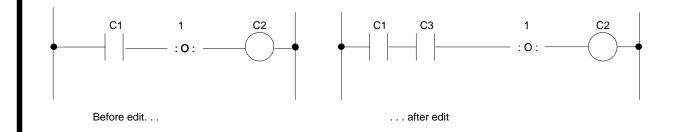

| 5.8 | Doing Run-Time Program Edits                                                                                                                                                                                    | 5-35                                |

|     | Using TISOFT 4.2 or Later with the TI545, TI555, or TI575<br>Using TISOFT 4.01 or Earlier (All Controllers)<br>Avoid These Actions During Run-Time Edits<br>Additional Considerations When Doing Run-Time Edits | 5-35<br>5-36<br>5-37<br>5-40        |

| 5.9  | Password Protection                                                                                                                                                  | 5-42                                 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

|      | Protected Program Elements<br>Disabled and Enabled Passwords<br>Password Protection Levels<br>Determining the Current State of Password<br>Password Effect on EEPROM | 5-42<br>5-42<br>5-43<br>5-43<br>5-43 |

| Chap | oter 6 RLL Instruction Set                                                                                                                                           |                                      |

| 6.1  | Safety Considerations                                                                                                                                                | 6-4                                  |

|      | Overview                                                                                                                                                             | 6-4<br>6-4                           |

|      | Inconsistent Program Operation                                                                                                                                       | 6-5                                  |

|      | Editing an Active Process                                                                                                                                            | 6-5                                  |

| 6.2  | Introduction                                                                                                                                                         | 6-6                                  |

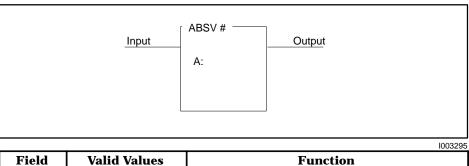

| 6.3  | Absolute Value                                                                                                                                                       | 6-11                                 |

|      | ABSV Description                                                                                                                                                     | 6-11<br>6-11                         |

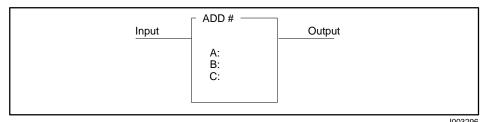

| 6.4  | Add                                                                                                                                                                  | 6-12                                 |

|      | ADD Description                                                                                                                                                      | 6-12<br>6-12                         |

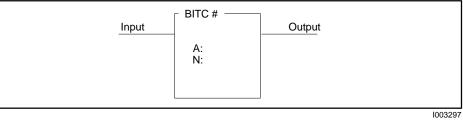

| 6.5  | Bit Clear                                                                                                                                                            | 6-13                                 |

|      | BITC DescriptionBITC Operation                                                                                                                                       | 6-13<br>6-13                         |

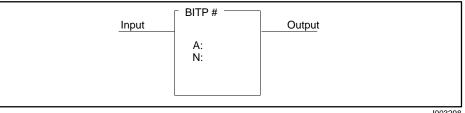

| 6.6  | Bit Pick                                                                                                                                                             | 6-14                                 |

|      | BITP Description                                                                                                                                                     | 6-14<br>6-14                         |

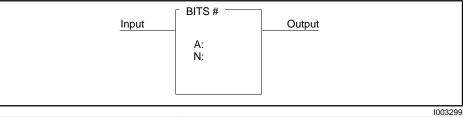

| 6.7  | Bit Set                                                                                                                                                              | 6-15                                 |

|      | BITS Description                                                                                                                                                     | 6-15<br>6-15                         |

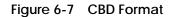

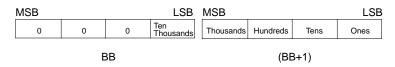

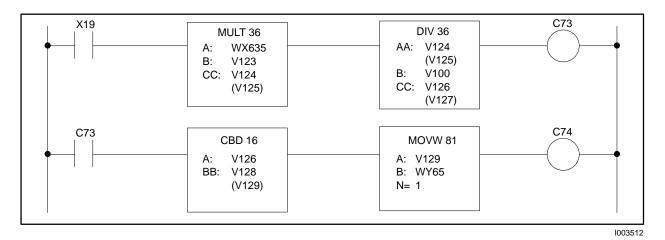

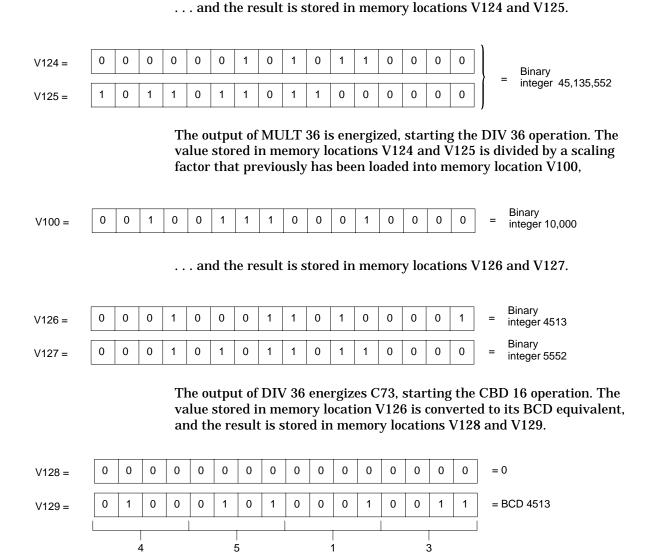

| 6.8  | Convert Binary to BCD                                                                                                                                                | 6-16                                 |

|      | CBD Description                                                                                                                                                      | 6-16<br>6-16                         |

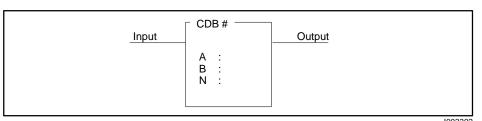

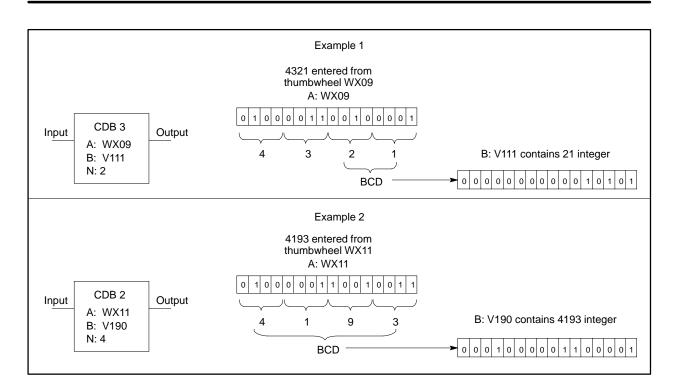

| 6.9  | Convert BCD to Binary                                                                                                                                                | 6-18                                 |

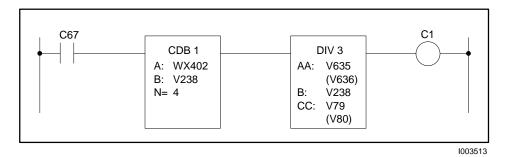

|      | CDB Description                                                                                                                                                      | 6-18<br>6-18                         |

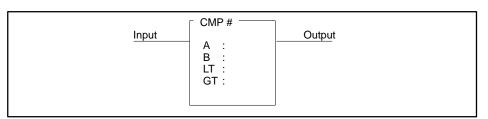

| 6.10 | Compare                                                                                                                                                              | 6-20                                 |

|      | CMP Description                                                                                                                                                      | 6-20<br>6-20                         |

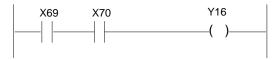

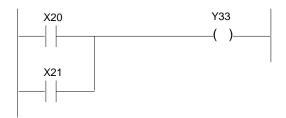

| 6.11 | Coils                                                                                                                                                                | 6-22                                 |

| 6.12 | Contacts                                                                                                                                                             | 6-23                                 |

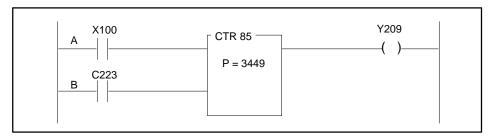

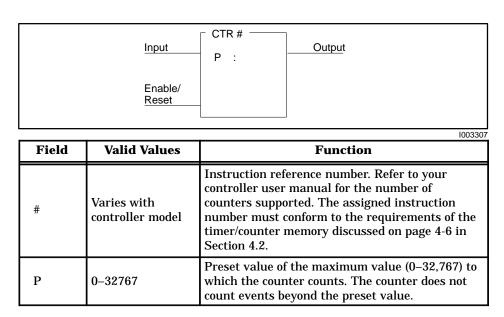

| 6.13 | Counter (Up Counter)                                                                                                                                                                                                                       | 6-24                                                         |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

|      | CTR Description<br>CTR Operation<br>Using the Counter Variables                                                                                                                                                                            | 6-24<br>6-24<br>6-25                                         |

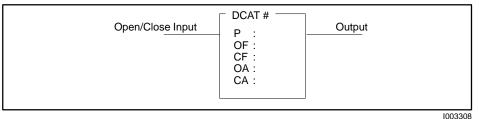

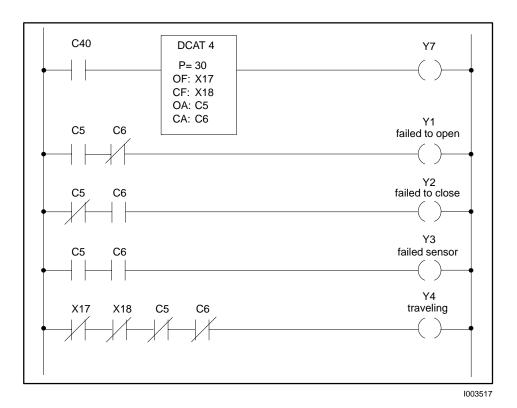

| 6.14 | Discrete Control Alarm Timer                                                                                                                                                                                                               | 6-26                                                         |

|      | DCAT Description<br>DCAT State Changes<br>DCAT Operation<br>Open/Close Input Turns On<br>Open/Close Input Turns Off<br>Using the DCAT Variables                                                                                            | 6-26<br>6-27<br>6-28<br>6-28<br>6-28<br>6-29                 |

| 6.15 | Date Compare                                                                                                                                                                                                                               | 6-30                                                         |

|      | DCMP Description                                                                                                                                                                                                                           | 6-30<br>6-31                                                 |

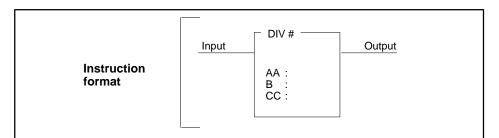

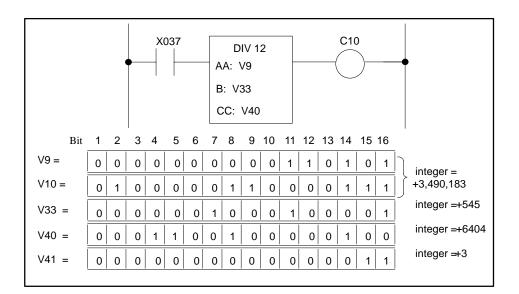

| 6.16 | Divide                                                                                                                                                                                                                                     | 6-32                                                         |

|      | DIV Description                                                                                                                                                                                                                            | 6-32<br>6-32                                                 |

| 6.17 | Time Driven Drum                                                                                                                                                                                                                           | 6-34                                                         |

|      | DRUM Description<br>DRUM Operation<br>Calculating Counts/Step<br>Using DRUM Variables                                                                                                                                                      | 6-34<br>6-35<br>6-36<br>6-37                                 |

| 6.18 | Date Set                                                                                                                                                                                                                                   | 6-38                                                         |

|      | DSET Description                                                                                                                                                                                                                           | 6-38<br>6-39                                                 |

| 6.19 | Time/Event Driven Drum                                                                                                                                                                                                                     | 6-40                                                         |

|      | EDRUM Description<br>EDRUM Operation<br>Calculating Counts/Step<br>Timer-triggered Advance Only<br>Event-triggered Advance Only<br>Timer and Event-Triggered Advance<br>Timer or External Event-triggered Advance<br>Using EDRUM Variables | 6-40<br>6-41<br>6-42<br>6-42<br>6-42<br>6-43<br>6-43<br>6-43 |

| 6.20 | Unconditional End                                                                                                                                                                                                                          | 6-44                                                         |

|      | END Description                                                                                                                                                                                                                            | 6-44<br>6-44                                                 |

| 6.21 | Conditional End                                                                                                                                                                                                                            | 6-45                                                         |

|      | ENDC DescriptionENDC Operation                                                                                                                                                                                                             | 6-45<br>6-45                                                 |

| 6.22 |                                                                                                                 | 6-46                 |

|------|-----------------------------------------------------------------------------------------------------------------|----------------------|

|      | FRS Description<br>FRS Operation                                                                                | 6-46<br>6-47         |

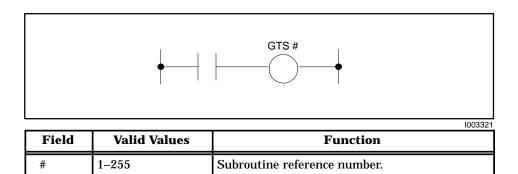

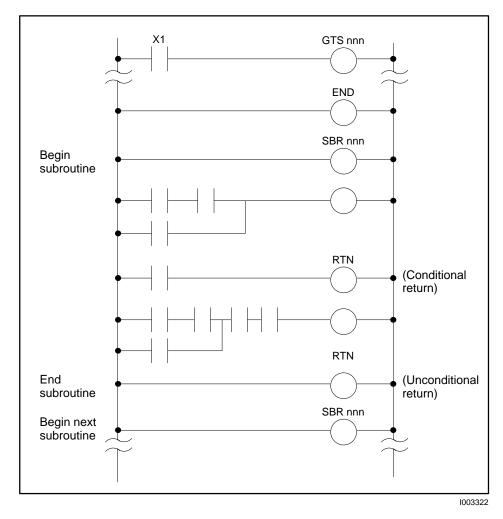

| 6.23 | Go To Subroutine                                                                                                | 6-48                 |

|      | GTS Description                                                                                                 | 6-48<br>6-48         |

| 6.24 | Indexed Matrix Compare                                                                                          | 6-50                 |

|      | IMC Description<br>IMC Operation                                                                                | 6-50<br>6-51         |

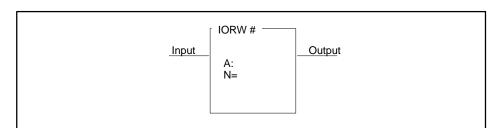

| 6.25 | Immediate I/O Read/Write                                                                                        | 6-52                 |

|      | IORW Description                                                                                                | 6-52<br>6-52         |

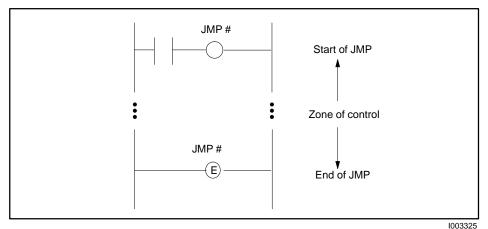

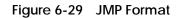

| 6.26 | Jump                                                                                                            | 6-54                 |

|      | JMP Description                                                                                                 | 6-54<br>6-54         |

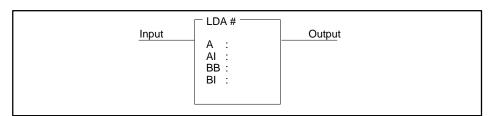

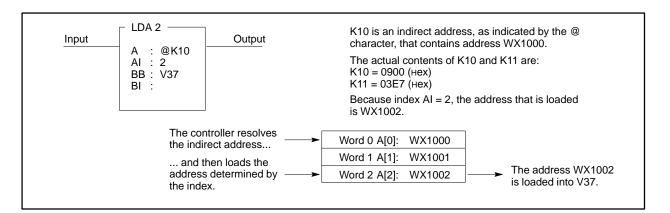

| 6.27 | Load Address                                                                                                    | 6-56                 |

|      | LDA Description                                                                                                 | 6-56<br>6-57         |

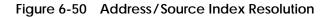

|      | Specifying Source       Specifying Index for Source         Specifying Destination       Specifying Destination | 6-57<br>6-58<br>6-58 |

|      | Specifying Index for Destination                                                                                | 6-59                 |

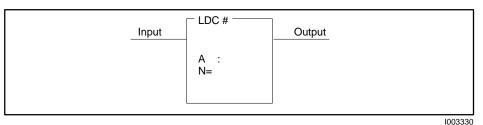

| 6.28 | Load Data Constant                                                                                              | 6-61                 |

|      | LDC DescriptionLDC Operation                                                                                    | 6-61<br>6-61         |

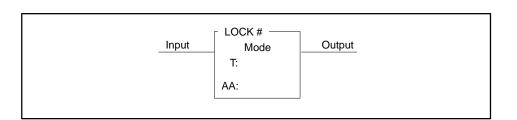

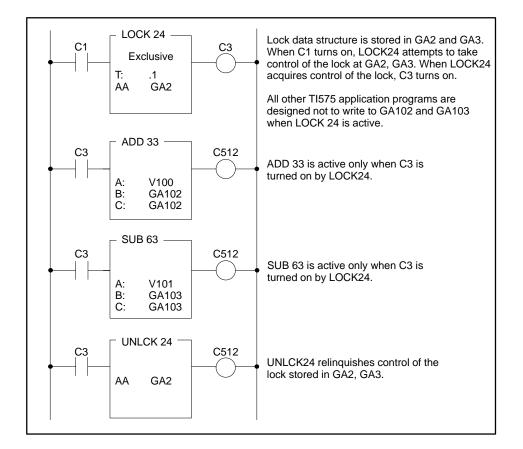

| 6.29 | Lock Memory                                                                                                     | 6-62                 |

|      | LOCK Description                                                                                                | 6-62                 |

|      | Acquiring Control of the Lock                                                                                   | 6-62<br>6-64         |

| ( 20 |                                                                                                                 |                      |

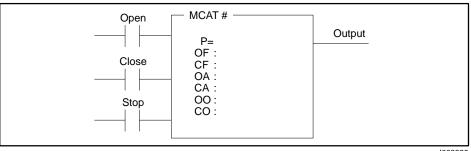

| 6.30 | Motor Control Alarm Timer                                                                                       | <b>6-65</b>          |

|      | MCAT Description                                                                                                | 6-66                 |

|      | MCAT Operation                                                                                                  | 6-68                 |

|      | Open Input Turns On                                                                                             | 6-68                 |

|      | Close Input Turns OnUsing the MCAT Variables                                                                    | 6-68<br>6-69         |

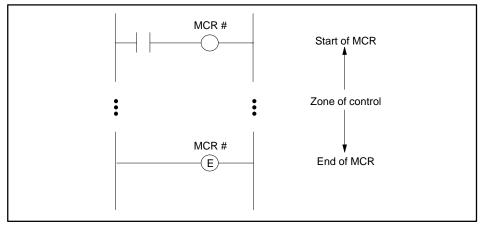

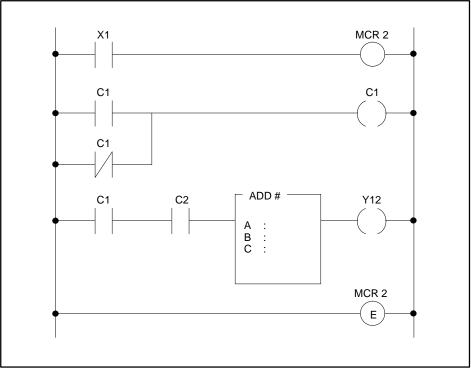

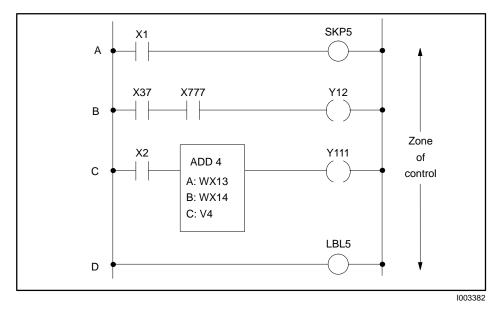

| 6.31 | Master Control Relay                                                                                            | 6-70                 |

|      | MCR Description                                                                                                 | 6-70                 |

|      | MCR/MCRE Operation                                                                                              | 6-70                 |

| 6.32     | Maskable Event Drum, Discrete                                                  | 6-74                 |

|----------|--------------------------------------------------------------------------------|----------------------|

|          | MDRMD Description<br>MDRMD Operation<br>Defining the Mask                      | 6-74<br>6-75<br>6-76 |

|          | Calculating Counts/Step                                                        | 6-76                 |

|          | Timer-triggered Advance Only         Event-triggered Advance Only              | 6-76<br>6-76         |

|          | Timer and Event-Triggered Advance                                              | 6-77                 |

|          | Timer or External Event-triggered Advance                                      | 6-77                 |

| <i>.</i> | Using MDRMD Variables                                                          | 6-77                 |

| 6.33     | Maskable Event Drum, Word                                                      | 6-78                 |

|          | MDRMW Description                                                              | 6-78<br>6-80         |

|          | Defining the Mask                                                              | 6-81                 |

|          | Calculating Counts/Step                                                        | 6-81                 |

|          | Timer-triggered Advance Only                                                   | 6-82                 |

|          | Event-triggered Advance Only         Timer and Event-Triggered Advance         | 6-82<br>6-82         |

|          | Timer or External Event-triggered Advance                                      | 6-82                 |

|          | Using MDRMD Variables                                                          | 6-83                 |

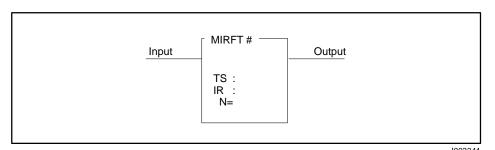

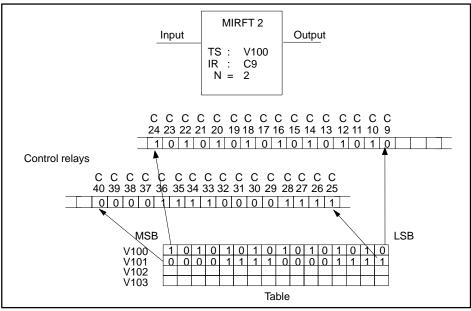

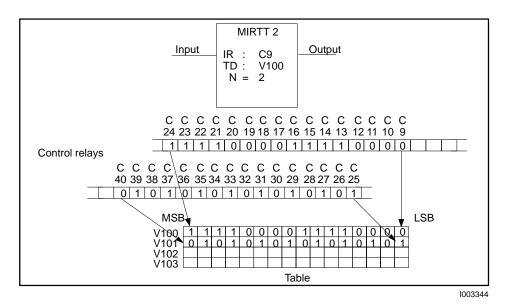

| 6.34     | Move Image Register From Table                                                 | 6-84                 |

|          | MIRFT Description                                                              | 6-84<br>6-84         |

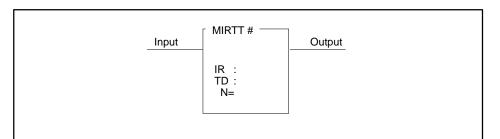

| 6.35     | Move Image Register To Table                                                   | 6-86                 |

|          | MIRTT Description                                                              | 6-86                 |

|          | MIRTT Operation                                                                | 6-86                 |

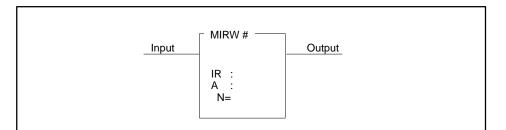

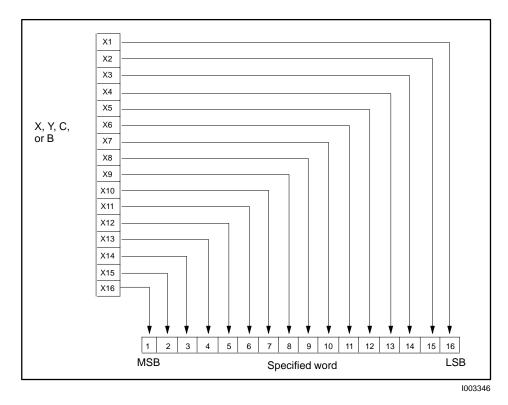

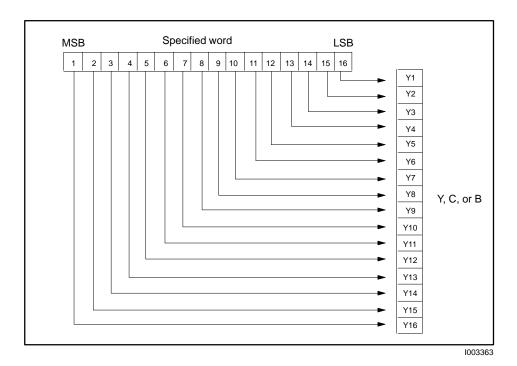

| 6.36     | Move Image Register To Word                                                    | 6-88                 |

|          | MIRW Description                                                               | 6-88                 |

|          | MIRW Operation                                                                 | 6-88                 |

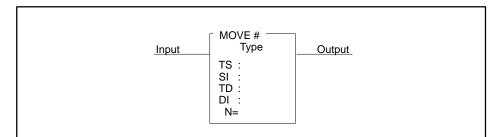

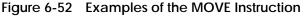

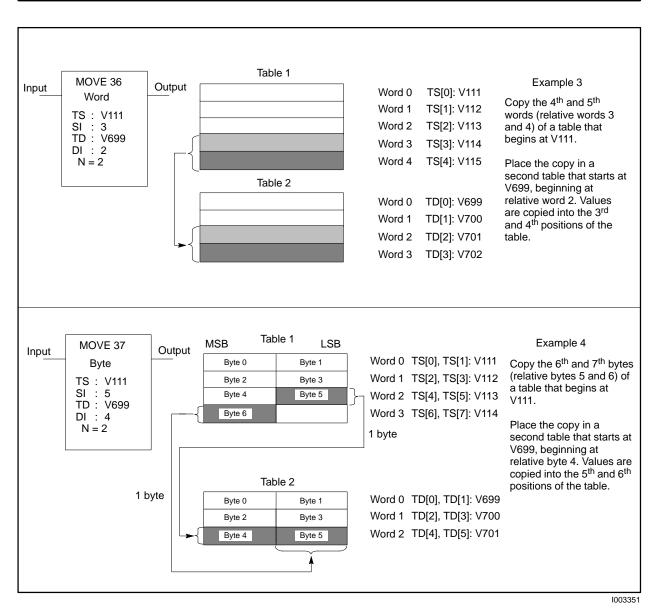

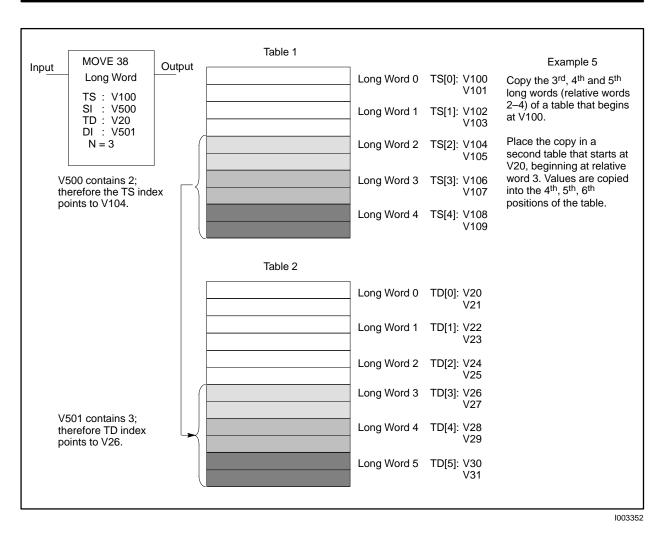

| 6.37     | Move Element                                                                   |                      |

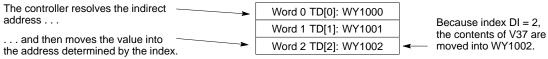

|          | MOVE Description                                                               | 6-90                 |

|          | MOVE Operation                                                                 | 6-91<br>6-91         |

|          | Specifying Source                                                              | 6-92                 |

|          | Specifying Index for Source                                                    | 6-92                 |

|          | Specifying Destination                                                         | 6-93                 |

|          | Specifying Index for Destination         Specifying Number of Elements to Move | 6-93<br>6-94         |

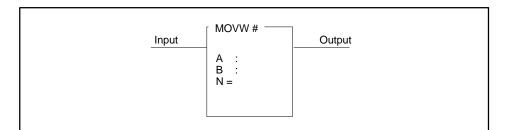

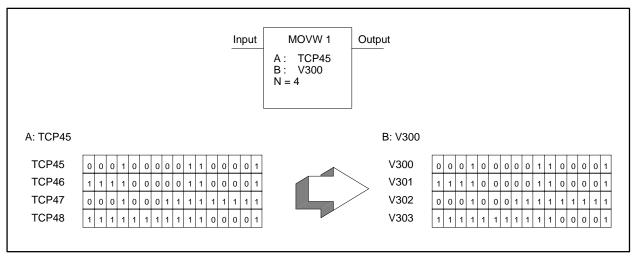

| 6.38     | Move Word                                                                      | 6-98                 |

|          | MOVW Description                                                               | 6-98                 |

|          | MOVW Operation                                                                 | 6-99                 |

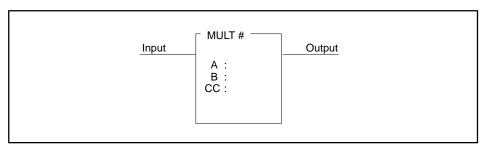

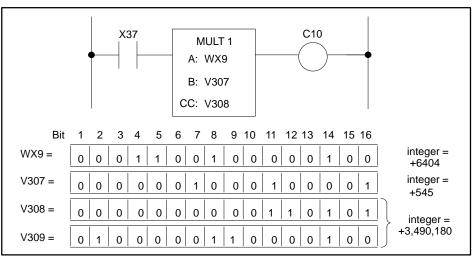

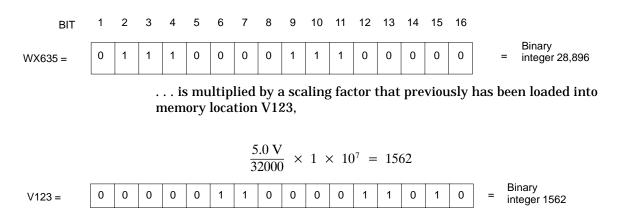

| 6.39 | Multiply                                   | 6-100 |

|------|--------------------------------------------|-------|

|      | MULT Description                           |       |

| 6.40 | Move Word From Table                       | 6-102 |

|      | MWFT Description                           |       |

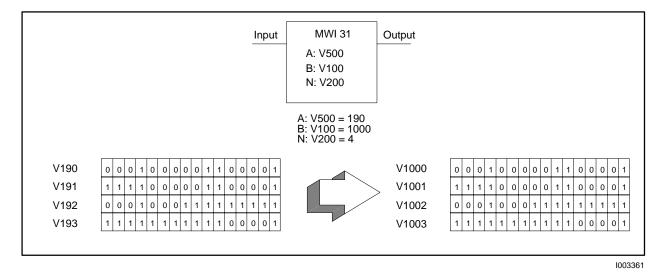

| 6.41 | Move Word with Index                       | 6-104 |

|      | MWI Description                            |       |

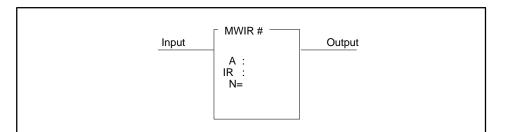

| 6.42 | Move Word to Image Register                | 6-106 |

|      | MWIR Description                           |       |

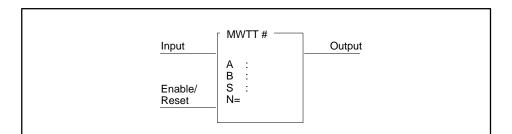

| 6.43 | Move Word to Table                         | 6-108 |

|      | MWTT Description                           |       |

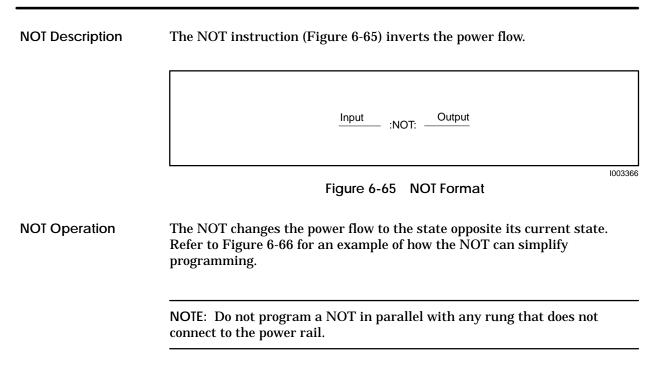

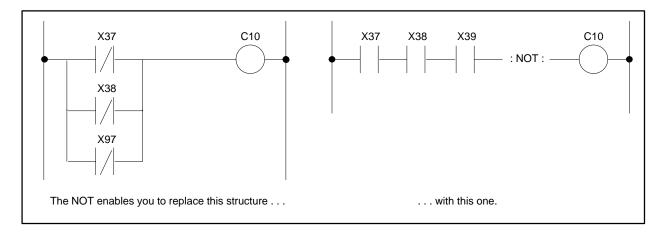

| 6.44 | NOT                                        | 6-110 |

|      | NOT Description                            |       |

| 6.45 | One Shot                                   | 6-111 |

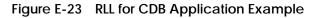

|      | One Shot Description<br>One Shot Operation |       |

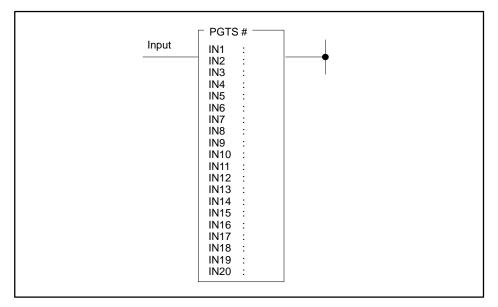

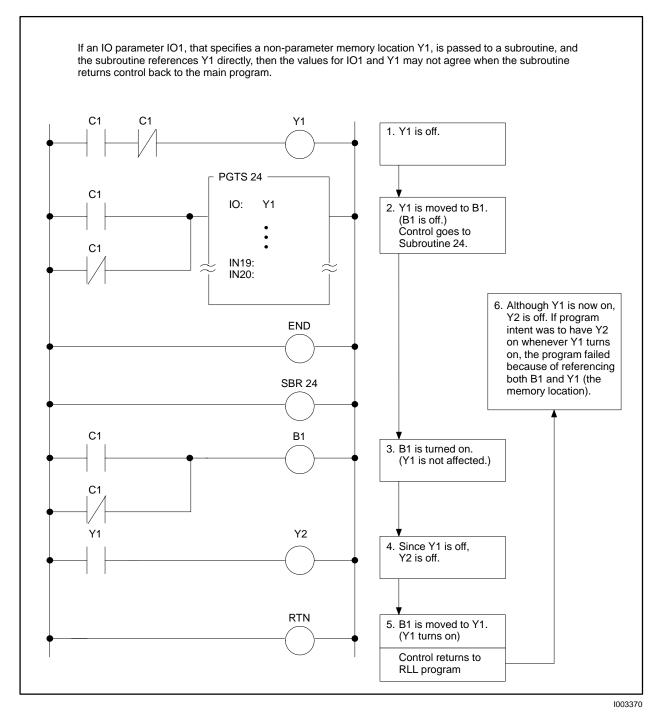

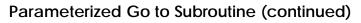

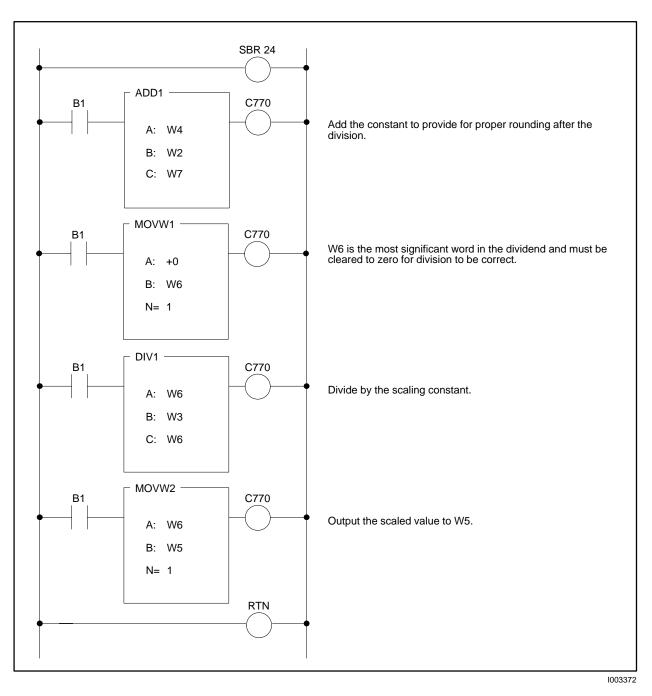

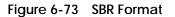

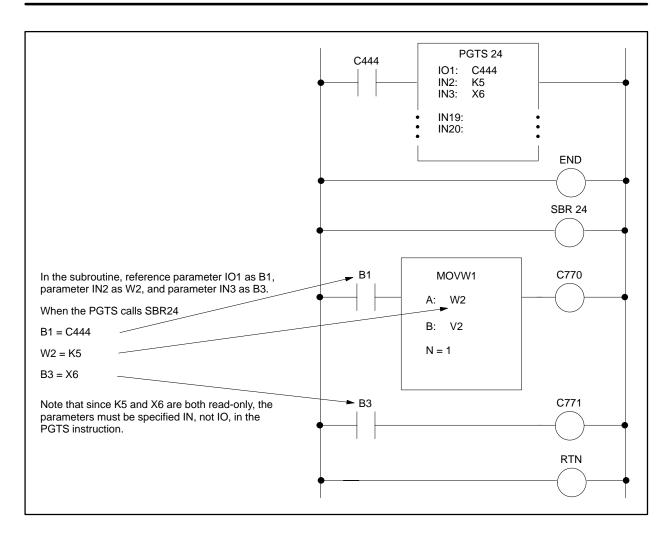

| 6.46 | Parameterized Go To Subroutine             | 6-112 |

|      | PGTS Description                           |       |

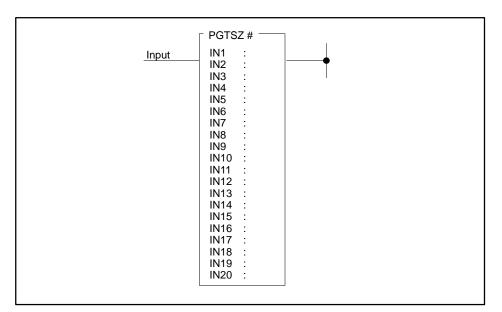

| 6.47 | Parameterized Go To Subroutine (Zero)      | 6-118 |

|      | PGTSZ Description                          |       |

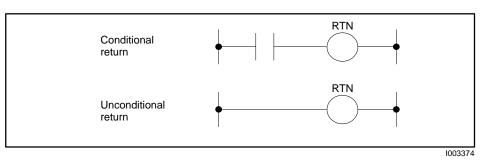

| 6.48 | Return from Subroutine                     | 6-120 |

|      | RTN Description<br>RTN Operation           |       |

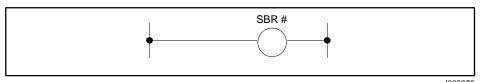

| 6.49 | Subroutine                                 | 6-121 |

|      | SBR Description                            |       |

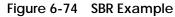

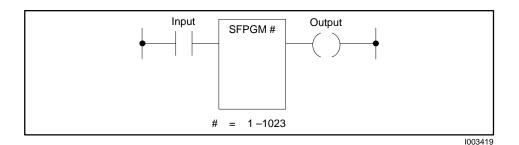

| 6.50 | Call an SF Program                         | 6-124 |

|      | SFPGM Description                          |       |

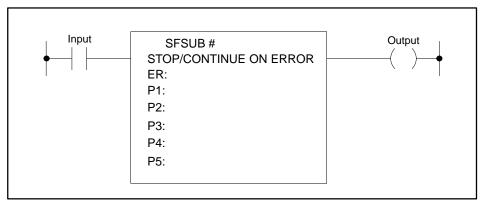

| 6.51 | Call SF Subroutines from RLL               | 6-126 |

|      | SFSUB Description                          |       |

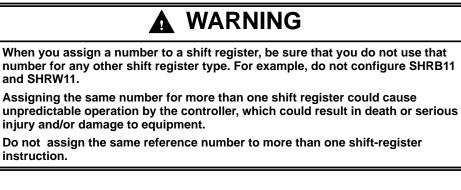

| 6.52 | Bit Shift Register                           | 6-128 |

|------|----------------------------------------------|-------|

|      | SHRB Description                             |       |

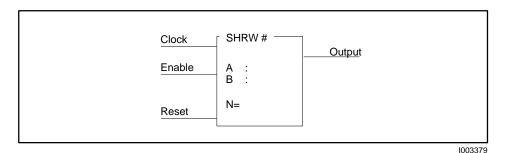

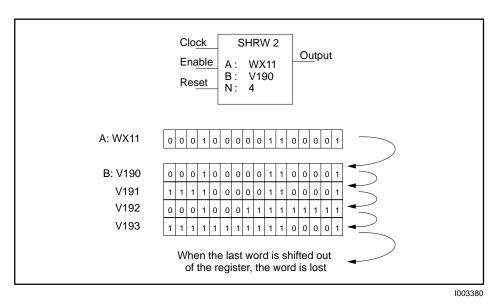

| 6.53 | Word Shift Register                          | 6-130 |

|      | SHRW Description                             |       |

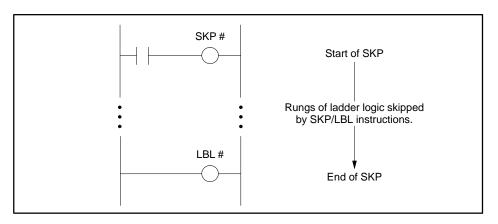

| 6.54 | Skip / Label                                 | 6-132 |

|      | SKP / LBL Description<br>SKP / LBL Operation |       |

| 6.55 | Scan Matrix Compare                          | 6-136 |

|      | SMC Description         SMC Operation        |       |

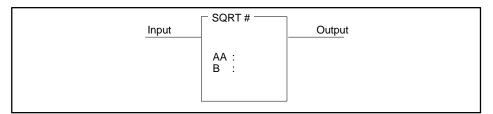

| 6.56 | Square Root                                  | 6-138 |

|      | SQRT Description                             |       |

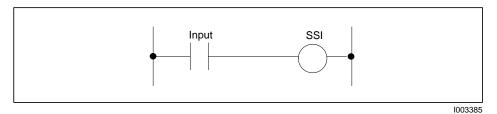

| 6.57 | Scan Synchronization Inhibit                 | 6-140 |

|      | SSI Description                              |       |

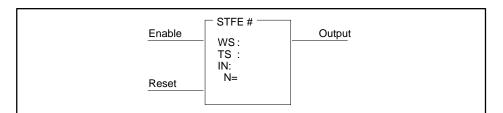

| 6.58 | Search Table for Equal                       | 6-142 |

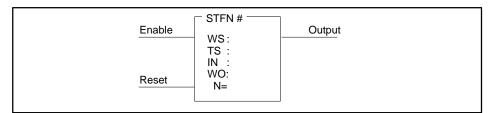

|      | STFE Description                             |       |

| 6.59 | Search Table for Not Equal                   | 6-144 |

|      | STFN Description                             |       |

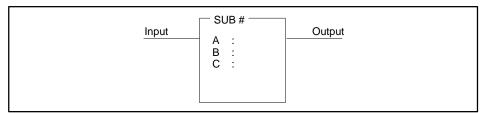

| 6.60 | Subtract                                     | 6-146 |

|      | SUB Description                              |       |

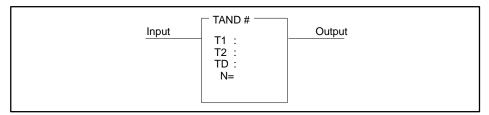

| 6.61 | Table to Table AND                           | 6-147 |

|      | TAND Description         TAND Operation      |       |

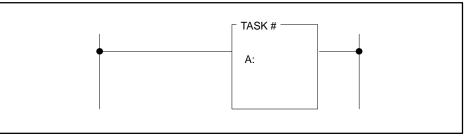

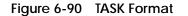

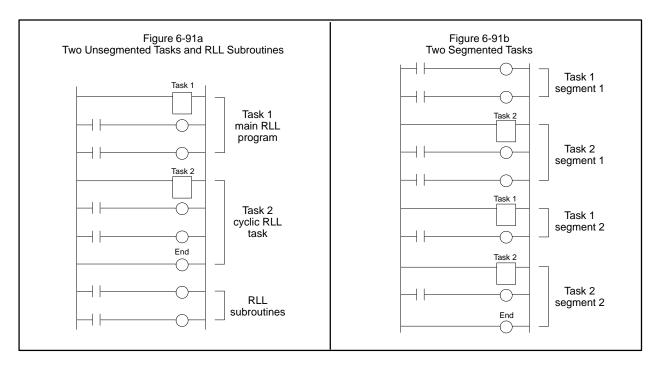

| 6.62 | Start New RLL Task                           | 6-148 |

|      | TASK Description                             |       |

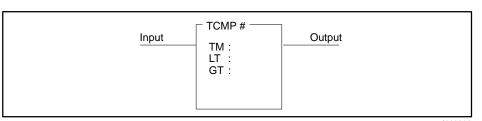

| 6.63 | Time Compare                                 | 6-151 |

|      | TCMP Description                             |       |

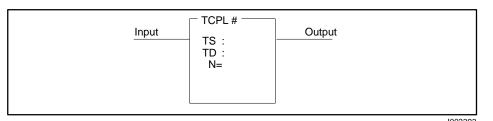

| 6.64 | Table Complement                             | 6-152 |

|      | TCPL Description         TCPL Operation      |       |

| 6.65 | Text                                                                              | 6-153 |

|------|-----------------------------------------------------------------------------------|-------|

|      | Text Box Description                                                              | 6-153 |

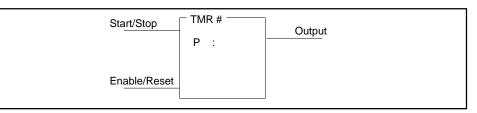

| 6.66 | Timer                                                                             | 6-154 |

|      | TMR/TMRF Description         TMR/TMRF Operation         Using the Timer Variables | 6-154 |

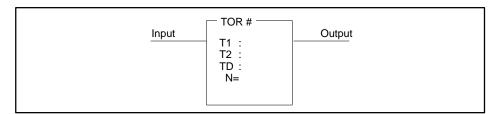

| 6.67 | Table to Table OR                                                                 | 6-156 |

|      | TOR Description                                                                   |       |

| 6.68 | Time Set                                                                          | 6-157 |

|      | TSET Description<br>TSET Operation                                                |       |

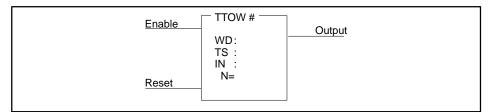

| 6.69 | Table to Word                                                                     | 6-158 |

|      | TTOW Description                                                                  |       |

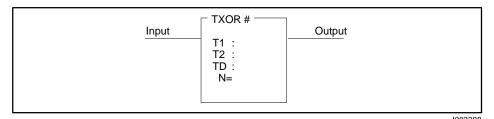

| 6.70 | Table to Table Exclusive OR                                                       | 6-160 |

|      | TXOR Description         TXOR Operation                                           |       |

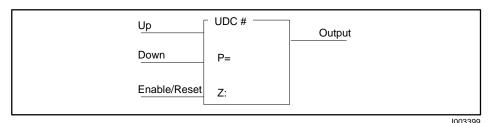

| 6.71 | Up/Down Counter                                                                   | 6-162 |

|      | UDC Description<br>UDC Operation<br>Using the UDC Variables                       | 6-163 |

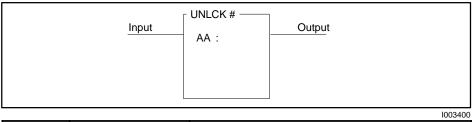

| 6.72 | Unlock Memory                                                                     | 6-164 |

|      | UNLCK Description                                                                 |       |

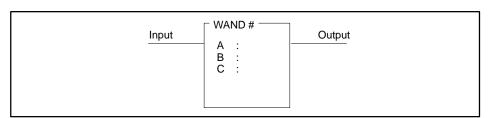

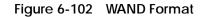

| 6.73 | Word AND                                                                          | 6-166 |

|      | WAND Description                                                                  |       |

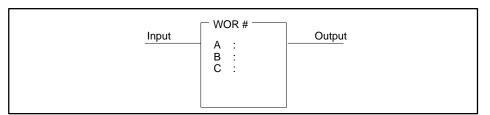

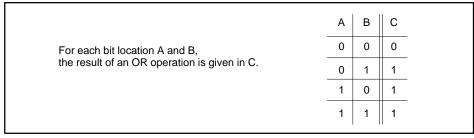

| 6.74 | Word OR                                                                           | 6-168 |

|      | WOR Description                                                                   |       |

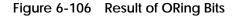

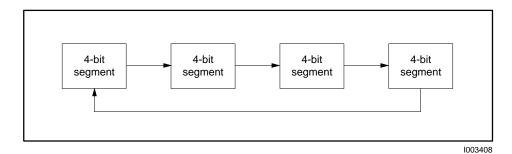

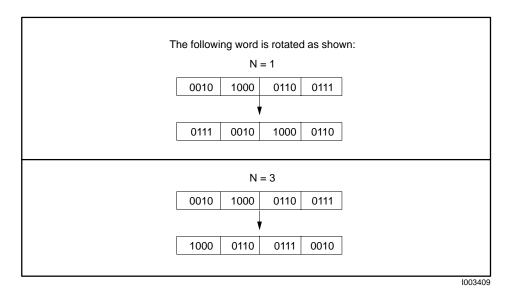

| 6.75 | Word Rotate                                                                       | 6-170 |

|      | WROT Description                                                                  |       |

| 6.76 | Word to Table                                                                     | 6-172 |

|      | WTOT Description                                                                  |       |

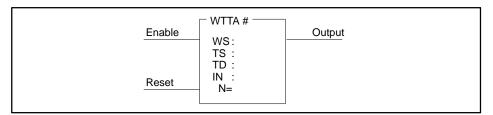

| 6.77 | Word to Table AND                                                                    |              |

|------|--------------------------------------------------------------------------------------|--------------|

|      | WTTA Description                                                                     |              |

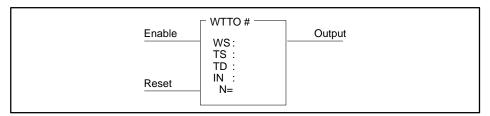

| 6.78 | Word to Table OR                                                                     | 6-176        |

|      | WTTO Description                                                                     |              |

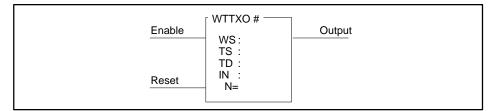

| 6.79 | Word to Table Exclusive OR                                                           | 6-178        |

|      | WTTXO Description                                                                    |              |

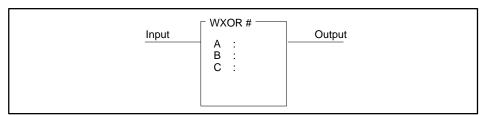

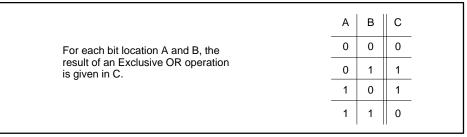

| 6.80 | Word Exclusive OR                                                                    | 6-180        |

|      | WXOR Description                                                                     |              |

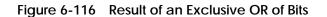

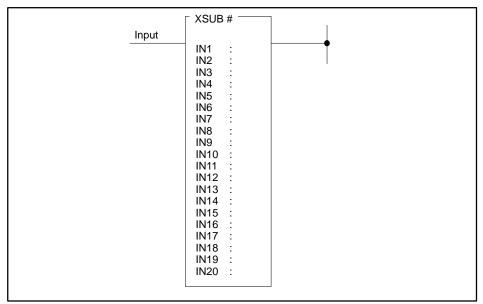

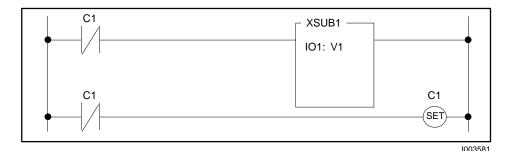

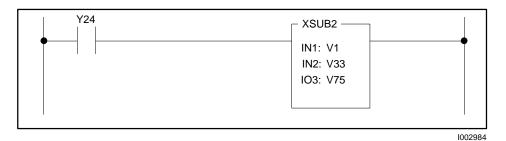

| 6.81 | External Subroutine Call                                                             | 6-182        |

|      | XSUB Description                                                                     |              |

| Chap | oter 7 Special Function Programs                                                     |              |

| 7.1  | Defining Special Function Programs                                                   | 7-2          |

|      |                                                                                      | 7-2          |

|      | Special Function Program Types         SF Programs Called from RLL                   | 7-2<br>7-3   |

|      | SF Programs Called from Loops/Analog Alarms                                          | 7-3          |

| 7.2  | SF Program Statements                                                                | 7-4          |

| 7.3  | Executing Special Function Programs                                                  | 7-5          |

|      | Priority/non-priority SF Programs                                                    | 7-5          |

|      | Cyclic Programs<br>Restricted Programs Called by Loops                               | 7-5<br>7-6   |

|      | Restricted Programs Called by Analog Alarms                                          | 7-7          |

| 7.4  | Executing Special Function Subroutines                                               | 7-8          |

|      | Calling SF Subroutines                                                               | 7-8<br>7-8   |

| 7.5  | Memory Usage by SF Programs                                                          | 7-10         |

| 7.6  | Entering SF Program Header with TISOFT                                               | 7-12         |

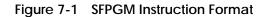

| 7.7  | Reporting SF Program or SFSUB RLL Instruction Errors                                 | 7-14         |

|      | Reporting Errors with the SFEC Variable                                              | 7-14         |

|      | Reporting Errors with Discrete Points           Reporting Errors with V or WY Memory | 7-14<br>7-15 |

| 7.8 | Entering Special Function Programming Statements | 7-16 |

|-----|--------------------------------------------------|------|

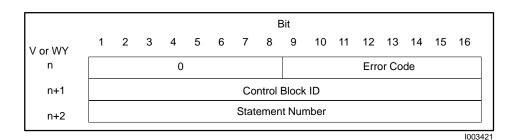

| 7.9  | Convert BCD to Binary                      | 7-18         |

|------|--------------------------------------------|--------------|

|      | BCDBIN DescriptionBCDBIN Operation         | 7-18<br>7-18 |

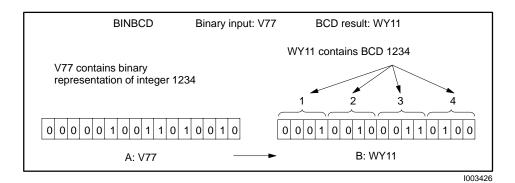

| 7.10 | Convert Binary Inputs to BCD               | 7-19         |

|      | BINBCD Description                         | 7-19<br>7-19 |

| 7.11 | Call Subroutine                            | 7-20         |

|      | CALL Description CALL Operation            | 7-20<br>7-20 |

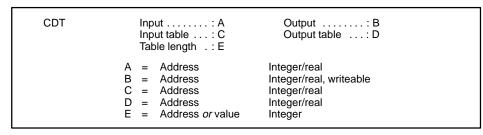

| 7.12 | Correlated Data Table                      | 7-22         |

|      | CDT Description<br>CDT Operation           | 7-22<br>7-23 |

| 7.13 | Exit on Error                              | 7-24         |

|      | EXIT Description                           | 7-24<br>7-24 |

| 7.14 | Fall Through Shift Register—Input          | 7-25         |

|      | FTSR-IN Description<br>FTSR-IN Operation   | 7-25<br>7-26 |

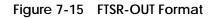

| 7.15 | Fall through Shift Register—Output         | 7-29         |

|      | FTSR-OUT Description<br>FTSR-OUT Operation | 7-29<br>7-30 |

| 7.16 | Go To/Label Function                       | 7-33         |

| 7.17 | IF/THEN/ELSE Functions                     | 7-34         |

|      | IF/THEN/ELSE DescriptionIF Operation       | 7-34<br>7-35 |

| 7.18 | Integer Math Operations                    | 7-36         |

|      | IMATH Description                          | 7-36         |

|      | IMATH Operation                            | 7-36         |

| 7.19 | Lead/Lag Operation                         | 7-38         |

|      | LEAD/LAG DescriptionLEAD/LAG Operation     | 7-38<br>7-39 |

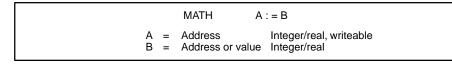

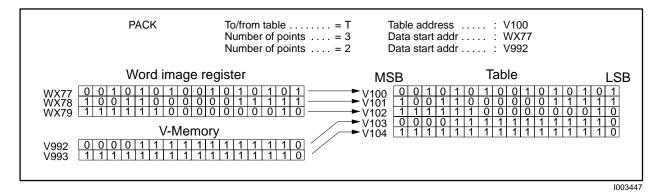

| 7.20 | Real/Integer Math Operations               | 7-40         |

|      | MATH Description                           | 7-40         |

|      | MATH OperationUsing Offset Indexing        | 7-41<br>7-43 |

|      | Using Element Indexing                     | 7-43         |

|      | Indexing Loop and Analog Alarm Variables   | 7-43         |

|      | Using Multiple Subscripts                  | 7-44<br>7-44 |

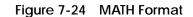

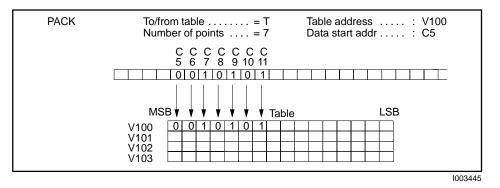

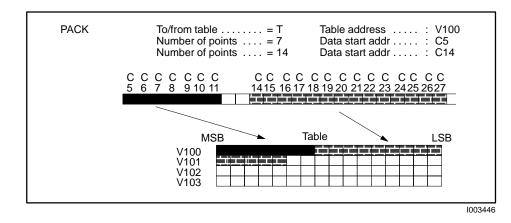

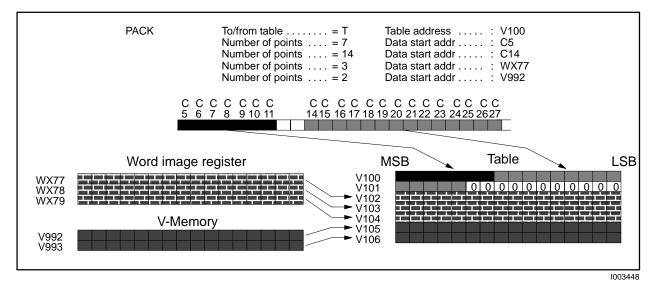

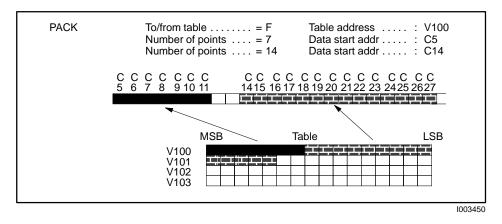

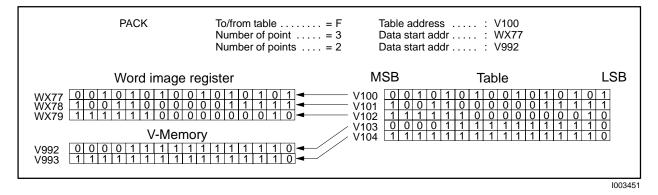

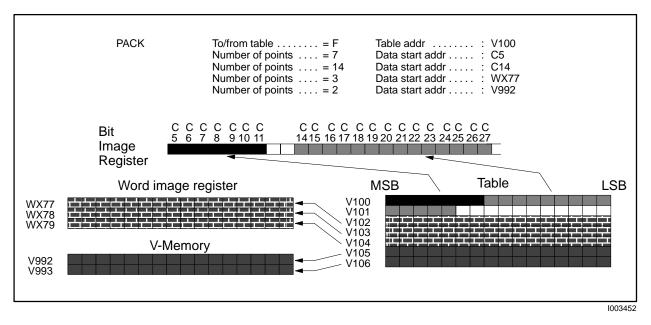

| 7.21 | Pack Data                                                    | 7-45                 |

|------|--------------------------------------------------------------|----------------------|

|      | PACK Description<br>PACK TO Operation<br>PACK FROM Operation | 7-45<br>7-46<br>7-48 |

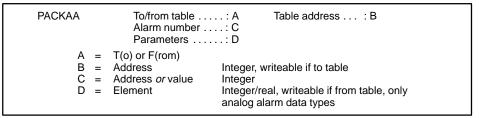

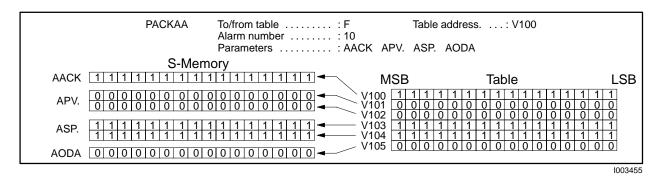

| 7.22 | Pack Analog Alarm Data                                       | 7-51                 |

| ,    | PACKAA Description PACKAA Operation                          | 7-51<br>7-52         |

| 7.23 | Pack Loop Data                                               | 7-54                 |

|      | PACKLOOP Description PACKLOOP Operation                      | 7-54<br>7-54         |

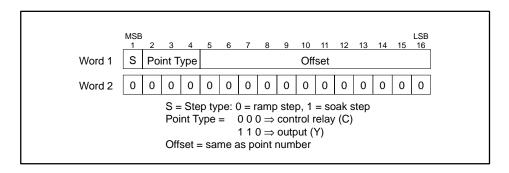

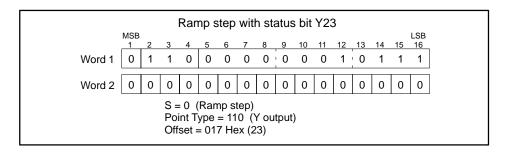

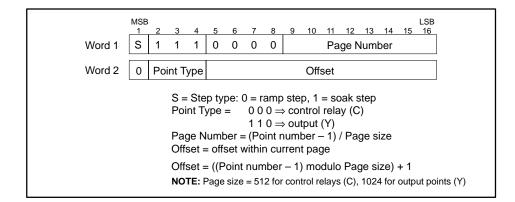

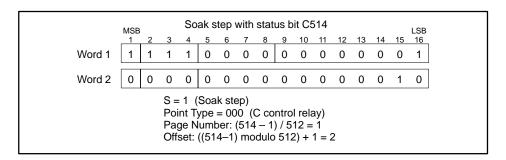

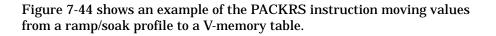

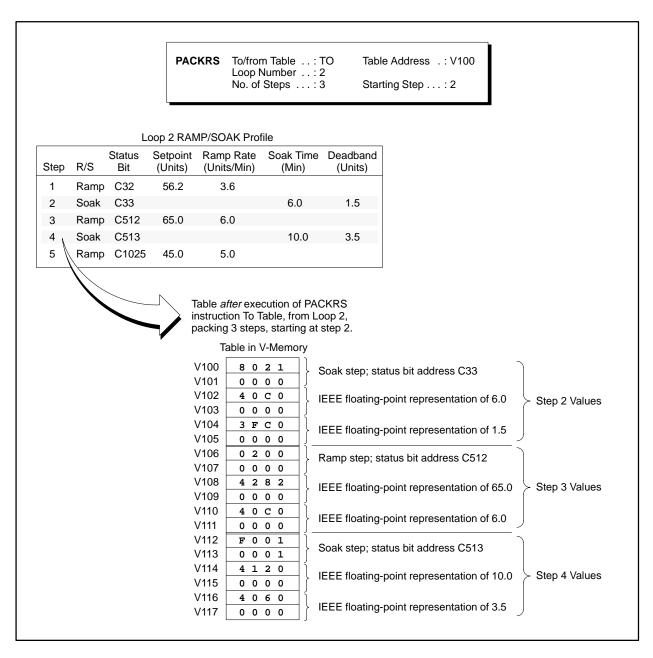

| 7.24 | Pack Ramp/Soak Data                                          | 7-56                 |

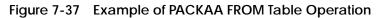

|      | PACKRS Description PACKRS Operation                          | 7-56<br>7-56         |

| 7.25 | Printing                                                     | 7-62                 |

|      | PRINT Description                                            | 7-62<br>7-62         |

| 7.26 | Return from SF Program/Subroutine                            | 7-65                 |

| 7.27 | Scaling Values                                               | 7-66                 |

|      | SCALE DescriptionSCALE Operation                             | 7-66<br>7-67         |

| 7.28 | Sequential Data Table                                        | 7-68                 |

|      | SDT Description                                              | 7-68<br>7-68         |

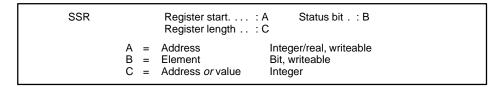

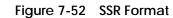

| 7.29 | Synchronous Shift Register                                   | 7-70                 |

|      | SSR Description                                              | 7-70<br>7-70         |

| 7.30 | Unscaling Values                                             | 7-72                 |

|      | UNSCALE Description                                          | 7-72<br>7-72         |

| 7.31 | Comment                                                      | 7-74                 |

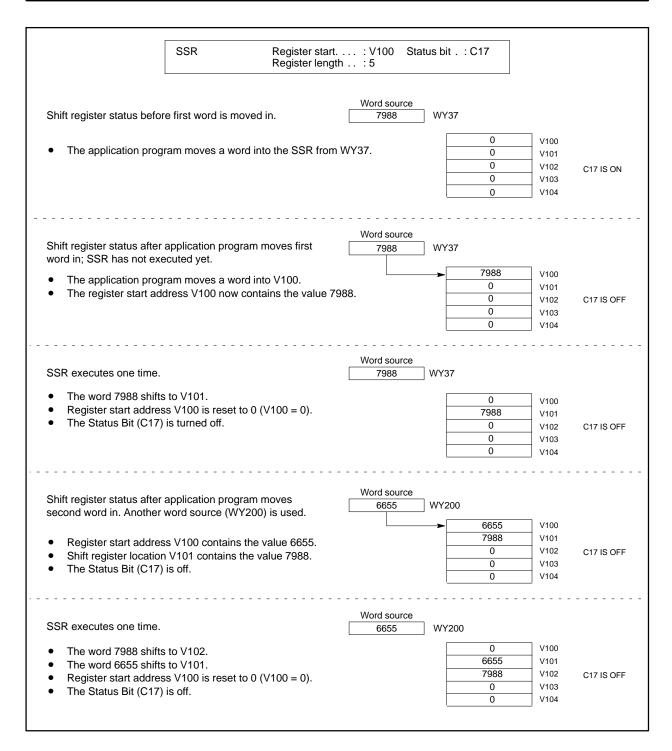

| Chap | oter 8 Programming Analog Alarms                             |                      |

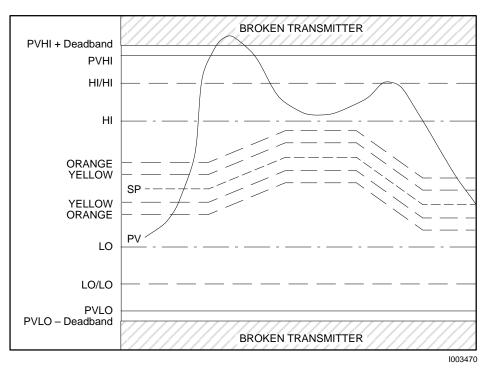

| 8.1  | Overview                                                     | 8-2                  |

| 8.2  | Analog Alarm Programming and Structure                       | 8-4                  |

|      | Analog Alarm Numbers and Variable Names                      | 8-4                  |

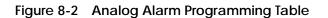

|      | Programming Tables                                           | 8-4<br>8-5           |

| 8.3  | Specifying Analog Alarm V-Flag Address                                                                                                                | <b>8-6</b><br>8-6                      |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 8.4  | Specifying Analog Alarm Sample Rate                                                                                                                   | <b>8-7</b><br>8-7                      |

| 8.5  | Specifying Analog Alarm Process Variable Parameters<br>Process Variable Address<br>PV Range Low/High<br>PV is Bipolar 20% Offset<br>Square Root of PV | <b>8-8</b><br>8-8<br>8-8<br>8-8<br>8-8 |

| 8.6  | Specifying Analog Alarm Deadband                                                                                                                      | <b>8-9</b><br>8-9                      |

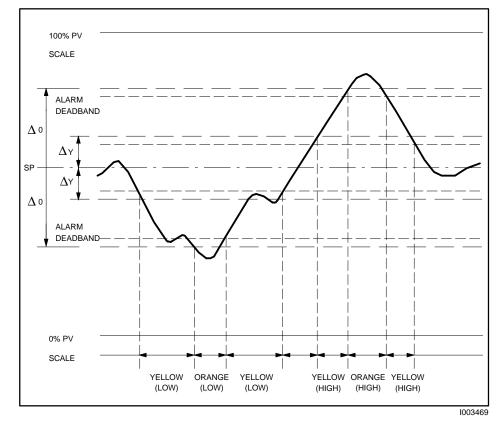

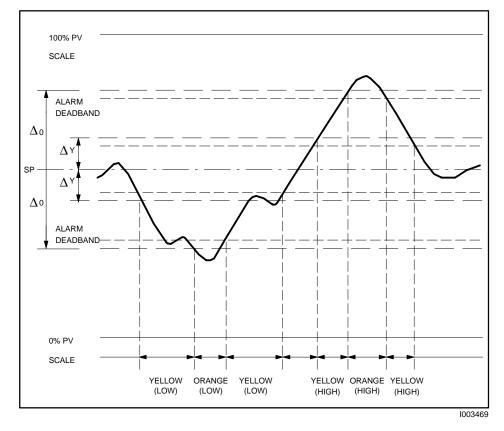

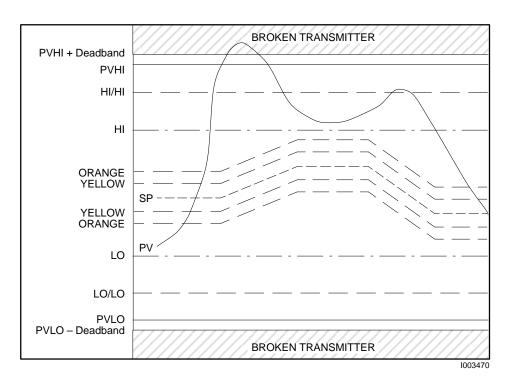

| 8.7  | Specifying Analog Alarm Process Variable Alarm Limits<br>PV Alarms: Low-low, Low, High, High-high                                                     | <b>8-10</b><br>8-10                    |

| 8.8  | Specifying Analog Alarm Setpoint Parameters                                                                                                           | <b>8-11</b><br>8-11<br>8-11            |

| 8.9  | Specifying Analog Alarm Special Function Call                                                                                                         | <b>8-12</b><br>8-12                    |

| 8.10 | Specifying Analog Alarm Setpoint Deviation Limits                                                                                                     | <b>8-13</b><br>8-13                    |

| 8.11 | Specifying Other Analog Alarm Process Variable Alarms<br>Rate of Change Alarm<br>Broken Transmitter Alarm                                             | <b>8-14</b><br>8-14<br>8-14            |

| Cha  | oter 9 Programming Loops                                                                                                                              |                                        |

| 9.1  | Overview                                                                                                                                              | 9-2                                    |

| 9.2  | Using the PID Loop Function<br>Manual Mode<br>Auto Mode<br>Cascade Mode<br>Changing Loop Mode                                                         | <b>9-4</b><br>9-4<br>9-4<br>9-5        |

| 9.3  | Loop Algorithms<br>PID Position Algorithm<br>PID Velocity Algorithm                                                                                   | <b>9-6</b><br>9-6<br>9-7               |

| 9.4  | Programming Loops                                                                                                                                     | <b>9-8</b><br>9-8<br>9-8<br>9-9        |

| 9.5  | Specifying Loop PID Algorithm<br>Pos/Vel PID Algorithm                                                                                                        | <b>9-10</b><br>9-10                                         |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 9.6  | Specifying LOOP VFLAG ADDRESS                                                                                                                                 | <b>9-11</b><br>9-11                                         |

| 9.7  | Specifying Loop Sample Rate                                                                                                                                   | <b>9-12</b><br>9-12                                         |

| 9.8  | Specifying Loop Process Variable ParametersProcess Variable AddressPV Range Low/highPV is Bipolar 20% OffsetSquare Root of PV                                 | <b>9-13</b><br>9-13<br>9-13<br>9-13<br>9-13                 |

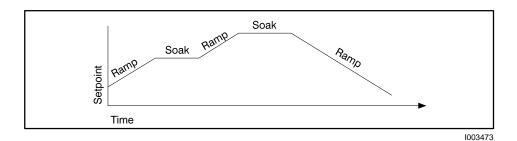

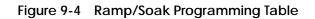

| 9.9  | Specifying Loop Ramp/Soak ProfileDefining Ramp/Soak OperationDefining Ramp/Soak StepsControlling the Ramp/Soak OperationRamp/Soak for SPProgramming Ramp/Soak | <b>9-14</b><br>9-14<br>9-14<br>9-16<br>9-16                 |

| 9.10 | Specifying Loop Output Parameters         Loop Output Address         Output is Bipolar         20% Offset on Output                                          | <b>9-18</b><br>9-18<br>9-18<br>9-18                         |

| 9.11 | Specifying Loop Alarm Deadband                                                                                                                                |                                                             |

| 9.12 | Specifying Loop Process Variable Alarm Limits<br>PV Alarms Low-low, Low-high, High-high                                                                       | <b>9-20</b><br>9-20                                         |

| 9.13 | Specifying Loop Setpoint Parameters         Remote Setpoint         Clamp SP Limits                                                                           | <b>9-21</b><br>9-21<br>9-21                                 |

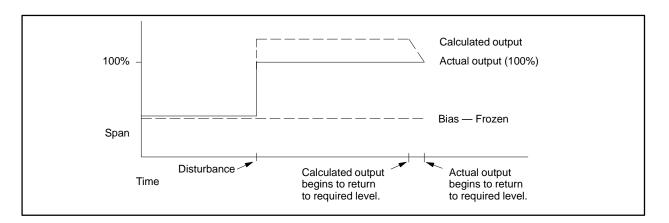

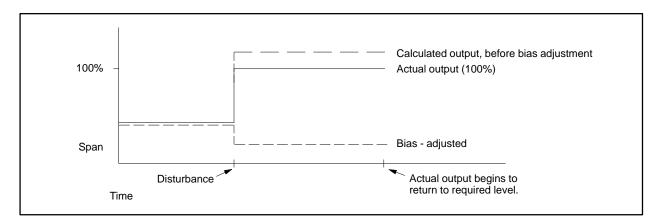

| 9.14 | Specifying Loop Tuning ParametersLoop Gain, Reset, RateRemoving Integral ActionRemoving Derivative ActionRemoving Proportional ActionFreeze BiasAdjust Bias   | <b>9-22</b><br>9-22<br>9-22<br>9-22<br>9-22<br>9-23<br>9-24 |

| 9.15 | Specifying Loop Derivative Gain Limiting                                                                                                                      | <b>9-25</b><br>9-25                                         |

| 9.16 | Specifying Loop Special Function Call                                                                                                          | 9-26                         |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

|      | Special Calculation/ Special FunctionCalculation Scheduled on SetpointCalculation Scheduled on Process VariableCalculation Scheduled on Output | 9-26<br>9-26<br>9-26<br>9-27 |

| 9.17 | Specifying Loop Locked Changes                                                                                                                 |                              |

|      | Lock Setpoint, Auto/Manual, Cascade                                                                                                            | 9-28                         |

| 9.18 | Specifying Loop Error Operation                                                                                                                | 9-29                         |

|      | Error Operation<br>Error Deadband<br>No Error Calculation                                                                                      | 9-29<br>9-29<br>9-29         |

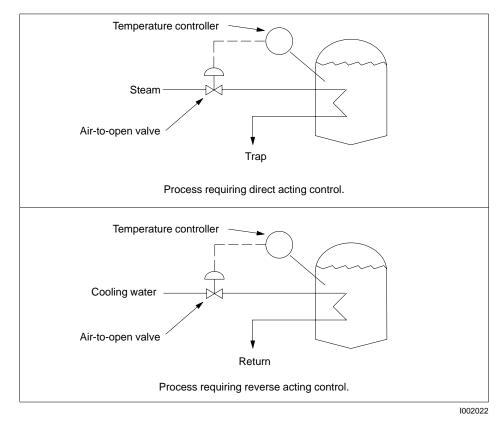

| 9.19 | Specifying Reverse Acting Loops                                                                                                                | 9-30                         |

|      | Reverse Acting<br>Direct-Acting Loop<br>Reverse-Acting Loop                                                                                    | 9-30<br>9-30<br>9-30         |

| 9.20 | Specifying Loop Setpoint Deviation Limits                                                                                                      | 9-31                         |

|      | Deviation Alarms Yellow, Orange                                                                                                                | 9-31                         |

| 9.21 | Specifying Other Loop Process Variable Alarms                                                                                                  | 9-32                         |

|      | Rate of Change Alarm<br>Broken Transmitter Alarm                                                                                               | 9-32<br>9-32                 |

| Appe | endix A Memory and Variable Types                                                                                                              |                              |

| A.1  | RLL Variable Access (TI545, TI555, TI560, TI575)                                                                                               | A-2                          |

| A.2  | SF Program Variable Access (TI545, TI555, TI565, TI575)                                                                                        | A-3                          |

| A.3  | RLL Variable Access — Early Model Controllers                                                                                                  | A-9                          |

| Арре | endix B RLL Memory Requirements                                                                                                                |                              |

| B.1  | Memory Requirements                                                                                                                            | B-2                          |

| Арре | endix C Controller Performance                                                                                                                 |                              |

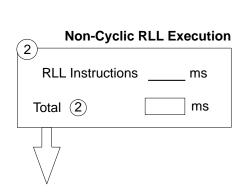

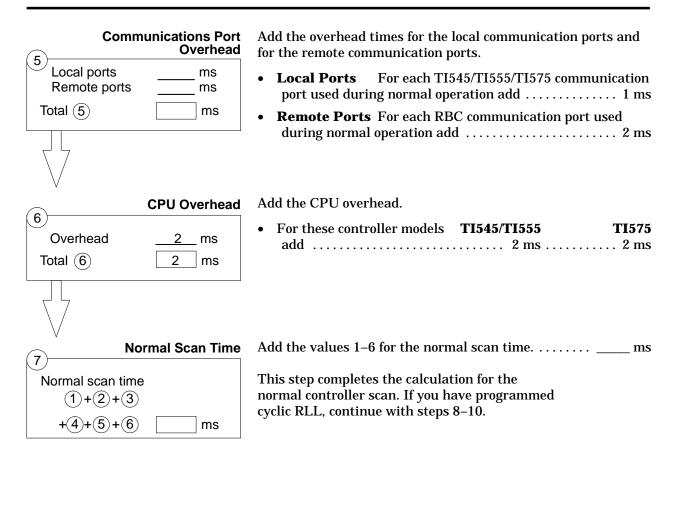

| C.1  | Calculating Performance for the TI545, TI555, and TI575                                                                                        | C-2                          |

|      | Calculating Normal Scan Time<br>Calculating the Cyclic RLL Execution Time<br>Total Scan Time Including Cyclic RLL                              | C-2<br>C-4<br>C-5            |

| C.2  | Tuning the TI545/TI555/TI575 Timeline                                                                                                          | C-8                          |

|      | Basic Strategy<br>Using Peak Elapsed Time Words<br>Using the Status Words<br>Concepts to Remember When Calculating Timeline                    | C-8<br>C-8<br>C-9<br>C-10    |

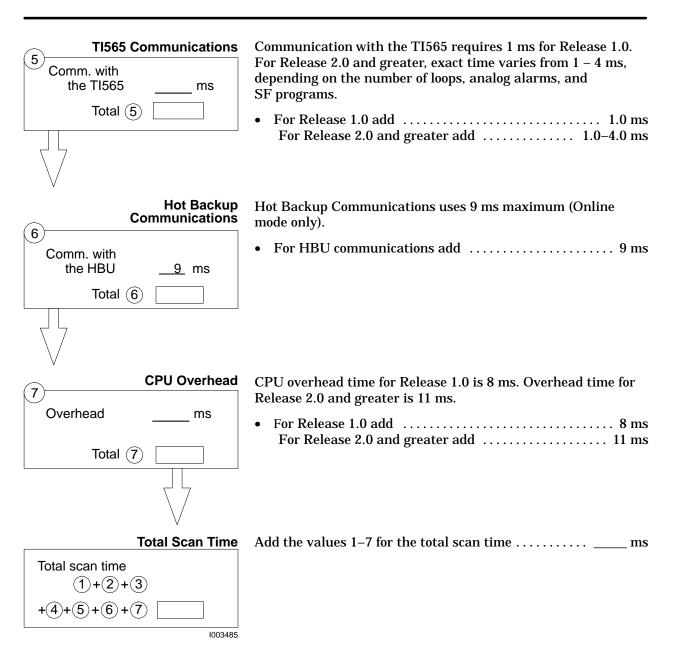

| C.3 | Calculating Performance for the TI560                                                   | C-12                |

|-----|-----------------------------------------------------------------------------------------|---------------------|

|     | Calculating Scan Time<br>RCC Performance<br>TI565 Performance<br>Hot Backup Performance |                     |

| C.4 | RLL Execution Times for High-End Controllers                                            | C-16                |

| C.5 | SF Program Statement Execution Times for the TI545/TI555/TI575                          | C-21                |

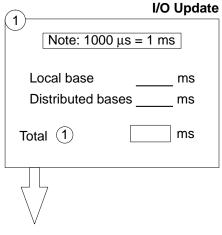

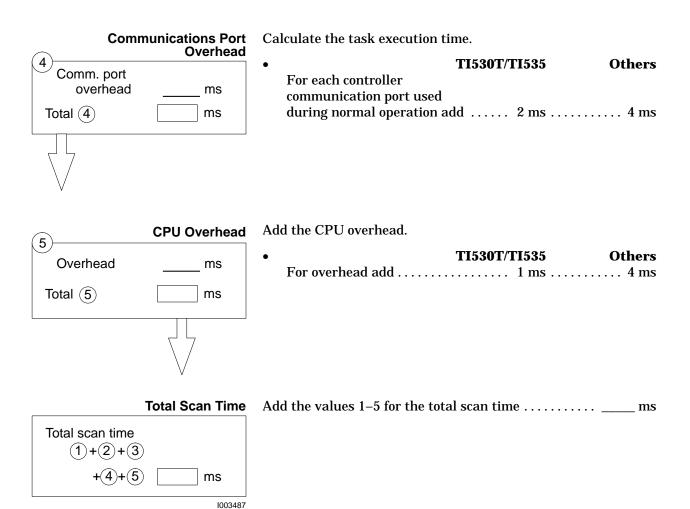

| C.6 | Calculating Performance for the TI520C, TI530C, TI530T, TI525, and TI535                | <b>C-24</b><br>C-24 |

| Арр | endix D Loop and Analog Alarm Flag Formats                                              |                     |

| D.1 | Loop Flags                                                                              | D-2                 |

| D.2 | Analog Alarm Flags                                                                      | D-4                 |

| Арр | endix E Selected Application Examples                                                   |                     |

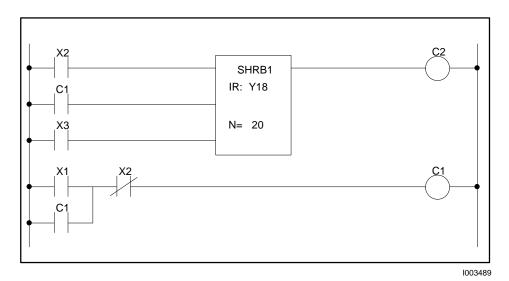

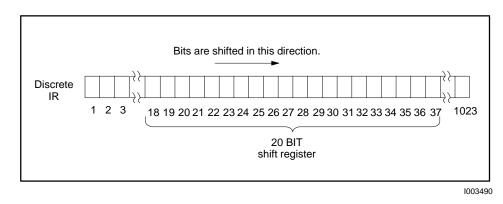

| E.1 | Using the SHRB                                                                          | E-2                 |

|     | SHRB Application Example                                                                | E-2<br>E-2          |

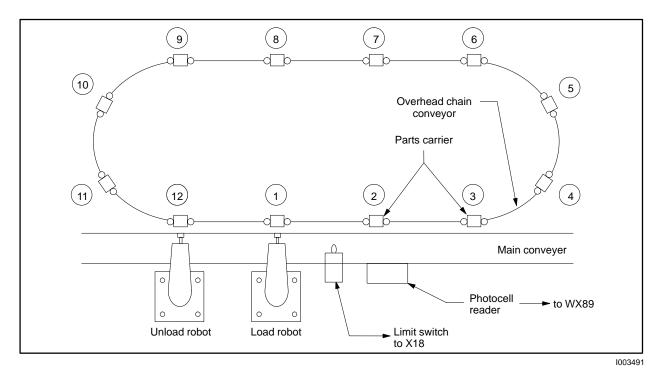

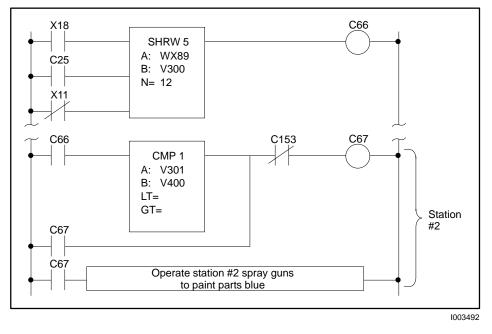

| E.2 | Using the SHRW                                                                          | E-4                 |

|     | SHRW Application Example Explanation                                                    | E-4<br>E-5          |

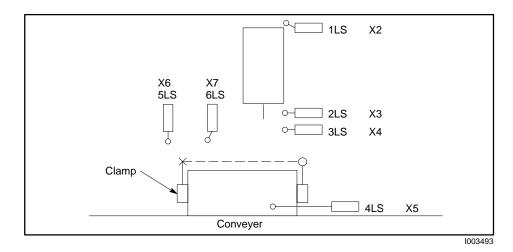

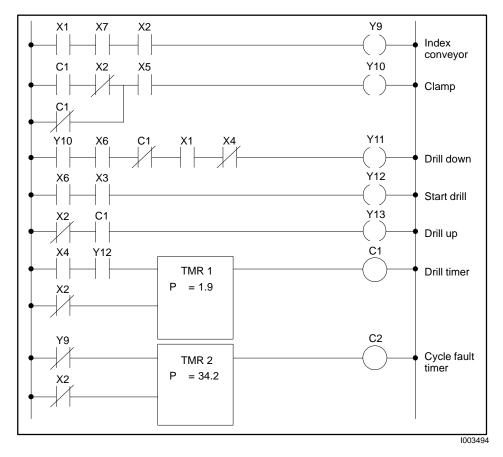

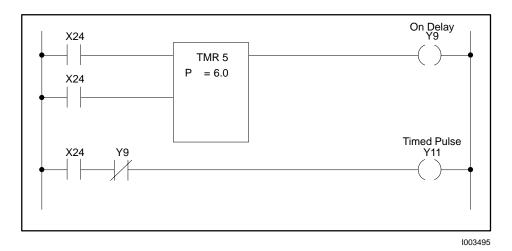

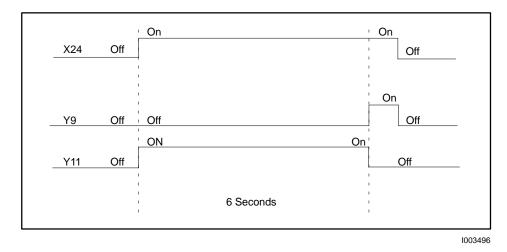

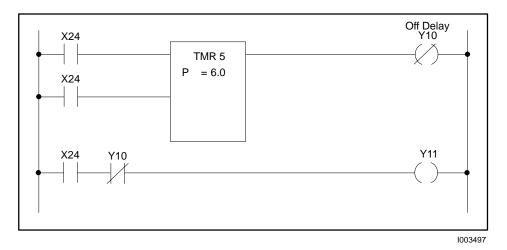

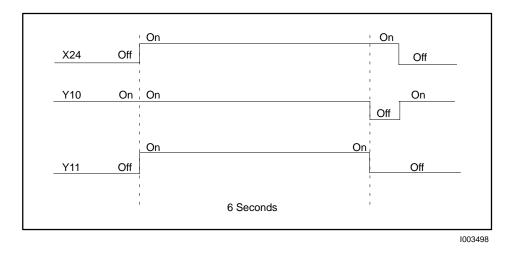

| E.3 | Using the TMR                                                                           | E-6                 |

|     | TMR Application Example #1                                                              | E-6                 |

|     | Explanation #1                                                                          | E-6<br>E-8          |

|     | Application #3                                                                          | E-9                 |

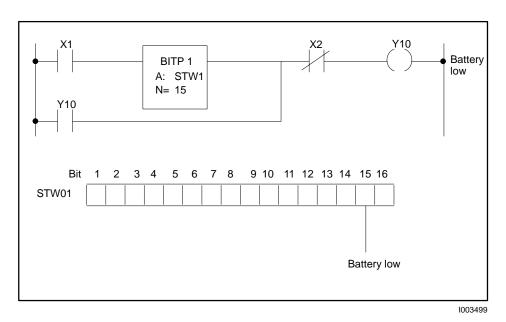

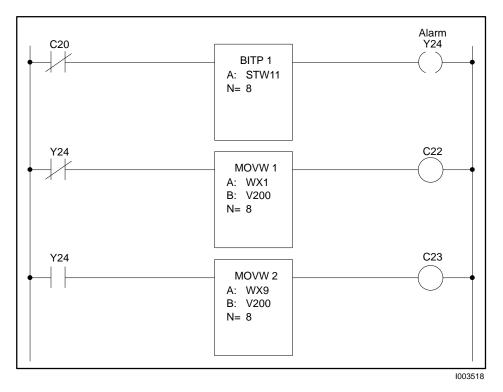

| E.4 | Using the BITP                                                                          | E-10                |

|     | BITP Application Example                                                                | E-10<br>E-10        |

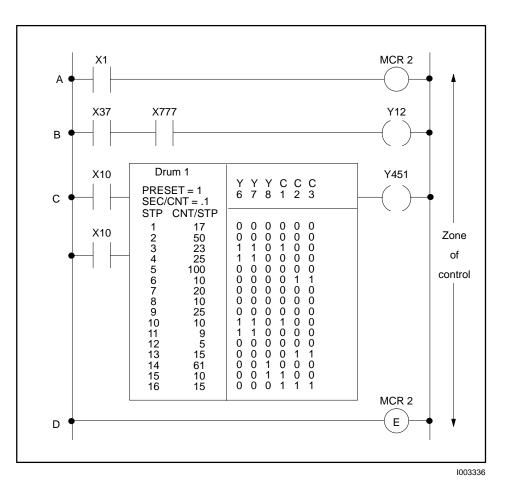

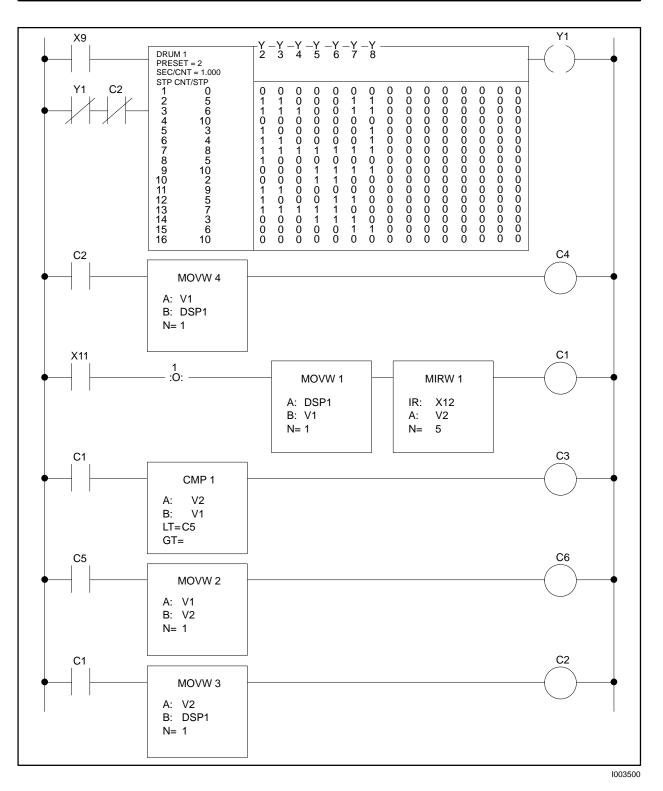

| E.5 | Using the DRUM                                                                          | E-12                |

|     | DRUM Application Example                                                                | E-12<br>E-12        |

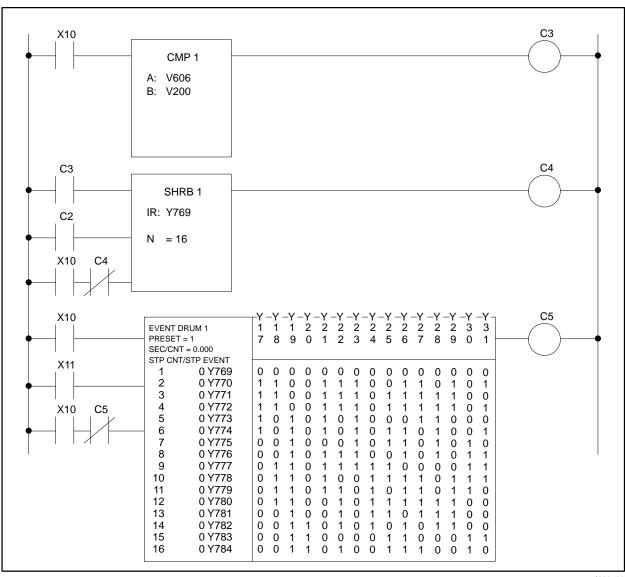

| E.6 | Using the EDRUM                                                                         | E-14                |

|     | EDRUM Application Example                                                               | E-14<br>E-14        |

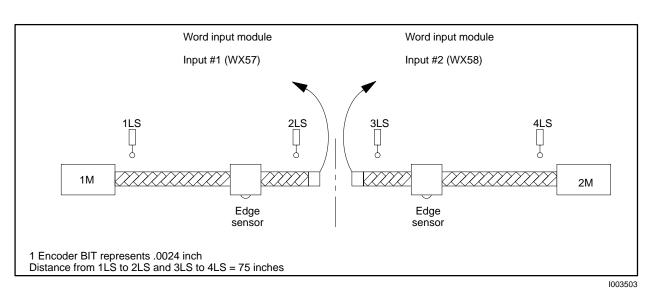

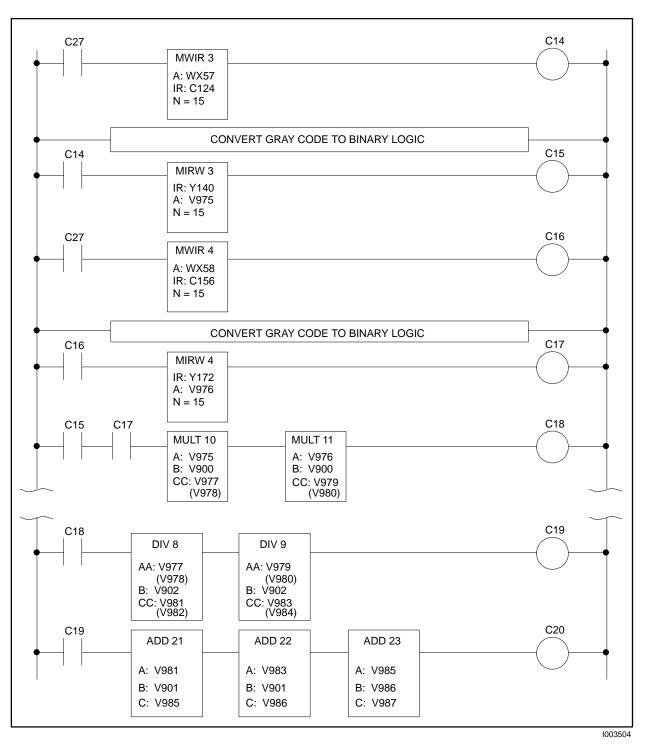

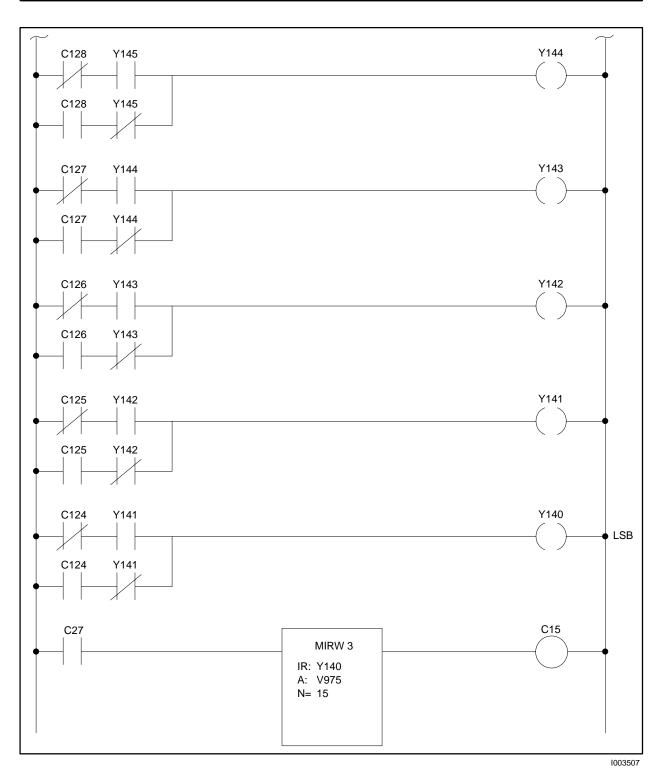

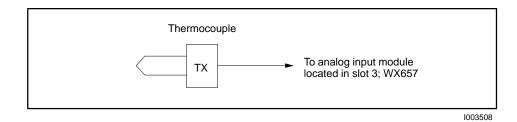

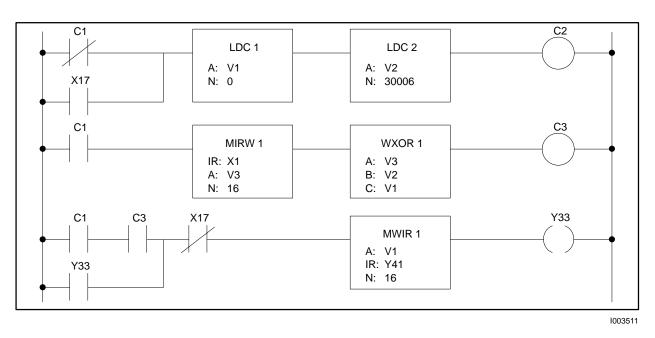

| E.7 | Using the MIRW                                                                          | E-18                |

|     | Application<br>Explanation                                                              | E-18<br>E-20        |

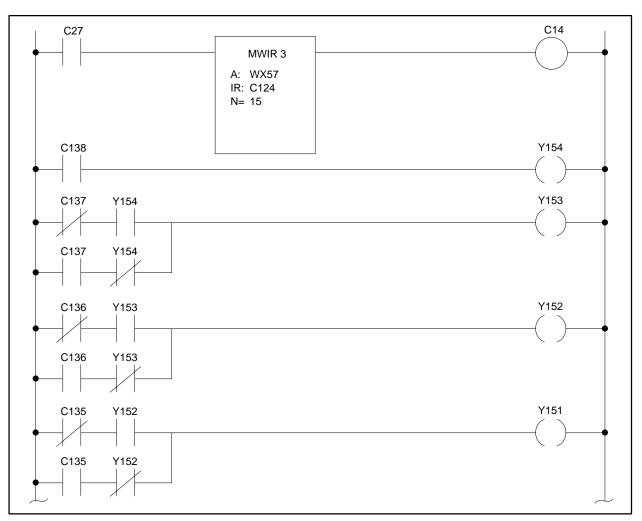

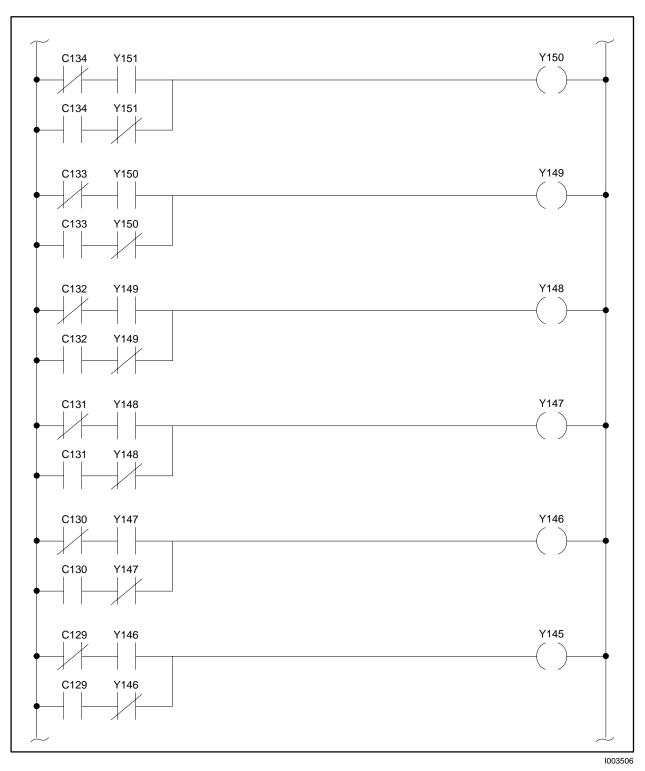

| E.8  | Using the MWIR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>E-22</b><br>E-22<br>E-22                  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

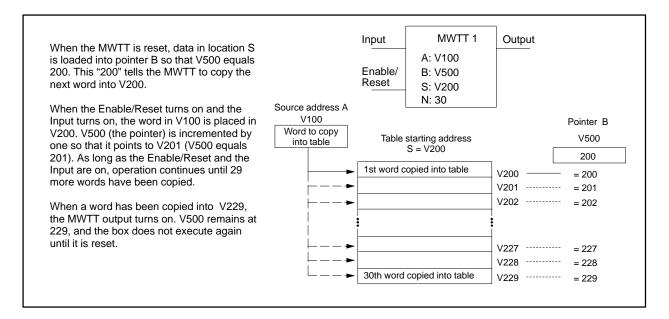

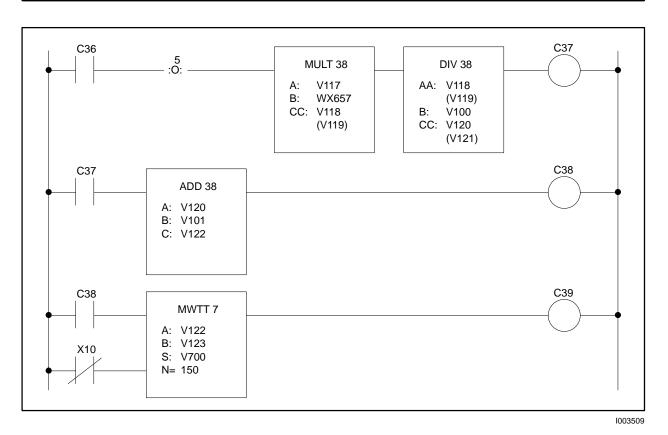

| E.9  | Using the MWTT<br>Application<br>Explanation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>E-26</b><br>E-26<br>E-26                  |

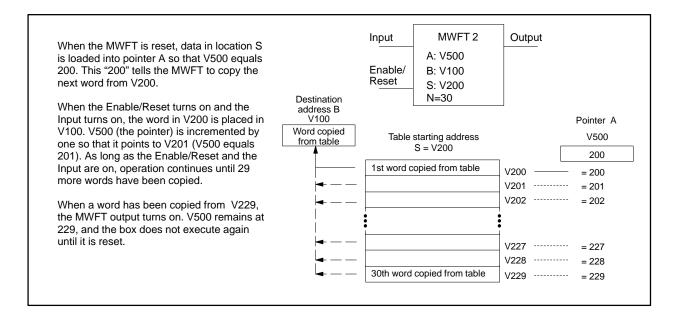

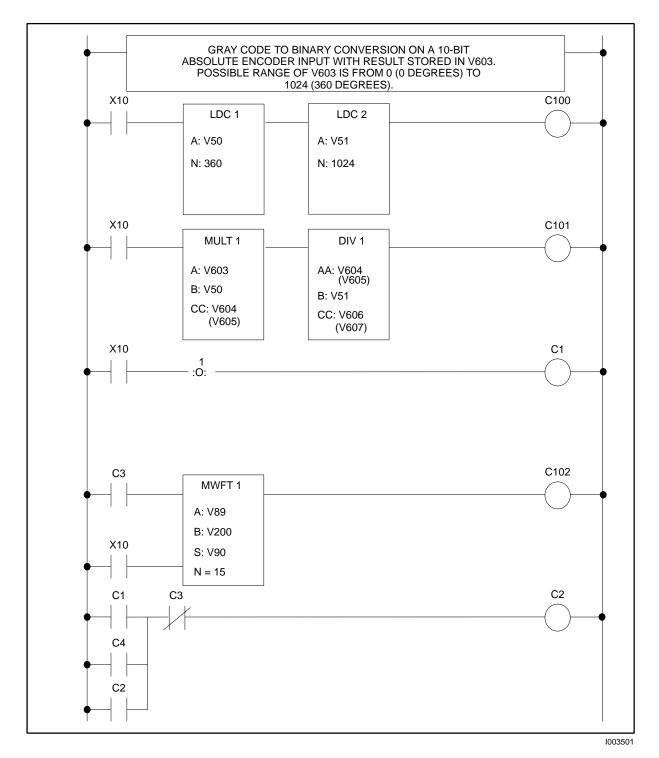

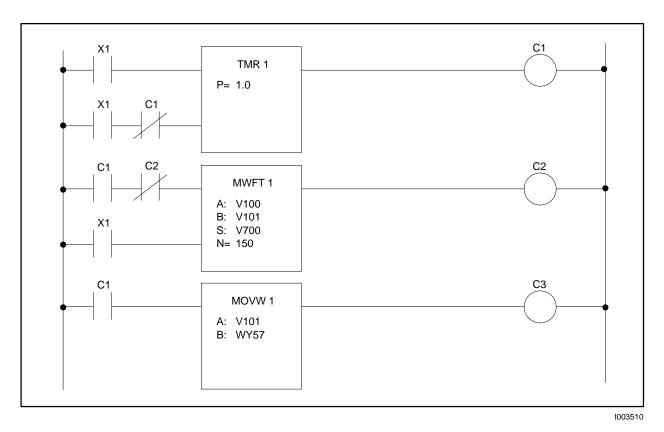

| E.10 | Using the MWFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>E-28</b><br>E-28<br>E-28                  |

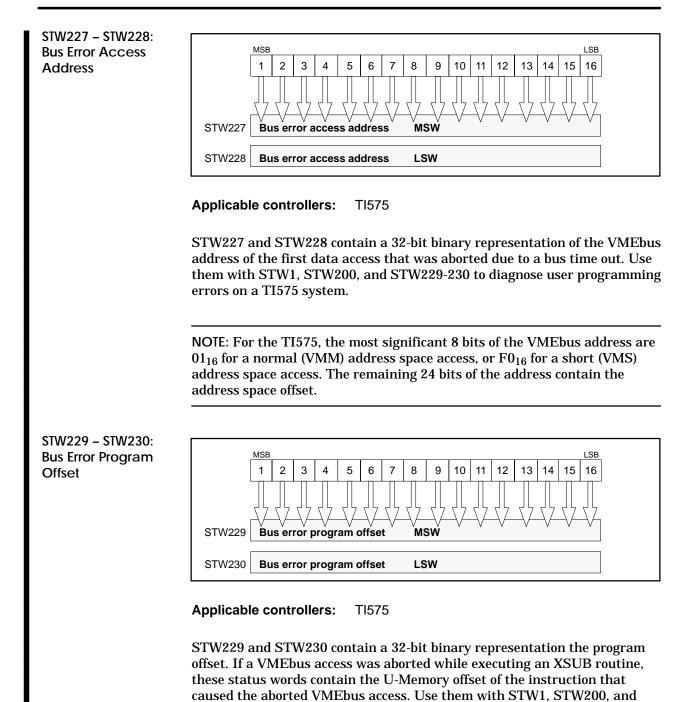

| E.11 | Using the WXOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>E-30</b><br>E-30<br>E-32<br>E-33          |