# **SIEMENS**

# **SIMATIC**

# ET 200X BM 147 CPU Basic Module

### Manual

<u>^!</u>

The following supplement is part of this documentation:

| No. | Designation         | Drawing number | Edition |  |

|-----|---------------------|----------------|---------|--|

| 1   | Product information | A5E00385826-02 | 11/2005 |  |

Preface, Contents 1 **Product Overview** 2 Addressing ET 200X in the PROFIBUS 3 Network 4 ET 200X in the MPI Network 5 Installation and Wiring 6 Commissioning and Diagnostics 7 Functions of the BM 147 CPU 8 Cycle and Response Times 9 Technical Specifications Changing from BM 147 CPU (6ES7 147-1AA01-0XB0) to 10 BM 147-1 CPU or BM 147-2 CPU Position of the BM 147 CPU in 11 the CPU Range **Appendices** Α **Order Numbers**

Glossary, Index

This manual is part of the documentation package with the order number **6ES7198-8FA01-8BA0**

Edition 05/2003 EWA-4NEB780602202-04

### **Safety Guidelines**

This manual contains notices intended to ensure personal safety, as well as to protect the products and connected equipment against damage. These notices are highlighted by the symbols shown below and graded according to severity by the following texts:

#### Danger

indicates that death, severe personal injury or substantial property damage will result if proper precautions are not taken.

### Warning

indicates that death, severe personal injury or substantial property damage can result if proper precautions are not taken.

#### Caution

indicates that minor personal injury can result if proper precautions are not taken.

### Caution

indicates that property damage can result if proper precautions are not taken.

#### **Notice**

draws your attention to particularly important information on the product, handling the product, or to a particular part of the documentation.

#### **Qualified Personnel**

Only **qualified personnel** should be allowed to install and work on this equipment. Qualified persons are defined as persons who are authorized to commission, to ground and to tag circuits, equipment, and systems in accordance with established safety practices and standards.

### **Correct Usage**

Note the following:

#### Warning

This device and its components may only be used for the applications described in the catalog or the technical description, and only in connection with devices or components from other manufacturers which have been approved or recommended by Siemens.

This product can only function correctly and safely if it is transported, stored, set up, and installed correctly, and operated and maintained as recommended.

#### **Trademarks**

SIMATIC®, SIMATIC HMI® and SIMATIC NET® are registered trademarks of SIEMENS AG.

Third parties using for their own purposes any other names in this document which refer to trademarks might infringe upon the rights of the trademark owners.

### Copyright © Siemens AG 1998-2003 All rights reserved

The reproduction, transmission or use of this document or its contents is not permitted without express written authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved.

Siemens AG Bereich Automation and Drives Geschaeftsgebiet Industrial Automation Systems Postfach 4848, D- 90327 Nuernberg

#### Disclaim of Liability

We have checked the contents of this manual for agreement with the hardware and software described. Since deviations cannot be precluded entirely, we cannot guarantee full agreement. However, the data in this manual are reviewed regularly and any necessary corrections included in subsequent editions. Suggestions for improvement are welcomed.

© Siemens AG 2003 Technical data subject to change.

# **Preface**

### Purpose of the manual

This manual complements the *ET 200X Distributed I/O Device* manual. It describes all the functions of the BM 147 CPU basic module. It does not deal with functions that have general applicability to the ET 200X. You will find these in the *ET 200X Distributed I/O Device* manual (see also the Section "Integration in the information landscape").

The information contained in this manual and in the *ET 200X Distributed I/O System* manual will enable you to operate the ET 200X with the BM 147 CPU basic module as a DP slave on the PROFIBUS-DP or in an MPI network. The master functionality of basic module BM 147-2 CPU is also described.

### Required level of knowledge

Knowledge of the field of automation engineering is required to understand the manual.

Knowledge on how to use computers or other PC equipment (e.g. programming devices) under the Windows 95/98/2000 and NT operating system is also required. You should also be familiar with the STEP 7 basic software. Refer to the "Programming with STEP 7 V5.x" manual.

# Scope of validity of the manual

This manual is valid for basic module BM 147-1 CPU with the order number 6ES7 147-1AA10-0XB0 and for basic module BM 147-2 CPU with the order number 6ES7 147-2AA00-0XB0, as well as for the components of the ET 200X distributed I/O device specified in the ET 200X Distributed I/O Device manual.

**Agreement:** When features and functions of the basic modules are described in this handbook that apply to both modules, the designation BM 147 CPU will be used. The full designation is only used when a feature is described that only applies to one of the basic modules.

This manual contains a description of the components that were valid at the time the manual was published. We reserve the right to enclose a Product Information bulletin containing up-to-date information about new components and new versions of components.

### Changes compared to the previous version

This manual contains the following changes that were made to the previous version of this manual, *Basic Module BM 147 CPU*, Edition 03:

- · Module name changed to BM 147 CPU

- New order numbers for BM 147 CPU:

- 6ES7 147-1AA10-0XB0 for BM 147-1 CPU

- 6ES7 147-2AA00-0XB0 for BM 147-2 CPU

- Connections using ECOFAST technology

- · No mechanical adjustment of the PROFIBUS address on the device

- · Coexistent MPI/DP interface

- · Additional DP master interface for BM 147-2 CPU

- New memory concept

- · Additional communication utilities

- New blocks

- Micro Memory Card (MMC) up to 8 Mbytes

- · Data archiving and project storage on MMC

- 32-bit run-time meter

The Instruction list is no longer integrated in the manual. Available commands with the runtimes and the execution times of the SFCs and SFBs can be found in the documentation package in the *operations list, S7-300, CPU 31xC, CPU 31x, IM 151-7 CPU, BM 147-1 CPU, BM 147-2 CPU.*

### Standards, certificates and approvals

The BM 147 CPU basic module is based on the IEC 61784-1:2002 Ed1 CP 3/1 standard. It fulfills the requirements and criteria of IEC 61131, Part 2 and the requirements for obtaining the CE marking. For BM 147 CPU, the certifications for cULus have been applied for. You will find detailed information on these standards, certificates and approvals in the ET 200X Distributed I/O Device manual.

### Position in the information landscape

This manual is a component of the documentation package with the order number 6ES7 198-8FA01-8BA0. The package consists of 5 manuals with the following content:

# BM 147 CPU Basic

- Addressing

- The ET 200X with the BM 147 CPU in the PROFIBUS network

- The ET 200X with the BM 147 CPU in the MPI network

- · Commissioning and diagnostics

- Functions of the BM 147 CPU

- Technical specifications

# ET 200X Distributed I/O

- Installation and wiring

- Commissioning and diagnostics

- Technical specifications of digital and analog modules

- Order numbers for digital and analog modules

#### **EM 300 Motor Starter**

- Wiring

- Commissioning and diagnostics

- Technical specifications

- Order numbers

### EM 148-FC Frequency Converter

- Wiring

- Commissioning and diagnostics

- Functions and technical data

### Instruction list S7-300 CPU 31xC, CPU 31x, IM 151-7 CPU, BM 147-1 CPU, BM 147-2 CPU

- The instruction set lists and their execution times

- A list of executable blocks (OBs/SFCs/SFBs) and their execution times

### Guide

The manual offers the following useful features that will assist you in rapidly finding the information you are looking for:

- At the beginning of the manual you will find a comprehensive table of contents and lists of the figures and tables in the manual.

- The sections of the chapters in the manual contain subheadings that allow you to gain a quick overview of the contents of the section.

- · Important technical terminology used in the manual is defined in the Glossary.

- At the end of the manual you will find a comprehensive index enabling rapid access to the information you are looking for.

### Special note

In addition to the ET 200X manuals, you will also need the manual for the DP master used and the documentation for the configuration and programming software used (see the list in Appendix A of the ET 200X Distributed I/O Device manual).

### Note

You will find a detailed list of the contents of the ET 200X manuals in Section 1.2 of this manual.

We recommend that you begin by reading this section so as to find out which parts of which manuals are most relevant to you in helping you to do what you want to do.

### Recycling and disposal

The components of the BM 147 CPU contain very few harmful substances which means that the unit can be recycled.

Please consult a certified disposal company specializing in electronics waste to ensure that your old device is recycled and disposed of in an environment-friendly manner.

### Additional support

Please contact your local Siemens representative if you have any queries about the products described in this manual.

http://www.siemens.com/automation/partner

# **Training center**

We offer courses to introduce you to the ET 200 distributed I/O system and the SIMATIC S7 programmable controller. Please contact your local training center or the central training center in Nuremberg, D-90327 Germany.

Telephone: +49 (911) 895-3200

Internet: http://www.sitrain.com

# **A&D Technical Support**

Accessible throughout the world at any time of day:

| Worldwide (Nuremberg)                   |                                          |                                     |

|-----------------------------------------|------------------------------------------|-------------------------------------|

| Technical Support                       |                                          |                                     |

|                                         |                                          |                                     |

| Loc. time: 0:00 to 24:00 / 365 days     |                                          |                                     |

| Teleph.: +49 (0) 180 5050-222           |                                          |                                     |

| Fax: +49 (0) 180 5050-223               |                                          |                                     |

| E-mail: adsupport@ siemens.com          |                                          |                                     |

| GMT: +1:00                              |                                          |                                     |

| Europe/Africa (Nuremberg)               | United States (Johnson City)             | Asia / Australia (Beijing)          |

| Authorization                           | Technical Support and Authorization      | Technical Support and Authorization |

| Loc. time: Mon Fri. 8:00 to 17:00       | Loc. time: Mon Fri. 8:00 to 17:00        | Loc. time: Mon Fri. 8:00 to 17:00   |

| Teleph.: +49 (0) 180 5050-222           | Teleph.: +1 (0) 423 262 2522             | Teleph.: +86 10 64 75 75 75         |

| Fax: +49 (0) 180 5050-223               | Fax: +1 (0) 423 262 2289                 | Fax: +86 10 64 74 74 74             |

| E-mail: adsupport@ siemens.com          | E-mail: simatic.hotline@ sea.siemens.com | E-mail: adsupport.asia@ siemens.com |

| GMT: +1:00                              | GMT: -5:00                               | GMT: +8:00                          |

| Technical support and authorization sta | ff generally speak English and German.   |                                     |

### Service & Support on the Internet

In addition to our documentation, we also offer you all of our know-how online on the Internet.

http://www.siemens.com/automation/service&support

There you will find:

- the newsletter, which constantly supplies you with the latest information on your products

- a search function in Service & Support to help you find the documents you need

- a forum in which users and specialists can exchange their experiences worldwide

- your local contact partner for Automation & Drives in our contact database

- information on on-site service, repairs and spare parts. You will find a lot more information under "Services".

# **Contents**

| 1 | Product                                                   | Overview                                                                                                                                                                    | 1-1                                                  |

|---|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|   | 1.1                                                       | What is the BM 147 CPU basic module?                                                                                                                                        | 1-2                                                  |

|   | 1.2                                                       | Guide to the ET 200X manuals                                                                                                                                                | 1-5                                                  |

| 2 | Address                                                   | sing                                                                                                                                                                        | 2-1                                                  |

|   | 2.1                                                       | Slot-based addressing                                                                                                                                                       | 2-2                                                  |

|   | 2.2                                                       | User-oriented addressing of the expansion modules                                                                                                                           | 2-4                                                  |

|   | 2.3                                                       | Data interchange with the DP master                                                                                                                                         | 2-5                                                  |

|   | 2.4                                                       | Accessing the intermediate memory in the BM 147 CPU                                                                                                                         | 2-7                                                  |

| 3 | ET 200X                                                   | in the PROFIBUS Network                                                                                                                                                     | 3-1                                                  |

|   | 3.1                                                       | ET 200X in the PROFIBUS network                                                                                                                                             | 3-2                                                  |

|   | 3.2                                                       | Network components                                                                                                                                                          | 3-6                                                  |

|   | 3.3                                                       | PROFIBUS address                                                                                                                                                            | 3-7                                                  |

|   | 3.4                                                       | Functions via the PD/OP                                                                                                                                                     | 3-8                                                  |

|   | 3.5                                                       | Direct communication                                                                                                                                                        | 3-11                                                 |

| 4 | ET 200X                                                   | in the MPI Network                                                                                                                                                          | 4-1                                                  |

|   | 4.1                                                       | ET 200X in the MPI network                                                                                                                                                  | 4-2                                                  |

|   | 4.2                                                       | MPI address                                                                                                                                                                 | 4-4                                                  |

| 5 | Installat                                                 | ion and Wiring                                                                                                                                                              | 5-1                                                  |

| 6 | Commis                                                    | sioning and Diagnostics                                                                                                                                                     | 6-1                                                  |

|   | 6.1                                                       | Configuring the BM 147 CPU                                                                                                                                                  | 6-2                                                  |

|   | 6.2                                                       | Resetting the memory of the BM 147 CPU                                                                                                                                      | 6-5                                                  |

|   | 6.3<br>6.3.1<br>6.3.2<br>6.3.3                            | Commissioning and start-up of the ET 200X Starting up the BM 147 CPU as a DP slave Starting up the BM 147-2 CPU as a DP master Start-up                                     | 6-8<br>6-8<br>6-9<br>6-12                            |

|   | 6.4                                                       | Diagnostics using LEDs                                                                                                                                                      | 6-13                                                 |

|   | 6.5                                                       | Diagnostics via diagnostic address with STEP 7                                                                                                                              | 6-16                                                 |

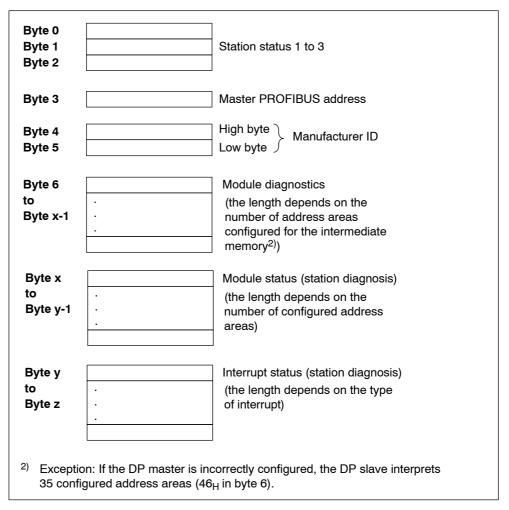

|   | 6.6<br>6.6.1<br>6.6.2<br>6.6.3<br>6.6.4<br>6.6.5<br>6.6.6 | Slave diagnostics with BM 147 CPU as intelligent slave Station status 1 to 3  Master PROFIBUS address  Manufacturer ID  Module diagnostics  Module status  Interrupt status | 6-19<br>6-20<br>6-22<br>6-22<br>6-23<br>6-24<br>6-25 |

| 7  | Functio                                          | ns of the BM 147 CPU                                                                                                                                          | 7-1                                          |

|----|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|    | 7.1                                              | Data for the PROFIBUS-DP                                                                                                                                      | 7-2                                          |

|    | 7.2                                              | The mode selector and LEDs                                                                                                                                    | 7-4                                          |

|    | 7.3                                              | SIMATIC Micro Memory Card                                                                                                                                     | 7-6                                          |

|    | 7.4<br>7.4.1<br>7.4.2<br>7.4.3<br>7.4.4<br>7.4.5 | Memory concept Memory areas of the BM 147 CPU Memory functions Address areas Handling data in DBs Storing/download entire projects on/from Micro Memory Cards | 7-13<br>7-13<br>7-16<br>7-21<br>7-24<br>7-26 |

|    | 7.5                                              | Interface                                                                                                                                                     | 7-27                                         |

|    | 7.6                                              | Clock                                                                                                                                                         | 7-29                                         |

|    | 7.7                                              | S7 connections                                                                                                                                                | 7-30                                         |

|    | 7.8                                              | Communication                                                                                                                                                 | 7-35                                         |

|    | 7.9                                              | Routing                                                                                                                                                       | 7-39                                         |

|    | 7.10                                             | Data consistency                                                                                                                                              | 7-42                                         |

|    | 7.11                                             | Blocks                                                                                                                                                        | 7-43                                         |

|    | 7.12                                             | Parameters                                                                                                                                                    | 7-45                                         |

| 8  | Cycle a                                          | nd Response Times                                                                                                                                             | 8-1                                          |

|    | 8.1                                              | Cycle time                                                                                                                                                    | 8-2                                          |

|    | 8.2                                              | Response time                                                                                                                                                 | 8-5                                          |

|    | 8.3                                              | Interrupt response time                                                                                                                                       | 8-8                                          |

|    | 8.4<br>8.4.1<br>8.4.2                            | Calculation examples  Calculation examples for the cycle time and response time  Calculation example for the interrupt response time                          | 8-9<br>8-9<br>8-10                           |

| 9  | Technic                                          | cal Specifications                                                                                                                                            | 9-1                                          |

|    | 9.1                                              | Technical specifications of the BM 147 CPU                                                                                                                    | 9-2                                          |

| 10 | Changii<br>BM 147                                | ng from BM 147 CPU (6ES7 147-1AA01-0XB0) to BM 147-1 CPU or<br>-2 CPU                                                                                         | 10-1                                         |

| 11 | Positio                                          | n of the BM 147 CPU in the CPU Range                                                                                                                          | 11-1                                         |

|    | 11.1                                             | Differences to selected S7-300 CPUs                                                                                                                           | 11-2                                         |

| Α  | Order N                                          | lumbers                                                                                                                                                       | A-1                                          |

|    | Glossa                                           | ry Gloss                                                                                                                                                      | sary-1                                       |

|    | Index                                            | In                                                                                                                                                            | dex-1                                        |

| Ia | ur |  |

|----|----|--|

|    |    |  |

|    |    |  |

| 1-1 | View of the ET 200X distributed I/O device with the BM 147 CPU   | 1-3  |

|-----|------------------------------------------------------------------|------|

| 1-2 | Components and the manuals required for them                     | 1-5  |

| 2-1 | Principles of data interchange between the DP master and         |      |

|     | the ET 200X with the BM 147 CPU                                  | 2-1  |

| 2-2 | Structure of the default address area                            | 2-2  |

| 2-3 | Slots on the ET 200X                                             | 2-2  |

| 2-4 | Example of address assignment to expansion modules               | 2-3  |

| 2-5 | Structure of the address area for user-oriented addressing       | 2-4  |

| 2-6 | Intermediate memory in the BM 147 CPU                            | 2-5  |

| 3-1 | Example of a PROFIBUS network                                    | 3-2  |

| 3-2 | Setting the mode of the DP interface at the BM 147 CPU           | 3-3  |

| 3-3 | PD/OP accesses the ET 200X via the DP interface in the DP master | 3-5  |

| 3-4 | The PD directly accesses the ET 200X                             | 3-5  |

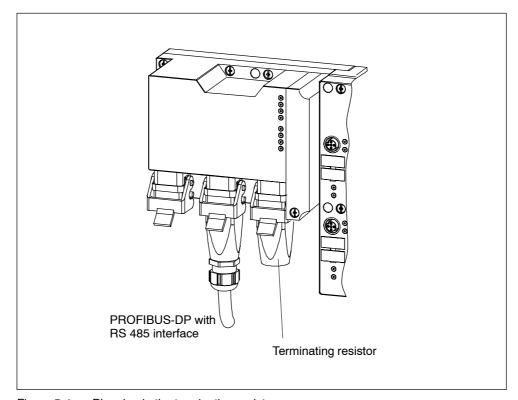

| 3-5 | Connecting the DP network                                        | 3-6  |

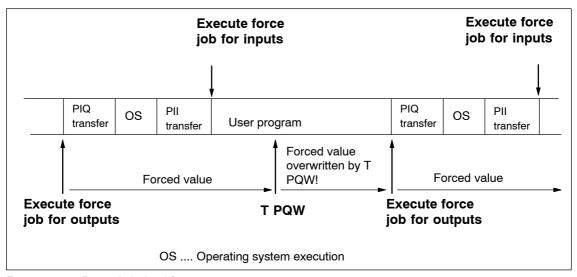

| 3-6 | Principle behind forcing                                         | 3-9  |

| 3-7 | Direct communication with the BM 147 CPU                         | 3-11 |

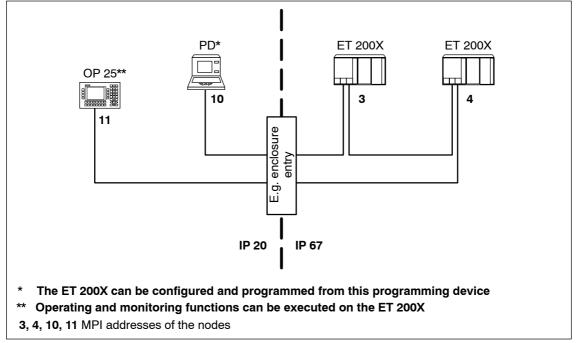

| 4-1 | Example of an MPI network                                        | 4-2  |

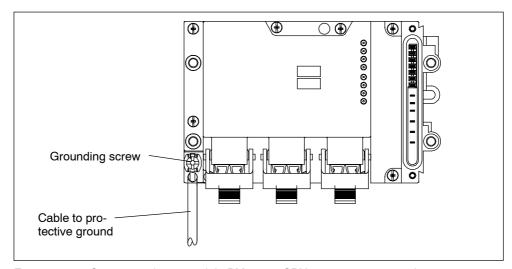

| 5-1 | Connecting basic module BM 147-2 CPU to protective ground        | 5-1  |

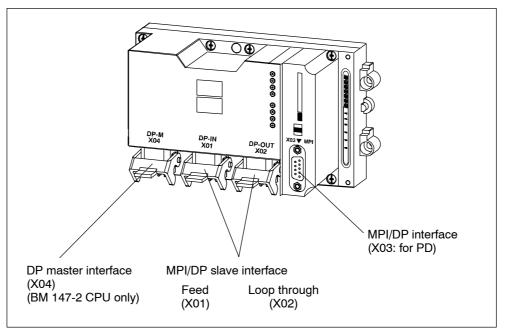

| 5-2 | Interfaces on basic module BM 147 CPU                            | 5-2  |

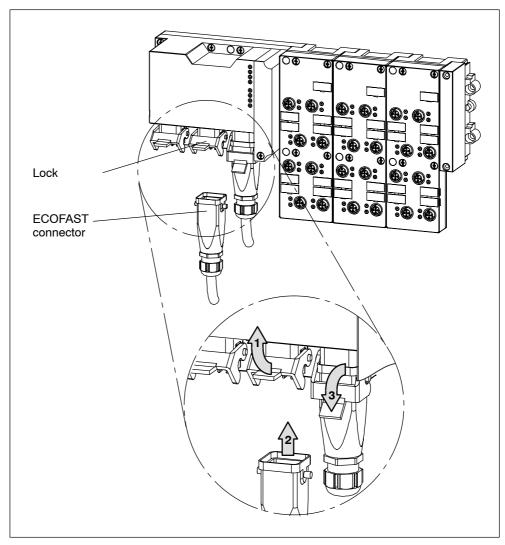

| 5-3 | Plugging the connector into the BM 147 CPU                       | 5-3  |

| 5-4 | Plugging in the terminating resistor                             | 5-4  |

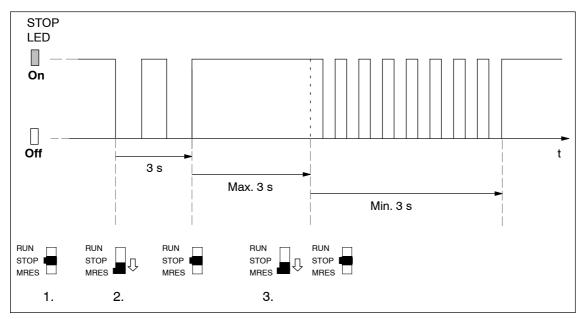

| 6-1 | Operating sequence on the mode selector for performing           |      |

|     | a general reset                                                  | 6-6  |

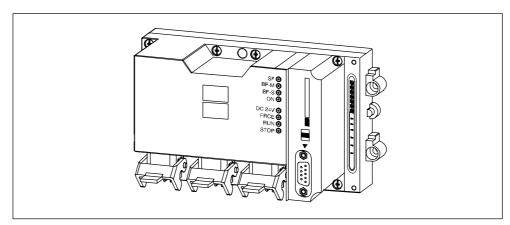

| 6-2 | Position of LEDs on basic module BM 147 CPU                      | 6-13 |

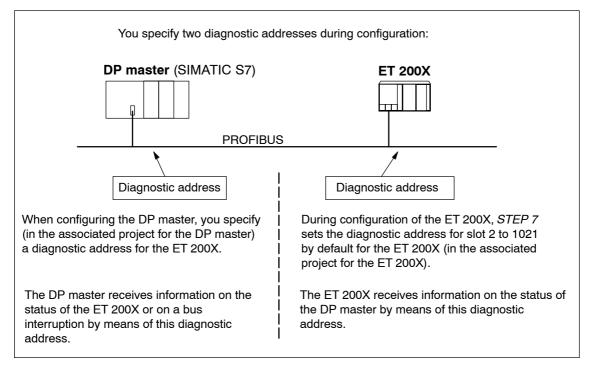

| 6-3 | Diagnostic addresses for the DP master and ET 200X               | 6-16 |

| 6-4 | Format of the slave diagnostic data                              | 6-19 |

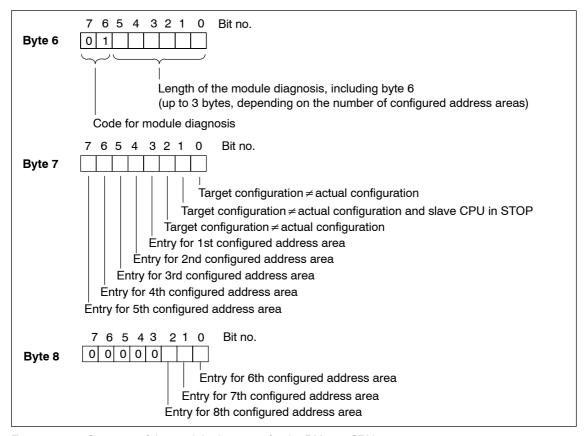

| 6-5 | Structure of the module diagnosis for the BM 147 CPU             | 6-23 |

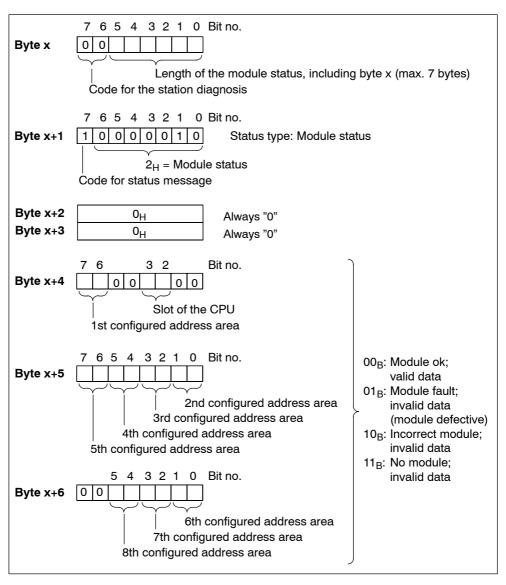

| 6-6 | Structure of the module status                                   | 6-24 |

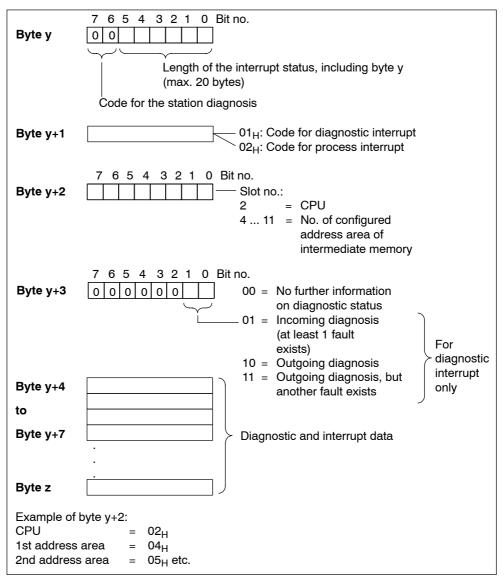

| 6-7 | Structure of the interrupt status                                | 6-25 |

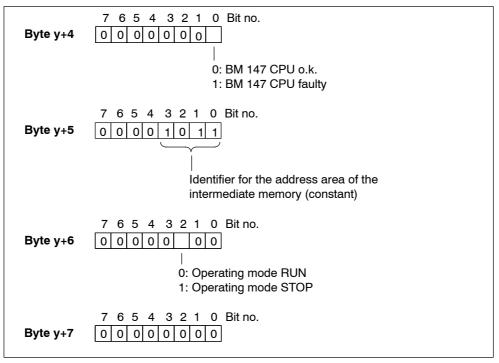

| 6-8 | Byte y+4 to y+7 for the diagnostic interrupt                     |      |

|     | (changed operating status of the intelligent slave)              | 6-26 |

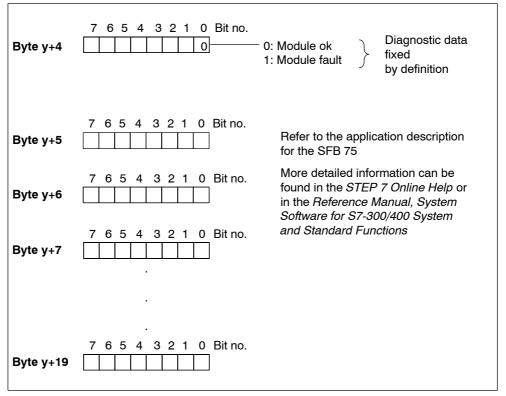

| 6-9 | Byte y+4 to y+7 for diagnostic interrupt (SFB 75)                | 6-27 |

| 7-1 | Mode selector                                                    | 7-4  |

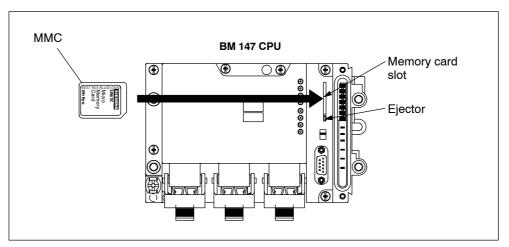

| 7-2 | Position of the memory card slot for the MMC on the BM 147 CPU   | 7-10 |

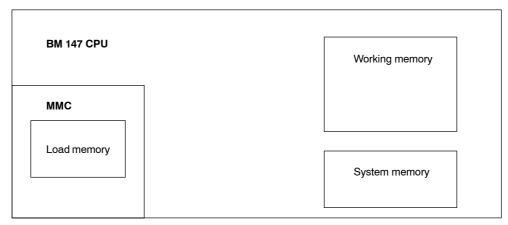

| 7-3 | Memory areas of the BM 147 CPU                                   | 7-13 |

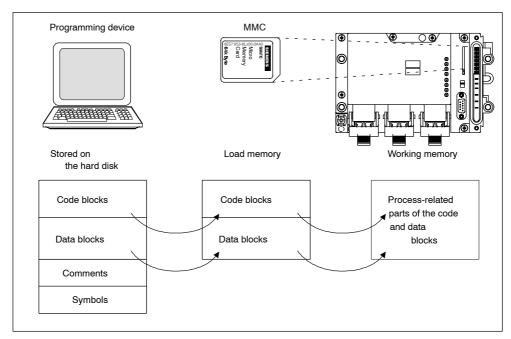

| 7-4 | Load and working memory                                          | 7-16 |

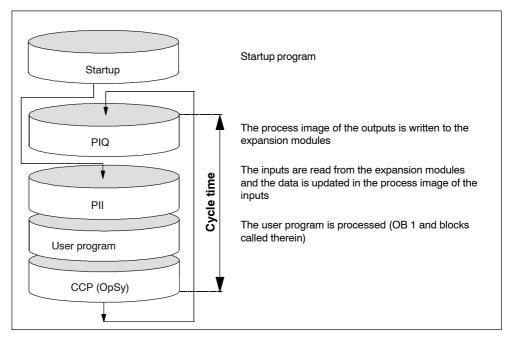

| 7-5 | Processing steps within a cycle                                  | 7-22 |

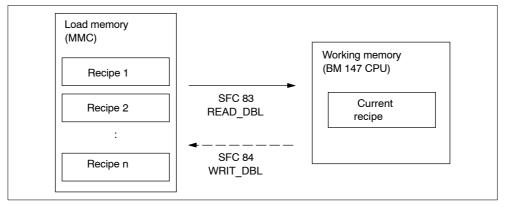

| 7-6 | Handling recipe data                                             | 7-24 |

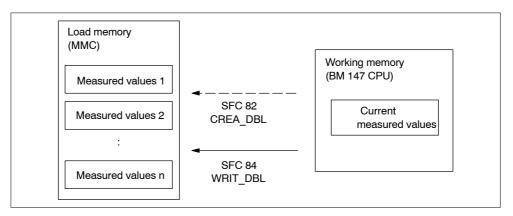

| 7-7 | Handling measured value archives                                 | 7-25 |

| 7-8 | Routing gateway                                                  | 7-40 |

| 7-9 | Routing – TeleService application example                        | 7-41 |

| 8-1 | Component parts of the cycle time                                | 8-2  |

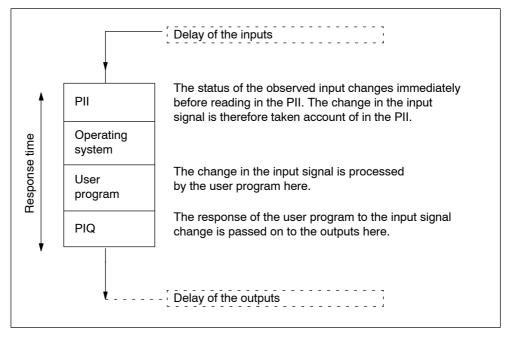

| 8-2 | Shortest response time                                           | 8-6  |

| 8-3 | Longest response time                                            | 8-7  |

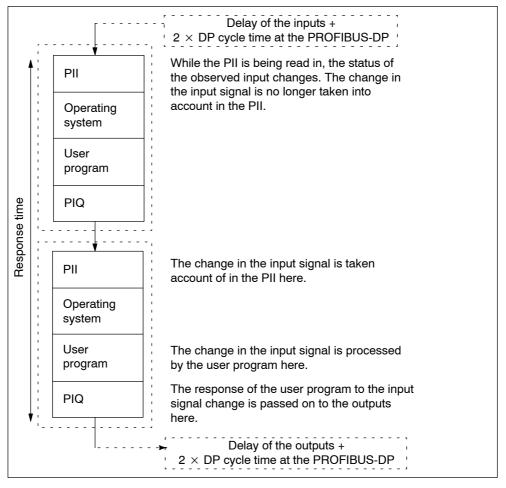

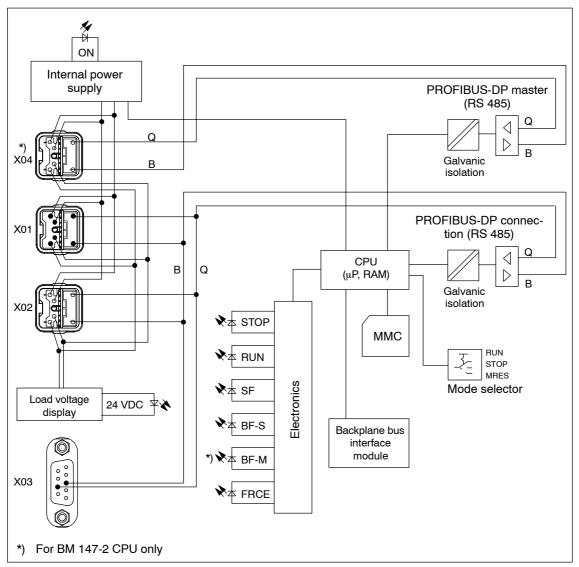

| 9-1 | Block diagram BM 147 CPU                                         | 9-4  |

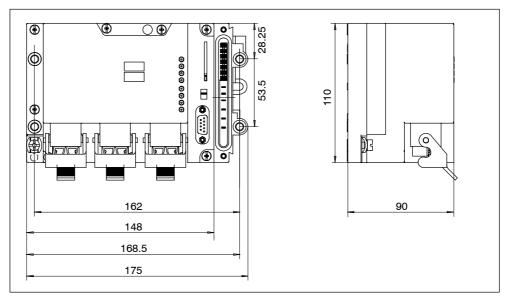

| 9-2 | Dimensioned drawing of basic module BM 147 CPU                   |      |

|     | (BM 147-2 CPU is shown)                                          | 9-5  |

### **Tables**

| 1-1  | Interface concept of the BM 147 CPU                                  | 1-3  |

|------|----------------------------------------------------------------------|------|

| 1-2  | Topics of the manuals in the ET 200X manual package                  | 1-6  |

| 2-1  | Addresses of the ET 200X expansion modules                           | 2-3  |

| 2-2  | Accessing the address areas                                          | 2-7  |

| 2-3  | Addressing interface in STEP 7 (extract)                             | 2-8  |

| 3-1  | Behavior of the BM 147 CPU depending on the DP interface setting     | 3-4  |

| 6-1  | Configuration options                                                | 6-2  |

| 6-2  | Ways to reset the memory                                             | 6-5  |

| 6-3  | Internal CPU events at memory resetting                              | 6-6  |

| 6-4  | Event recognition of the BM 147-2 CPU as a DP master                 | 6-10 |

| 6-5  | LED display for PROFIBUS-DP (BM 147 CPU is a slave)                  | 6-14 |

| 6-6  | LED display for PROFIBUS-DP (BM 147-2 CPU is a master)               | 6-15 |

| 6-7  | Responses to operating mode changes and interruptions in user        |      |

|      | data transfer in the DP master and the ET 200X with the BM 147 CPU . | 6-17 |

| 6-8  | Evaluation of RUN/STOP Transitions in the DP Master/ET 200X          | 6-18 |

| 6-9  | Structure of station status 1 (byte 0)                               | 6-20 |

| 6-10 | Structure of station status 2 (byte 1)                               | 6-21 |

| 6-11 | Structure of station status 3 (byte 2)                               | 6-21 |

| 6-12 | Structure of the master PROFIBUS address (byte 3)                    | 6-22 |

| 6-13 | Structure of the manufacturer identification (bytes 4 and 5)         | 6-22 |

| 7-1  | Positions of the mode selector                                       | 7-4  |

| 7-2  | LEDs for CPU functionality                                           | 7-5  |

| 7-3  | Available MMCs                                                       | 7-8  |

| 7-4  | Firmware update with MMC                                             | 7-11 |

| 7-5  | Backing up the operating system                                      | 7-12 |

| 7-6  | Retentive behavior of the memory objects                             | 7-15 |

| 7-7  | Retentive behavior of the DBs in BM 147 CPU                          | 7-15 |

| 7-8  | Address areas of the system memory                                   | 7-21 |

| 7-9  | Connectable devices                                                  | 7-28 |

| 7-10 | Features of the clock                                                | 7-29 |

| 7-11 | Distribution of the S7 connections                                   | 7-33 |

| 7-12 | Availability of the S7 connections                                   | 7-34 |

| 7-13 | Communication utilities of the BM 147 CPU                            | 7-35 |

| 7-14 | GD resources of the BM 147 CPU                                       | 7-38 |

| 7-15 | Overview of the Blocks                                               | 7-43 |

| 7-16 | Parameter blocks, settable parameters and their ranges for           |      |

|      | the BM 147 CPU                                                       | 7-45 |

| 8-1  | Operating system processing time in the scan cycle checkpoint        | 8-3  |

| 8-2  | Process image updating                                               | 8-3  |

| 8-3  | Extending the cycle by nesting interrupts                            | 8-4  |

| 8-4  | Interrupt response times of the BM 147 CPU (without communication)   | 8-8  |

| 9-1  | Pin assignment of basic module BM 147 CPU                            | 9-3  |

| 11-1 | Differences to selected S7-300 CPUs                                  | 11-2 |

| A-1  | BM 147 CPU basic modules – order numbers                             | A-1  |

| A-2  | Micro Memory Cards – order numbers                                   | A-1  |

| A-3  | Accessories – order numbers                                          | A-2  |

Product Overview

# In this chapter

The product overview provides information about

- The role of the BM 147 CPU basic module within the ET 200X distributed I/O device

- Which manuals in the ET 200X manual package contain what information.

# In this chapter

| In<br>Section | Contents                             | Page |

|---------------|--------------------------------------|------|

| 1.1           | What is the BM 147 CPU basic module? | 1-2  |

| 1.2           | Guide to the ET 200X manuals         | 1-5  |

# 1.1 What is the BM 147 CPU basic module?

#### What is the BM 147 CPU basic module?

The BM 147 CPU is a component of the ET 200X distributed I/0 device designed in the degrees of protection IP 65, IP 66 and IP 67. Unlike all other basic modules, the BM 147 CPU features integrated PLC functionality for pre-processing purposes. It enables you to decentralize control tasks.

An ET 200X with a BM 147 CPU can therefore exercise full and, if necessary, independent control over a process-related functional unit and can be used as a stand-alone CPU. The use of the BM 147 CPU leads to further modularization and standardization of technological functional units and simple, clear machine concepts.

### How is the BM 147 CPU integrated in the ET 200X?

The BM 147 CPU basic module is integrated in the ET 200X in the same way as any other basic module. In other words, its configuration concept, installation and expansion capability are the same.

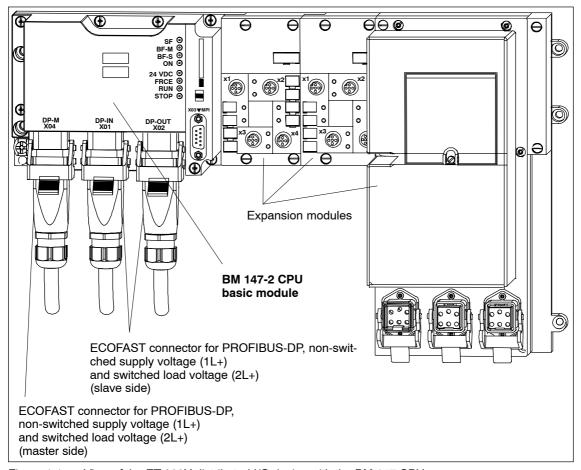

### View

The figure below shows a sample configuration of an ET 200X with a BM 147 CPU.

Figure 1-1 View of the ET 200X distributed I/O device with the BM 147 CPU

### Interface

The BM 147 CPU has the following interfaces:

Table 1-1 Interface concept of the BM 147 CPU

| Description                  | Functionality                           | Plug-in connection    | Remarks on functionality          |

|------------------------------|-----------------------------------------|-----------------------|-----------------------------------|

| X01<br>(DP-IN)               | MPI/DP slave interface (feed)           | ECOFAST               | Coexistent MPI/DP                 |

| X02<br>(DP-OUT)              | MPI/DP slave interface (looped through) | ECOFAST               | interface one logical             |

| X03<br>(MPI)                 | MPI/DP<br>PD interface                  | 9-pin<br>Sub-D socket |                                   |

| X04 <sup>1</sup> )<br>(DP-M) | DP master interface                     | ECOFAST               | Additional<br>DP master interface |

<sup>1)</sup> Only featured in BM 147-2 CPU

#### Features of the BM 147 CPU in contrast to other basic modules

The BM 147 CPU basic module has the following special features:

- The basic module has PLC functionality (integrated CPU component with 48 kByte working memory).

- The basic module can only be operated with fitted load memory (MMC).

- The basic module does not have integrated inputs and outputs, but, like any other basic module, up to 7 expansion modules can be added to it from the ET 200X range.

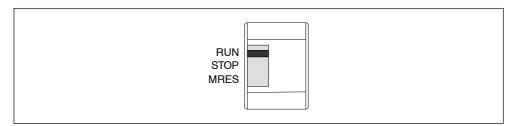

- The basic module has an operating mode switch with positions for RUN, STOP and MRES.

- There are 8 LEDs on the front of the interface module to indicate the following:

- ET 200X faults (SF)

- Bus faults (BF-S and BF-M) (BF-M only in BM 147-2 CPU),

- Non-switched supply voltage for electronics/sensors (1L+) (ON),

- Switched load voltage (2L+) (24 VDC),

- Force requests (FRCE)

- Operating mode of the BM 147 CPU (RUN and STOP)

- The BM 147-2 CPU basic module also contains an additional interface with DP master functionality.

### How is the ET 200X configured with the BM 147 CPU?

To configure the ET 200X with the BM 147 CPU (configuration and parameterization), you will require the *STEP 7* configuration software as of version V 5.2 + Service Pack 1. How to configure the ET 200X with the BM 147 CPU is described in Section 6.1 of this manual.

# How is the BM 147 CPU programmed?

To program the BM 147 CPU, you will require the *STEP 7* configuration software as of version V 5.2 + Service Pack 1. In the *Instruction list*, you will find the *STEP 7* instruction set for programming the BM 147 CPU.

# 1.2 Guide to the ET 200X manuals

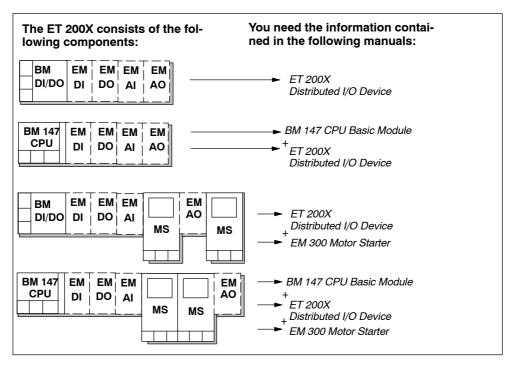

### Components and the manuals required for them

The components of the ET 200X are described in various manuals in the ET 200X package. The figure below shows possible ET 200X configurations and the manuals required for them.

Figure 1-2 Components and the manuals required for them

# Where do you find what information?

The table below will help you get your bearings and find the information you need quickly. It tells you which manual you need to refer to and which chapter deals with the topic you are interested in.

Table 1-2 Topics of the manuals in the ET 200X manual package

|                                                                                                                              |                                       | Manual                          |                           |                           |

|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------|---------------------------|---------------------------|

| Contents                                                                                                                     | ET 200 X<br>Distributed<br>I/O Device | BM 147 CPU<br>Basic Mod-<br>ule | EM 300 Mo-<br>tor Starter | Chapter/<br>Appen-<br>dix |

| ET 200X configuration options                                                                                                | х                                     |                                 |                           | 2                         |

| Installing the ET 200X; setting the PROFIBUS address; connecting a terminating resistor                                      | ×                                     |                                 |                           | 3                         |

| BM 147 CPU addressing                                                                                                        |                                       | х                               |                           | 2                         |

| Electrical configuration and wiring of the ET 200X                                                                           | ×                                     |                                 |                           | 4                         |

| Wiring motor starters                                                                                                        |                                       |                                 | х                         | 2                         |

| The ET 200X with the BM 147 CPU in the PROFIBUS network                                                                      |                                       | х                               |                           | 3                         |

| The ET 200X with the BM 147 CPU in the MPI network                                                                           |                                       | х                               |                           | 4                         |

| Mounting and wiring the BM 147 CPU                                                                                           |                                       | х                               |                           | 5                         |

| Commissioning and diagnostics of the ET 200X                                                                                 | х                                     |                                 |                           | 5                         |

| Commissioning and diagnostics of the ET 200X with the BM 147 CPU                                                             |                                       | ×                               |                           | 6                         |

| Commissioning and diagnostics of the ET 200X with motor starters                                                             |                                       |                                 | Х                         | 3                         |

| Functions of the BM 147 CPU                                                                                                  |                                       | х                               |                           | 7                         |

| BM 147 CPU cycle and response times                                                                                          |                                       | х                               |                           | 8                         |

| General technical specifications of the ET 200X (standards, certificates and approvals, EMC, environmental conditions, etc.) | х                                     |                                 |                           | 6                         |

| Technical specifications of the basic and expansion modules with DI, DO, AI and AO                                           | x                                     |                                 |                           | 7                         |

| Technical specifications of the BM 147 CPU                                                                                   |                                       | Х                               |                           | 9                         |

| Technical specifications of the motor starters                                                                               |                                       |                                 | х                         | 5                         |

| Compatibility                                                                                                                |                                       | х                               |                           | 10                        |

| Order numbers of the components                                                                                              | х                                     |                                 |                           | Q                         |

| Order numbers for the motor starters                                                                                         |                                       |                                 | х                         | Q                         |

| GSD files                                                                                                                    | х                                     |                                 |                           | В                         |

| Dimensioned drawings of the basic modules and digital and analog expansion modules                                           | х                                     |                                 |                           | С                         |

| Dimensioned drawings of motor starters                                                                                       |                                       |                                 | х                         | В                         |

Table 1-2 Topics of the manuals in the ET 200X manual package

|                                                   |                                       | Manual                          |                           |                           |

|---------------------------------------------------|---------------------------------------|---------------------------------|---------------------------|---------------------------|

| Contents                                          | ET 200 X<br>Distributed<br>I/O Device | BM 147 CPU<br>Basic Mod-<br>ule | EM 300 Mo-<br>tor Starter | Chapter/<br>Appen-<br>dix |

| Configuration assignment frame for motor starters |                                       |                                 | х                         | С                         |

| Position of the BM 147 CPU in the CPU range       |                                       | х                               |                           | 11                        |

| Glossary                                          | х                                     | х                               |                           | Glossary                  |

The frame for configuration and parameter assignment for the BM 147 CPU can be found on the Internet at http://www.ad.siemens.de/simatic-cs

Addressing 2

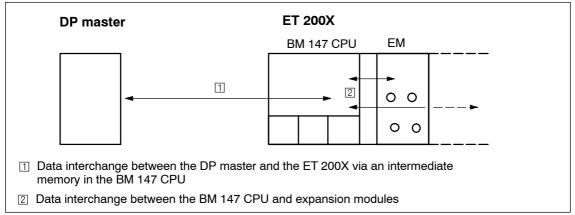

# Principles of data interchange between the DP master and the ET 200X

The figure below illustrates both mechanisms of data interchange for which addresses are required in the ET 200X. In this chapter you will find all the information you need on the addressing of the ET 200X with the BM 147 CPU.

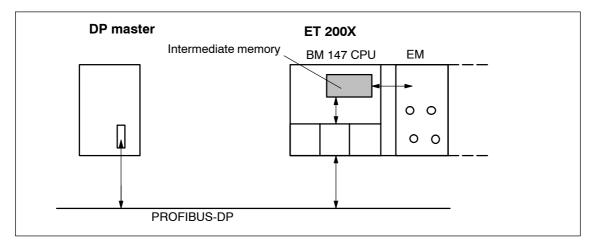

Figure 2-1 Principles of data interchange between the DP master and the ET 200X with the BM 147 CPU

### In this chapter

| In Section | Contents                                            | Page |

|------------|-----------------------------------------------------|------|

| 2.1        | Slot-based addressing                               | 2-2  |

| 2.2        | User-oriented addressing of the expansion modules   | 2-4  |

| 2.3        | Data interchange with the DP master                 | 2-5  |

| 2.4        | Accessing the intermediate memory in the BM 147 CPU | 2-7  |

# 2.1 Slot-based addressing

#### Slot-oriented address allocation

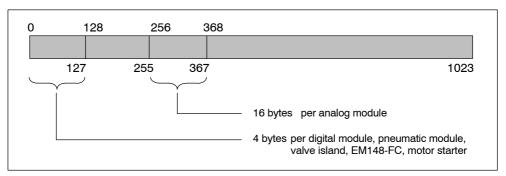

In slot-based addressing (default addressing), each of a module's slot numbers is assigned an address area in the BM 147 CPU.

Depending on the type of the expansion module, the addresses are digital or analog (see Table 2-1). The address allocation is not fixed and can be changed, but there is a default address area.

Figure 2-2 Structure of the default address area

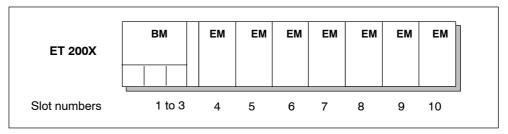

### Slot assignment

The figure below shows an ET 200X configuration with 7 expansion modules (maximum configuration) and the slot assignment.

Figure 2-3 Slots on the ET 200X

### Slot rules

When assembling an ET 200X with extension modules and pneumatic interface modules, follow the rules in the ET 200X Distributed I/O Device manual, Chap. 2.8.

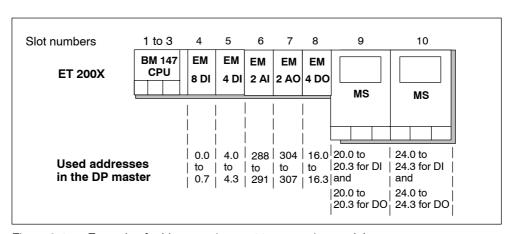

### Address assignment

For each of the expansion modules, of which there can be up to seven, 4 bytes are reserved for digital I/O devices and 16 bytes for analog I/O devices, depending on the slot, in the address areas of the BM 147 CPU.

The table below indicates the fixed address assignment for analog and digital modules per slot. The address areas of the expansion modules are "visible" only to a BM 147 CPU in the ET 200X, not to the associated DP master. The DP master has no access to the expansion modules.

| Reserved          | Slot number     |   |               |               |               |               |               |               |               |    |

|-------------------|-----------------|---|---------------|---------------|---------------|---------------|---------------|---------------|---------------|----|

| address area      | 1               | 2 | 3             | 4             | 5             | 6             | 7             | 8             | 9             | 10 |

| Digital modules   | Basic<br>module |   | 0 to 3        | 4 to 7        | 8 to 11       | 12 to 15      | 16 to 19      | 20 to 23      | 24 to 27      |    |

| Analog<br>modules |                 |   | 256 to<br>271 | 272 to<br>287 | 288 to<br>303 | 304 to<br>319 | 320 to<br>335 | 336 to<br>351 | 352 to<br>367 |    |

Table 2-1 Addresses of the ET 200X expansion modules

The unassigned addresses in the range 28 to 127 are in the process image in default addressing and can be used any way you choose in the user program. If 4 bits in a byte are already used, the remaining 4 bits cannot be used.

You can use the bytes in the address areas that are not used by modules in any way you choose in your user program. In the configuration in Figure 2-4, for example, bytes 1, 2 and 3 can be used as you choose.

### Example of address assignment to expansion modules

The figure below illustrates a sample ET 200X configuration, showing address allocation for expansion modules by way of example. The addresses for the expansion modules are predefined in default addressing.

Figure 2-4 Example of address assignment to expansion modules

# 2.2 User-oriented addressing of the expansion modules

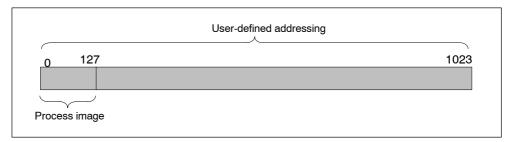

#### User-oriented address allocation

User-oriented address allocation means you can select the following in units of 1 byte and independent of one another within the range 0 to 1023:

- · Input addresses of expansion modules and

- · Output addresses of expansion modules.

The addresses 0 to 127 are in the process image. Assign the addresses in *STEP 7*. When you do this, you define the base address of the module, on which all the addresses of the module depend.

Figure 2-5 Structure of the address area for user-oriented addressing

### **Advantages**

Advantages of user-defined address allocation:

- Optimum utilization of the address areas available, since "address gaps" between the modules do not occur.

- When creating standard software, you can specify addresses that are independent of the configuration of the ET 200X station.

# 2.3 Data interchange with the DP master

### User data transfer via an intermediate memory

The user data is located in an intermediate memory in the BM 147 CPU. This intermediate memory is always used when user data is transferred between the BM 147 CPU and the DP master. The intermediate memory consists of a maximum of 32 address areas.

Figure 2-6 Intermediate memory in the BM 147 CPU

### Address areas for user data transfer with the DP master

The ET 200X provides the PROFIBUS-DP with a maximum of 244 bytes of input data and 244 bytes of output data. This data can be addressed in the intermediate memory of the BM 147 CPU in up to 32 address areas.

An address area contains a maximum of 32 bytes. A maximum of 244 bytes is available for input and output data.

### **Data consistency**

You define data consistency as byte, word, or overall consistency per address area. Consistency can amount to up to 32 bytes/16 words per address area.

# DP diagnostic address in STEP 7

When the ET 200X is configured with *STEP 7*, two diagnostic addresses are set. The ET 200X receives information on the status of the DP master or on a bus interruption by means of these diagnostic addresses (see Section 6.5). In DP slave mode, the diagnostic addresses are by default at:

| BM 147-1 CPU | BM 147-2 CPU |                         |

|--------------|--------------|-------------------------|

| 1021         | 1020         | Address for slot 2      |

| 1022         | 1021         | Slave diagnosis address |

Detailed information can be found in the *Online Help for STEP 7* under *Slot model for I slaves*.

### Access to free areas in the process image

If you access available but unconfigured process image areas, no process image errors will be generated. You can therefore use inputs and outputs in the process image to which no I/O modules are allocated as markers.

# 2.4 Accessing the intermediate memory in the BM 147 CPU

# Access in the user program

The following table tells you how to access the intermediate memory in the BM 147 CPU from the user program.

Table 2-2 Accessing the address areas

| Access dependent on data consistency                            | The following applies                                                                                                                                                                                                                                                                                                    |  |  |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1, 2 or 4-byte data consistency with load/transfer instructions | All areas parameterized with "unity" consistency can be accessed. A maximum of 32 bytes of input data can be addressed with load instructions and 32 bytes of output data with transfer instructions (L PEB/PEW/PED; T PAB/PAW/PAD; see also <i>Instruction list</i> ).                                                  |  |  |

|                                                                 | The data consistency for word addressing is 2 bytes; for double-word addressing it is 4 bytes.                                                                                                                                                                                                                           |  |  |

|                                                                 | Access is also possible via the process image.                                                                                                                                                                                                                                                                           |  |  |

| 1- to 32-byte data consistency on the PROFIBUS-DP with SFC 14   | If the address area of consistent data is in the process image, this area is updated automatically.                                                                                                                                                                                                                      |  |  |

| and SFC 15                                                      | If you want to access data in the intermediate memory, you have to read the input data with SFC 14 "DPRD_DAT" and write the output data with SFC 15 "DPWR_DAT". These SFCs have data consistency of 1 to 32 bytes.                                                                                                       |  |  |

|                                                                 | You can only copy the input data read with SFC 14 as a block of 1 to 32 bytes to a memory marker address area, for example, where it can be addressed with A M x.y. You can also write only one block of 1 to 32 bytes as output data with SFC 15 (see also the <i>System and Standard Functions</i> ) Reference Manual. |  |  |

|                                                                 | If you access areas with "whole length" consistency, the length in the SFC must correspond to the length of the parameterized area.                                                                                                                                                                                      |  |  |

|                                                                 | It is also possible to address the consistent areas directly (for example, L PIW or T PQW).                                                                                                                                                                                                                              |  |  |

#### Rules for address allocation

You must obey the following rules when allocating addresses for the ET 200X with the BM 147 CPU:

- Assignment of the address areas:

- Input data for the ET 200X is always output data for the DP master

- Output data for the ET 200X is always input data for the DP master

- You access the data in the user program using load/transfer instructions or SFCs 14 and 15.

- The length, unit and consistency of the associated address areas for the DP master and the DP slave must be identical.

- Addresses for the master and the slave can be different in the logically identical intermediate memory (mutually independent logical I/O address areas in the master and the slave CPU)

When the BM 147 CPU is configured with *STEP 7* for operation in the S5 or in non-Siemens systems, it is clear that only the logical addresses within the slave CPU are allocated. The addresses are then assigned in the master system using the specific configuration tool of the master system.

# Addressing interface in STEP 7

The following table illustrates the principles of address allocation. You will also find this table in the *STEP 7* interface. You must set the mode "MS" (for master slave) or "DX" (direct connection) in *STEP 7* (see Section 3.5).

Table 2-3 Addressing interface in STEP 7 (extract)

|   | Mode                   | Master                             |         | PROFIL                             | BUS-DP partner | Parameters                                                                           |      |              |

|---|------------------------|------------------------------------|---------|------------------------------------|----------------|--------------------------------------------------------------------------------------|------|--------------|

|   |                        | I/O                                | Address | I/O                                | Address        | Length                                                                               | Unit | Consistency  |

| 1 | MS                     | Q                                  | 200     | I                                  | 128            | 4                                                                                    | Byte | Unit         |

| 2 | MS                     | Q                                  | 300     | I                                  | 132            | 8                                                                                    | Byte | Total length |

| 3 | MS                     | I                                  | 700     | Q                                  | 128            | 4                                                                                    | Word | Unit         |

| 4 | MS                     | I                                  | 50      | Q                                  | 136            | 4                                                                                    | Byte | Unit         |

| : |                        |                                    |         |                                    |                |                                                                                      |      |              |

| 7 |                        |                                    |         |                                    |                |                                                                                      |      |              |

|   | MS:<br>Master<br>Slave | Address areas in the DP master CPU |         | Address areas in the<br>BM 147 CPU |                | These address area parameters must be identical for the DP master and the BM 147 CPU |      |              |

# Sample Program

Below you will see a sample program for data interchange between the DP master and the DP slave.

You will find the addresses in Table 2-3.

SFCs 14 and 15 are called by specifying the logical address in hexadecimal format.

|                                     | in the BM 147 CPU                                        |          |                                                      |  |  |  |  |

|-------------------------------------|----------------------------------------------------------|----------|------------------------------------------------------|--|--|--|--|

| Data preprocessing in the DP slave: |                                                          |          |                                                      |  |  |  |  |

| L                                   | 2                                                        |          | Load actual value 2 and                              |  |  |  |  |

| T                                   | MB                                                       | 6        | transfer to memory byte 6.                           |  |  |  |  |

| L                                   | IB                                                       | 0        | Load input byte 0 and                                |  |  |  |  |

| T                                   | MB                                                       | 7        | transfer to memory byte 7.                           |  |  |  |  |

| Forwa                               | Forward data to DP master                                |          |                                                      |  |  |  |  |

| L                                   | MW                                                       | 6        | Load memory word 6 and                               |  |  |  |  |

| T                                   | PQW                                                      | 136      | transfer to peripheral output word 136               |  |  |  |  |

|                                     |                                                          |          | in the DP Master CPU                                 |  |  |  |  |

| Postp                               | rocess 1                                                 | received | data in the DP master:                               |  |  |  |  |

| L                                   | PIB                                                      | 50       | Load peripheral input byte 50 and                    |  |  |  |  |

| T                                   | MB                                                       | 60       | transfer to memory byte 60.                          |  |  |  |  |

| L                                   | PIB                                                      | 51       | Load peripheral input byte 51 and                    |  |  |  |  |

| L                                   | B#16#                                                    | 3        | load byte 3;                                         |  |  |  |  |

| +                                   | I                                                        |          | add the values as integer data type and              |  |  |  |  |

| T                                   | MB                                                       | 61       | transfer the result to memory byte 61.               |  |  |  |  |

| Data                                | preproce                                                 | essing i | n the DP master:                                     |  |  |  |  |

| L                                   | 10                                                       |          | Load actual value 10 and                             |  |  |  |  |

| +                                   | 3                                                        |          | add 3,                                               |  |  |  |  |

| T                                   | MB                                                       | 67       | transfer the result to memory byte 67.               |  |  |  |  |

| Send                                | the data                                                 | a (memor | y bytes 60 to 67) to the DP slave:                   |  |  |  |  |

| CALL                                | SFC                                                      | 15       | Call system function 15:                             |  |  |  |  |

| LADD                                | R:= W#16                                                 | 5#12C    | Write the data to the output address area as of      |  |  |  |  |

| RECO                                | RD:= P#1                                                 | 460.0 By | te8 address 300 (12C hexadecimal) with a length of 8 |  |  |  |  |

| RET_                                | VAL:=MW                                                  | 22       | bytes as of memory byte 60.                          |  |  |  |  |

|                                     | in the BM 147 CPU                                        |          |                                                      |  |  |  |  |

| Recei                               | Receive data from the DP master (stored in MB 30 to 37): |          |                                                      |  |  |  |  |

| CALL                                | CALL SFC 14 Call system function 14:                     |          |                                                      |  |  |  |  |

| LADD                                | R:= W#16                                                 | 5#84     | Write the data from the input address area as of     |  |  |  |  |

| RET VAL:=MW 20                      |                                                          | 20       | address 132 (84 hexadecimal) with a length of 8      |  |  |  |  |

| RECO                                | RECORD:=P#M30.0 Byte8 bytes to memory byte 30.           |          |                                                      |  |  |  |  |

| Postp                               | Postprocess received data:                               |          |                                                      |  |  |  |  |

| L                                   | МВ                                                       | 30       | Load memory byte 30 and                              |  |  |  |  |

| L                                   | MB                                                       | 37       | load memory byte 37;                                 |  |  |  |  |

| +                                   | I                                                        |          | add the values as integer data type and              |  |  |  |  |

| T                                   | MW                                                       | 100      | transfer the result to memory byte 100.              |  |  |  |  |

|                                     |                                                          |          |                                                      |  |  |  |  |

### User data transfer in STOP mode

The user data in the intermediate memory is processed differently depending on whether the DP master or the DP slave (BM 147 CPU) goes into STOP mode.

- The BM 147 CPU goes into STOP mode: The data in the intermediate memory (outputs only from the slave's viewpoint) of the BM 147 CPU are overwritten with "0"; i.e. the DP master or a recipient in direct communication reads "0".

- If the DP master goes into STOP mode: The current data in the intermediate memory of the BM 147 CPU (inputs in the slave, outputs in the master) are retained and can be read out in the user program of the BM 147 CPU.

### IM 308-C as the DP master (SIMATIC S5)

If you use an IM 308-C as the DP master, the following applies to the interchange of consistent data:

You must program FB 192 in the IM 308-C to enable the transfer of consistent data between the DP master and the DP slave. The effect of FB 192 is that the data is only output or read out by the ET 200X continuously in a single block.

ET 200X in the PROFIBUS Network

3

### Introduction

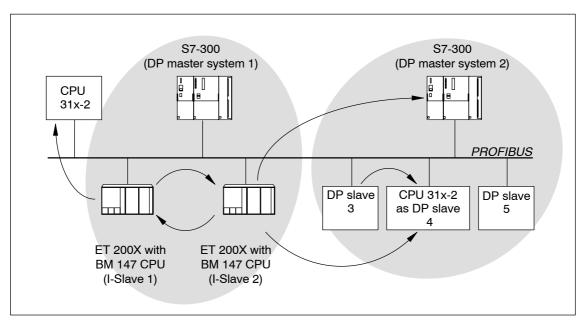

You can integrate the ET 200X with the BM 147 CPU as a node in a PROFIBUS network. This chapter contains a description of a typical network configuration with the BM 147 CPU. It also tells you which functions can be executed via the PD or OP on the ET 200X and which options are available for direct connection. The available communication utilities can be found in Section 7.8.

### **Equidistance**

As of *STEP 7* V 5.2 + SP1, you can parameterize bus cycles of the same length (equidistant) for PROFIBUS subnets with BM 147 CPU. You will find a detailed description of the functions in the *Online Help for STEP 7*.

# In this chapter

| In Section | Contents                        |      |  |  |

|------------|---------------------------------|------|--|--|

| 3.1        | ET 200X in the PROFIBUS network | 3-2  |  |  |

| 3.2        | Network components              | 3-6  |  |  |

| 3.3        | PROFIBUS address                | 3-7  |  |  |

| 3.4        | Functions via the PD/OP         | 3-8  |  |  |

| 3.5        | Direct communication            | 3-11 |  |  |

### More information

You will find more information on the structure of networks in the manual for the DP master.

# 3.1 ET 200X in the PROFIBUS network

### Structure of a PROFIBUS network

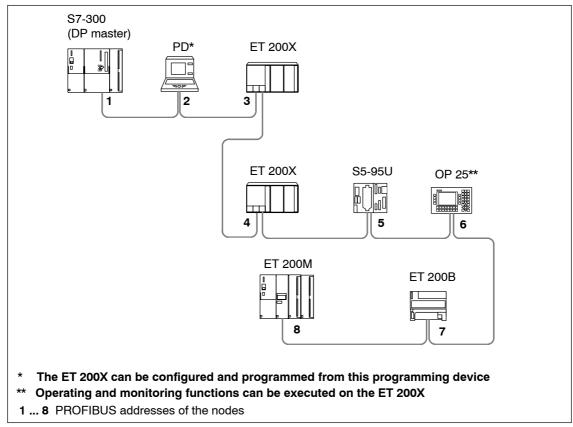

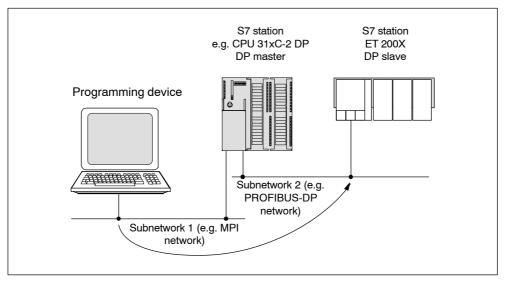

The figure below illustrates the basic structure of a PROFIBUS network with one DP master and several DP slaves.

Figure 3-1 Example of a PROFIBUS network

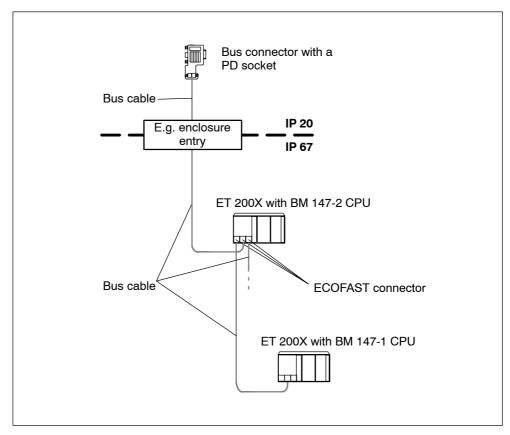

# Hardware requirements in the programming device/OP for accessing the ET 200X

Before you can access a BM 147 CPU from a programming device/operator panel, the programming device/operator panel must fulfill the following requirements:

- · it must have an integrated PROFIBUS-DP interface or DP card; or

- it must have an integrated MPI interface or MPI card.

### Access to the ET 200X

The BM 147 CPU is a passive/active bus node. The programs and configuration of the BM 147 CPU can be transferred to the BM 147 CPU by choosing "Load PLC" from the PD in SIMATIC Manager. All the other diagnostic and test functions are also possible with the PD.

If the PD is currently the only active bus node, this must be set beforehand in SIMATIC Manager by choosing the "Set PD/PC Interface" menu command (see Section 3.4).

However, you can still install OPs/OSs (operator panels/operator stations) as fixed components of the PROFIBUS network for operating and monitoring functions.

You cannot access an ET 200X from more than 12 devices in parallel:

- 1 connection is reserved for the PD.

- 1 connection is reserved for an OP or an OS.

- 10 connections are available as desired for PDs, OPs/OSs and CPUs.

We recommend that you allocate a PROFIBUS address to the PD/OP in the same way as for other network nodes (see Figure 3-1).

### Active/passive DP interface of the BM 147 CPU

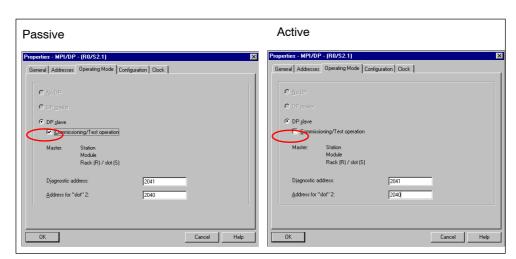

You set the mode of the DP interface at the BM 147 CPU during configuration in the **Properties – MPI/DP** window:

Figure 3-2 Setting the mode of the DP interface at the BM 147 CPU

Depending on the DP interface setting, the BM 147 CPU will behave in the following way:

Table 3-1 Behavior of the BM 147 CPU depending on the DP interface setting

|                                     | DP interface of the BM 147 CPU |           |  |  |

|-------------------------------------|--------------------------------|-----------|--|--|

|                                     | Passive                        | Active    |  |  |

| Transmission rate detection         | Yes                            | No        |  |  |

| Testing and commissioning functions | Slow                           | Fast      |  |  |

| Bus cycle time                      | Fast                           | Slow      |  |  |

| Diagnosis via BF LED                | See Sec                        | ction 6.4 |  |  |

| Routing (only for BM 147-2 CPU)     | No                             | Yes       |  |  |

### Maximum data transfer rate and cable length with a PD connecting cable

You can obtain a maximum data transfer rate of 1.5 Mbaud using the PD connecting cable. The cable length may not exceed 3 meters.

The PD connecting cable should only be connected for an extended period of time during startup and service.

Data transfer rates over 1.5 MBaud require an active connecting cable for the PD connection (for order information, see Appendix A).

### Note

A PD connecting cable on the X03 interface forms a spur line to the X01 and X02 interfaces. In this way, for example, an error for this DP segment can be output through use of a diagnosis repeater. Therefore, you should also use an active spur line for baud rates lower than or equal to 1.5 MBaud (for order information, see Appendix A).

# Examples of PD/OP connection to ET 200X

The PD/OP is connected to the PROFIBUS-DP interface of the DP master, but can be connected just as well to any other station in the DP network, including the ET 200X.

Figure 3-3 PD/OP accesses the ET 200X via the DP interface in the DP master

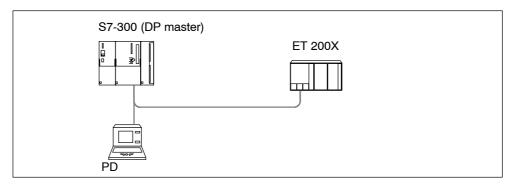

• The PD is directly connected to the ET 200X (you don't add the ET 200X to the PROFIBUS network until later).

**Note:** Depending on the DP interface (active/passive), a special setting is required in *STEP 7* (see Section 3.4).

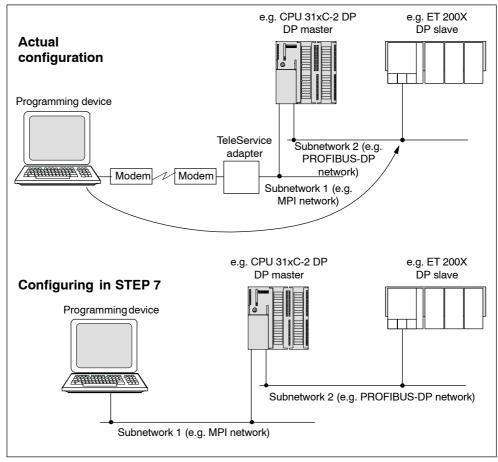

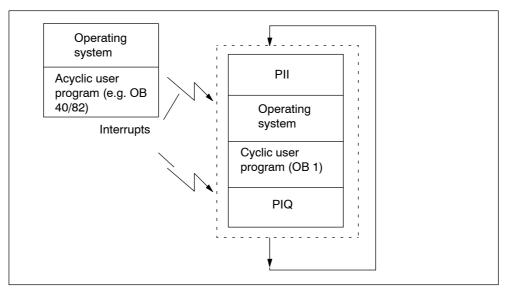

Figure 3-4 The PD directly accesses the ET 200X