# **SIEMENS**

# **SIMATIC S5**

# **Counter Module**

- IP 242A With FB 178/179/180/181/182

- IP 242B WithFB 183/184

**Equipment Manual**

Release: 02

Order No: 6ES5 998-0KM21

Subject to change without notice

© Siemens AG 1993, 1996 All rights reserved

| Introduction                                           |    |

|--------------------------------------------------------|----|

| General Function<br>Description                        | 1  |

| Hardware Settings                                      | 2  |

| Software Settings<br>(Registers)                       | 3  |

| Guidelines for Interrupt<br>Processing                 | 4  |

| Putting the Counter Module into Operation              | 5  |

| Control Words                                          | 6  |

| Special Functions                                      | 7  |

| Calculation Functions                                  | 8  |

| Operation Modes                                        | 9  |

| Technical Specifications                               | 10 |

| Programming Instructions, FB 178/179                   | 11 |

| Program Example for IP 242A                            | 12 |

| Programming Instructions, FB 180/181/182               | 13 |

| Programming Instructions, FB 183/184                   | 14 |

| Program Example for IP 242B                            | 15 |

| Function Blocks FB 38 and FB 39 (Only for PLC S5–115U) | 16 |

| Glossary                                               | 17 |

| Index                                                  | 18 |

| IP 242B with S7-400<br>(Appendices A, B, C)            | 19 |

| Suggestion Form                                        | 20 |

#### Note

For reasons fo clarity, this manual cannot cover all details of the modules or describe every conceivable situation concerning installation and operation. Contact your local Siemens of fice for more information should special questions arise.

The contents of this documentation are not part of a previous or existing agreement, promise or legal relationship, and are not intended to change same.

All obligations on the part of Siemens are based on the applicable sales contract which contains the complete and solely valid warranty regulations. The warranty regulations in the contact are neither expanded or restricted by the information in this manual.

Subject to change without notice. Siemens Aktiengesellschaft

Although the contents of this publication have been checked for agreement with the hardware and software described, total agreement is not guaranteed since deviations cannot be completely excluded. The information in this publication is checked at regular intervals and necessary corrections included in the next release. Your suggestions for improvement are welcome.

#### © Copyright Siemens AG 1993, 1996 All Rights Reserved

Passing on and reproduction of these documents, or utilization and disclosure of their contents is prohibited unless specifically authorized. Violations are cause for damage liability. All rights reserved, particularly in the event a patent is issued or a utility–model patent registered.

# ENVIRONMENTAL PROTECTION IN ACTION

# **Information Concerning Packaging Material/Notes on Disposal**

#### **Dear Customer!**

Our high-quality products cannot reach you safely without effective protective packaging. The size of the packaging is kept to an absolute minimum.

All our packaging materials are harmless to the environment and can be disposed of without danger.

Wood is not chemically treated.

Cardboard is made primarily of waste paper which can then be torn up and given to a waste paper collection.

Sheeting is made of polyethylene (PE), tapes of polypropylene (PP) and CFC-free padding of foamed polystyrene (PS).

These materials are pure hydrocarbons and can be recycled. Please dispose of these valuable secondary raw materials at a recycling center.

Recycling saves raw materials and cuts down on the amount of trash.

Ask your city administration for the address of the recycling center nearest you to dispose of packing materials and discarded devices.

Thank you for your help!

# SIEMENS

## Warning

Risks involved in the use of so-called SIMATIC-compatible modules of non-Siemens manufacture

"The manufacturer of a product (SIMATIC in this case) is under the general obligation to give warning of possible risks attached to his product. This obligation has been extended in recent court rulings to include parts supplied by other vendors. Accordingly, the manufacturer is obliged to observe and recognize such hazards as may arise when a product is combined with products of other manufacture.

For this reason, we feel obliged to warn our customers who use SIMATIC products not to install so-called SIMATIC-compatible modules of other manufacture in the form of replacement or add-on modules in SIMATIC systems.

Our products undergo a strict quality assurance procedure. We have no knowledge as to whether outside manufacturers of so-called SIMATIC-compatible modules have any quality assurance at all or one that is nearly equivalent to ours. These so-called SIMATIC-compatible modules are not marketed in agreement with Siemens; we have never recommended the use of so-called SIMATIC-compatible modules of other manufacture. The advertising of these other manufacturers for so-called SIMATIC-compatible modules wrongly creates the impression that the subject advertised in periodicals, catalogues or at exhibitions had been agreed to by us. Where so-called SIMATIC-compatible modules of non-Siemens manufacture are combined with our SIMATIC automation systems, we have a case of our product being used contrary to recommendations. Because of the variety of applications of our SIMATIC automation systems and the large number of these products marketed worldwide, we cannot give a concrete description specifically analyzing the hazards created by these so-called SIMATIC-compatible modules. It is beyond the manufacturer's capabilities to have all these so-called SIMATIC-compatible modules checked for their effect on our SIMATIC products. If the use of so-called SIMATIC-compatible modules leads to defects in a SIMATIC automation system, no warranty for such systems will be given by Siemens.

In the event of product liability damages due to the use of so-called SIMATIC-compatible modules, Siemens is not liable since we have taken timely action in warning users of the potential hazards involved in so-called SIMATIC-compatible modules."

R 04/96 Table of Contents

# **Table of Contents**

| 1    | General Function Description                                      |        |

|------|-------------------------------------------------------------------|--------|

| 1.1  | Features of Counter Module IP 242A/242B                           | 1 – 1  |

| 1.2  | Hardware Description                                              | 1 – 3  |

| 1.3  | 16-Bit Counter                                                    | 1 – 4  |

| 1.4  | Inputs of Counters 1 to 5                                         | 1 – 5  |

| 1.5  | 24/32-Bit Up/Down Counter                                         | 1 – 6  |

| 1.6  | Inputs of Counters 6 and 7                                        | 1 – 7  |

| 1.7  | Gate Control Logic                                                | 1 – 9  |

| 1.8  | Outputs of All Counters                                           | 1 – 12 |

| 1.9  | Comparator Function                                               | 1 – 14 |

| 1.10 | Reference Frequency                                               | 1 – 20 |

| 1.11 | Switching of Counters Among Each Other                            | 1 – 22 |

| 1.12 | Command Lists and Measured Value Memory                           | 1 – 22 |

| 1.13 | Calculation Functions (For IP 242B Only)                          | 1 – 24 |

| 2    | Hardware Settings                                                 |        |

| 2.1  | Layout of the Setting Elements                                    | 2 – 1  |

| 2.2  | Setting of the Module Address                                     | 2 – 2  |

| 2.3  | Interrupts and Process Interrupts                                 | 2 – 4  |

| 2.4  | Level Conditioning of Counter Inputs 1 to 5                       | 2 – 7  |

| 2.5  | Frequency Conditioning for Counter Frequencies of Counters 1 to 5 | 2 – 8  |

| 2.6  | Front Panel and Front Connectors                                  | 2 – 9  |

| 3    | Software Settings (Registers)                                     |        |

| 3.1  | Overview of the Registers                                         | 3 – 1  |

| 3.2  | Definition of the Registers                                       | 3 – 2  |

| 3.3  | Description of the Global Registers                               | 3 – 4  |

| 3.4  | Description of the Counter Registers                              | 3 – 13 |

| 3.5  | Description of the Registers for the Calculation Functions        | 3 – 20 |

| 3.6  | Description of the Registers for Additional Command Lists         | 3 – 21 |

| 3.7  | Description of the Registers for Measured Values                  | 3 – 22 |

| 3.8  | Description of the Information Registers                          | 3 – 25 |

| 3.9  | Basic Settings                                                    | 3 - 30 |

| 4   | Guidelines for Interrupt Processing                                      |        |

|-----|--------------------------------------------------------------------------|--------|

| 4.1 | What Is an Interrupt?                                                    | 4 – 1  |

| 4.2 | Interrupts via Interrupt Lines                                           | 4 – 2  |

| 4.3 | Interrupts via Intput Byte IB 0                                          | 4 – 3  |

| 4.4 | Interrupts via Interrupt Lines and Evaluation via Input Byte IB 0        | 4 – 6  |

| 4.5 | Reaction Times for Interrupts                                            | 4 – 7  |

| 4.6 | Sources of Interrupts                                                    | 4 – 9  |

| 4.7 | The Best Way to Proceed                                                  | 4 – 10 |

| 5   | Putting the Counter Module into Operation                                |        |

| 5.1 | Guidelines for Putting into Operation                                    | 5 – 1  |

| 5.2 | Start-Up Behavior of the Counter Module/Meaning of the LEDs              | 5 – 3  |

| 5.3 | Switching the Counters with Each Other                                   | 5 – 3  |

| 6   | Control Words                                                            |        |

| 6.1 | General Module Functions                                                 | 6 – 1  |

| 6.2 | Calculation Functions                                                    | 6 – 27 |

| 7   | Special Functions                                                        |        |

| 7.1 | Cascading (Counters 1 to 5)                                              | 7 – 1  |

| 7.2 | Command Lists for Interrupt Processing                                   | 7 – 3  |

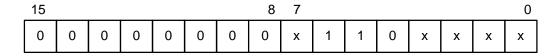

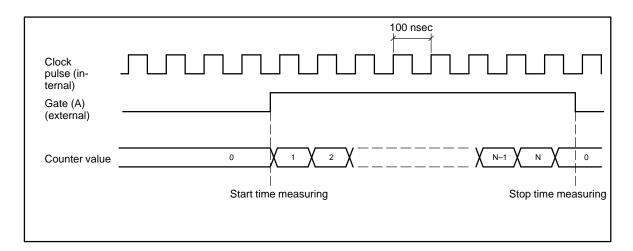

| 7.3 | Time Measurement (Counters 1 to 5)                                       | 7 – 5  |

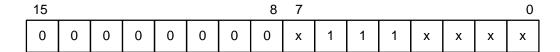

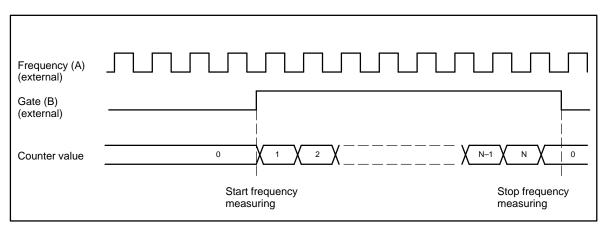

| 7.4 | Frequency Measurement (Counters 1 to 5)                                  | 7 – 9  |

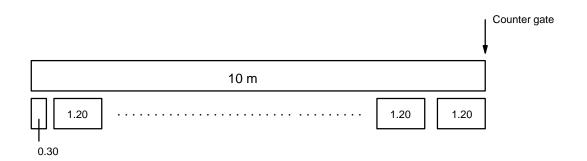

| 7.5 | Velocity Measurement with Light Barriers (Counters 1 to 5)               | 7 – 13 |

| 7.6 | Synchronization / Zero Point Shift (Counters 6 and 7)                    | 7 – 14 |

| 7.7 | Read Counter Status Via Edge on External Input                           | 7 – 15 |

| 8   | Calculation Functions                                                    |        |

| 8.1 | General                                                                  | 8 – 1  |

| 8.2 | Conversion of Counting Values to Physical Numbers                        | 8 – 3  |

| 8.3 | Adjustment of the Counting Values to Physical Numbers Via Gearing Factor | 8 – 7  |

| 8.4 | Compare Two Counter Values/Results                                       | 8 – 8  |

| 8.5 | Start a Counter with the Adjusted Counter Value of a Second Counter      | 8 – 11 |

| 8.6 | Buffering Results                                                        | 8 – 13 |

| 8.7 | Prepare for Load in a Command List with Conditional Jumps                | 8 – 15 |

| 9   | Operation Modes                                                          |        |

| 9.1 | Operating Modes for Counters 1 to 5                                      | 9 – 1  |

| 9.2 | Operating Modes for Counters 6 and 7                                     | 9 – 42 |

|     |                                                                          |        |

| 10    | Technical Specifications                           |         |

|-------|----------------------------------------------------|---------|

| 10.1  | Inputs for Counters 1 to 5                         | 10 – 1  |

| 10.2  | Inputs for Counters 6 and 7                        | 10 – 2  |

| 10.3  | Digital Outputs (P Switch)                         | 10 – 3  |

| 10.4  | Counting Frequencies                               | 10 – 4  |

| 10.5  | Power Supply                                       | 10 – 5  |

| 10.6  | General Data                                       | 10 – 6  |

| 10.7  | Program and Data Memory                            | 10 – 6  |

| 10.8  | Processing Times for Control Words                 | 10 – 7  |

| 10.9  | Basic Plug Connector Allocation                    | 10 – 14 |

| 10.10 | Stub Line for Siemens Incremental Encoder          | 10 – 15 |

| 10.11 | 24 V Asymmetric To 5 V (RS422) Symmetric Converter | 10 – 16 |

| 10.12 | In Which Slots Can the Counter Module Be Operated? | 10 – 18 |

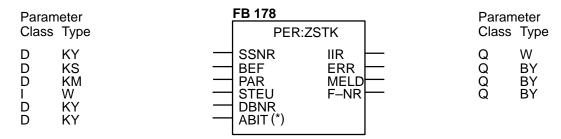

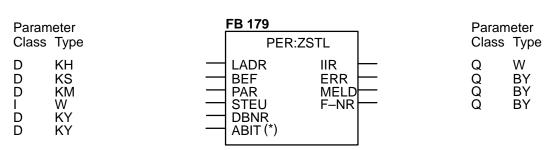

| 11    | Programming Instructions, FB 178/179               |         |

| 11.1  | Overview                                           | 11 – 1  |

| 11.2  | Function Description                               | 11 – 2  |

| 11.3  | Calling Function Blocks FB 178 and FB 179          | 11 – 3  |

| 11.4  | Explanation of the Parameters                      | 11 – 4  |

| 11.5  | Assignment of the Parameters                       | 11 – 5  |

| 11.6  | Assignment of the Data Area                        | 11 – 10 |

| 11.7  | Technical Specification                            | 11 – 14 |

| 11.8  | Application of the Funktion                        | 11 – 16 |

| 11.9  | Error Evaluation                                   | 11 – 20 |

| 11.10 | Interrupt Processing                               | 11 – 22 |

| 11.11 | Start-Up Behavior                                  | 11 – 25 |

| 11.12 | Multiprocessor Operation                           | 11 – 26 |

| 12    | Program Example for IP 242A                        |         |

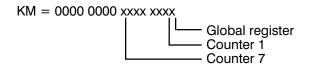

| 12.1  | General                                            | 12 – 1  |

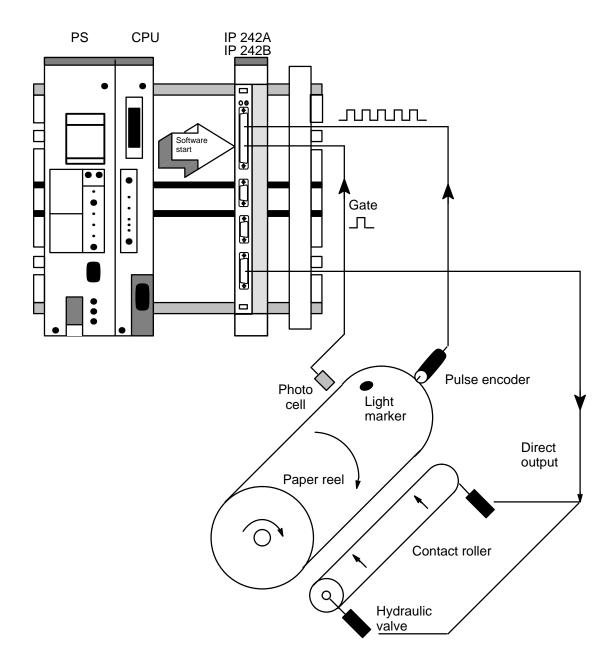

| 12.2  | Device Configuration                               | 12 – 2  |

| 12.3  | Jumper Allocation for Counter Module IP 242A       | 12 – 3  |

| 12.4  | Allocation of the Inputs and Outputs               | 12 – 4  |

| 12.5  | Allocation of the Flag Area                        | 12 – 6  |

| 12.6  | Allocation of the Data Area                        | 12 – 6  |

| 12.7  | Turn-On, Start-Up Behavior                         | 12 – 7  |

| 12.8  | Cyclic Operation                                   | 12 – 7  |

| 12.9  | Processing of Interrupts                           | 12 – 13 |

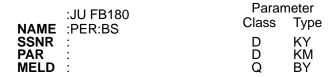

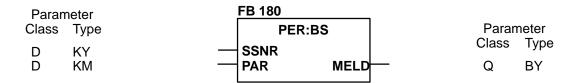

| 13    | Programming Instructions, FBs 180/181/182              |         |

|-------|--------------------------------------------------------|---------|

| 13.1  | Overview                                               | 13 – 1  |

| 13.2  | Function Description                                   | 13 – 2  |

| 13.3  | Calling Function Blocks FB 180, FB 181 and FB 182      | 13 – 3  |

| 13.4  | Explanation of the Parameters                          | 13 – 4  |

| 13.5  | Assignment of the Parameters                           | 13 – 5  |

| 13.6  | Technical Specifications                               | 13 – 7  |

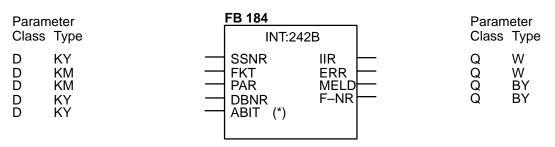

| 14    | Programming Instructions, FB 183/184                   |         |

| 14.1  | Overview                                               | 14 – 1  |

| 14.2  | Function Description                                   | 14 – 2  |

| 14.3  | Calls of Function Block FB 183 and FB 184              | 14 – 3  |

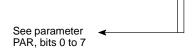

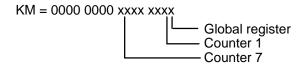

| 14.4  | Explanation of the Parameters                          | 14 – 4  |

| 14.5  | Assignment of the Parameters                           | 14 – 5  |

| 14.6  | Assignment of the Data Area                            | 14 – 11 |

| 14.7  | Technical Specifications                               | 14 – 18 |

| 14.8  | Use of Function Block FB 183                           | 14 – 22 |

| 14.9  | Application of Function Block FB 184                   | 14 – 29 |

| 14.10 | Error Evaluation                                       | 14 – 31 |

| 14.11 | Interrupt Processing                                   | 14 – 33 |

| 14.12 | Startup Behavior                                       | 14 – 36 |

| 14.13 | Multi-Processor Operation                              | 14 – 37 |

| 15    | Program Example for IP 242B                            |         |

| 15.1  | General                                                | 15 – 1  |

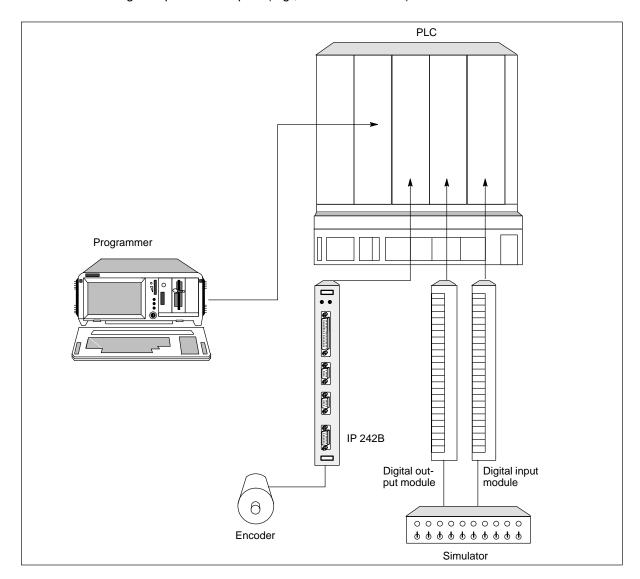

| 15.2  | Device Configuration                                   | 15 – 2  |

| 15.3  | Jumper Assignment of the IP 242B Counter Module        | 15 – 3  |

| 15.4  | Assignment of the Inputs and Outputs                   | 15 – 4  |

| 15.5  | Assignment of the Flag Area                            | 15 – 5  |

| 15.6  | Assignment of the Data Area                            | 15 – 5  |

| 15.7  | Switchon, Startup Behavior                             | 15 – 6  |

| 15.8  | Cyclic Operation                                       | 15 – 6  |

| 15.9  | Interrupt Processing                                   | 15 – 13 |

| 16    | Function Blocks FB 38 and FB 39 (Only for PLC S5-115U) |         |

| 16.1  | Overview                                               | 16 – 1  |

| 16.2  | Function Block FB 38                                   | 16 – 1  |

| 16.3  | Function Block FB 39                                   | 16 – 7  |

| 17    | Glossary                                               | 17 – 1  |

| 18    | Index                                                  | 18 – 1  |

R 04/96 Table of Contents

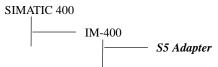

| Α   | Adapter Module (S5 Adapter)                         | <b>A</b> – 1 |

|-----|-----------------------------------------------------|--------------|

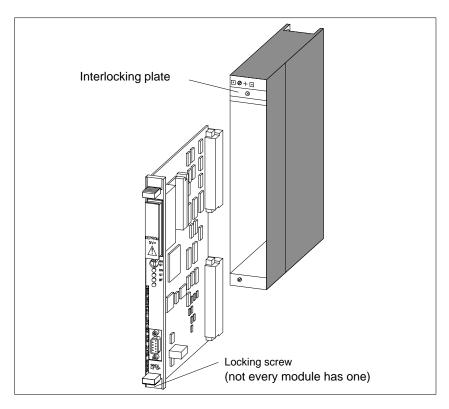

| A.1 | Prerequisites                                       | A-2          |

| A.2 | Installing an Adapter Module in an S7-400           | A-3          |

| A.3 | Inserting S5 Modules in the Adapter Module          | A – 4        |

| A.4 | Interrupt Processing                                | A – 5        |

| A.5 | Technical Specifications                            | A – 6        |

| В   | Addressing S5 Modules (Adapter Module and IM 463-2) | B – 1        |

| B.1 | Addressing S5 Modules                               | B – 2        |

| С   | IP 242B Counter Module                              | C – 1        |

| C.1 | Overview                                            | C – 2        |

| C.2 | Counter Processing Blocks                           | C – 4        |

| C.3 | Programming Example                                 | C – 12       |

R 02/93 Introduction

# Introduction

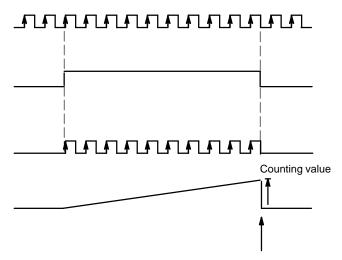

#### **Principle of Counting**

Counting is primarily the acquisition and addition of events. In the field of electronics, this is the addition of pulses.

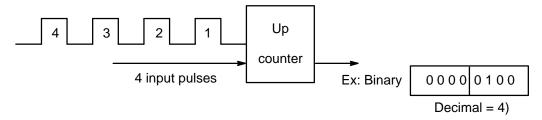

#### **Counting Up**

This type of counting is used, for example, for the acquisition of a simple piece count.

The AM 9513A counting chip on the IP 242A/242B, however, allows the counter to be used in a great variety of ways.

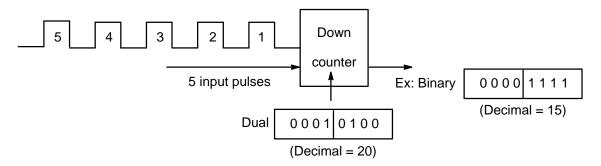

#### **Counting Down**

Starting with an initial value stored in a register (memory location) on the IP, the counter is decremented when a pulse occurs.

This type of counting is used, for example, when you want to count out an exact quantity and then package it. The counter is equipped with an output signal which allows you to close a valve, for example, when the counter reaches zero.

Introduction R 02/93

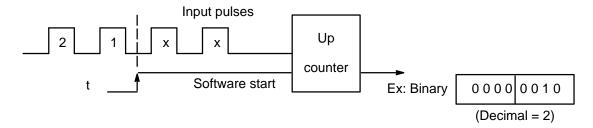

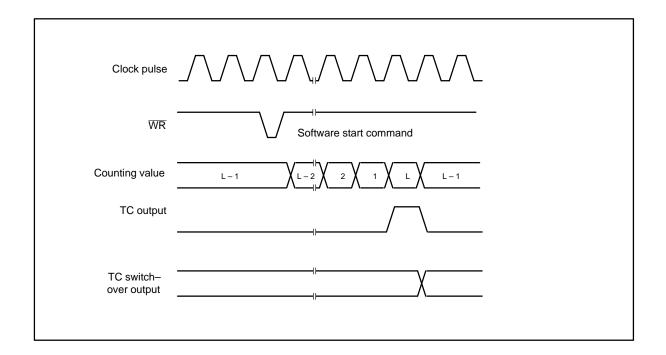

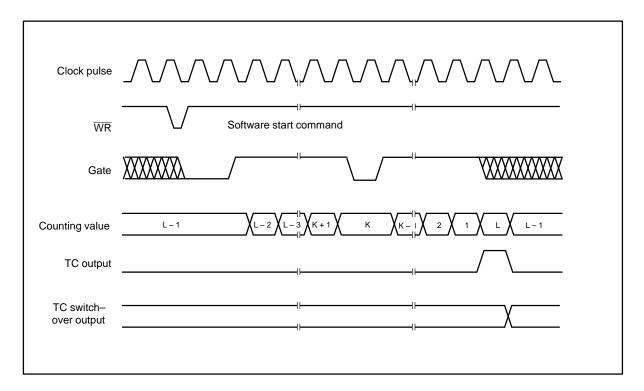

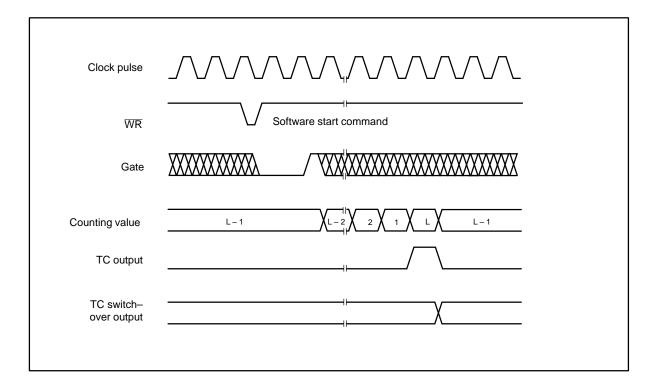

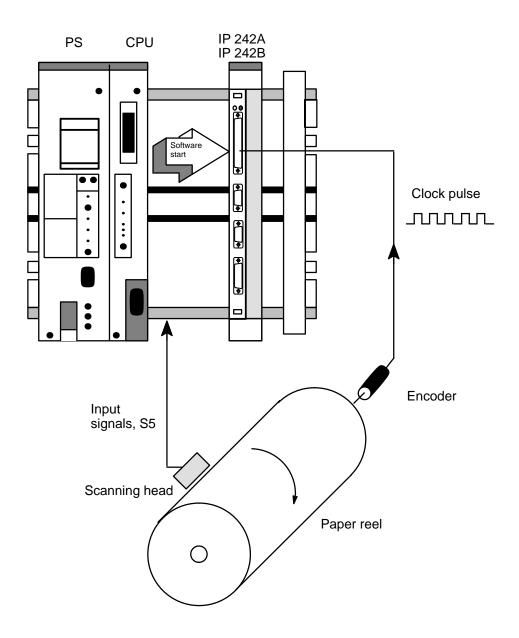

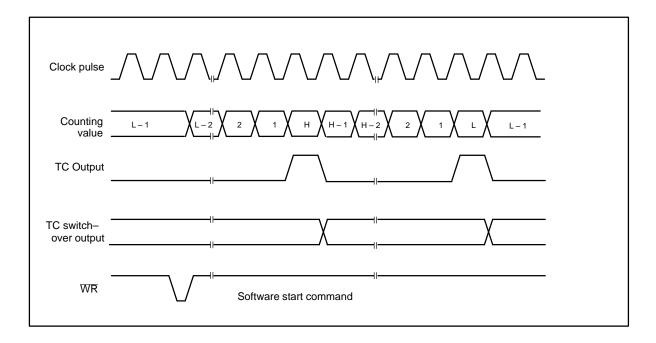

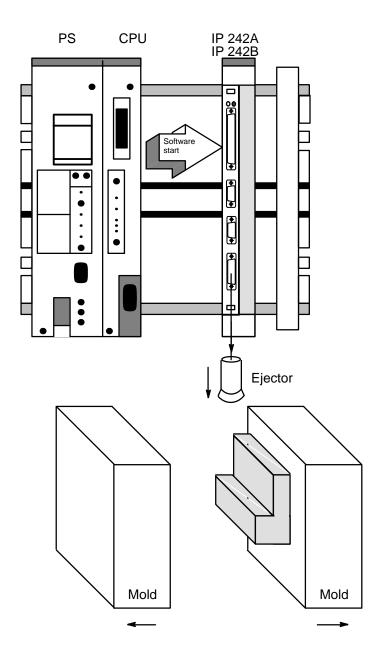

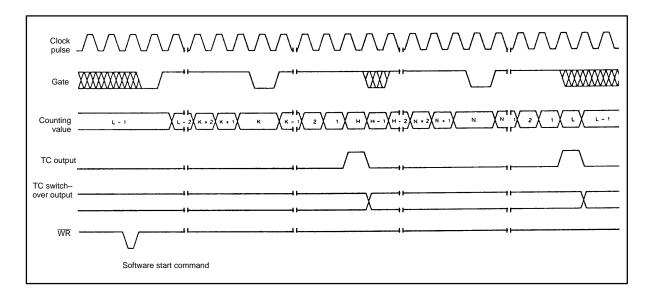

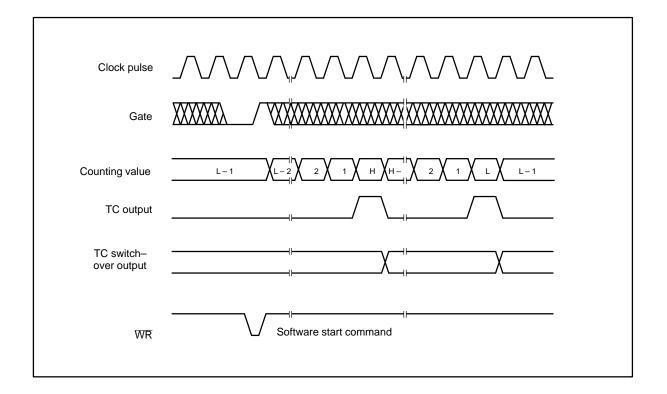

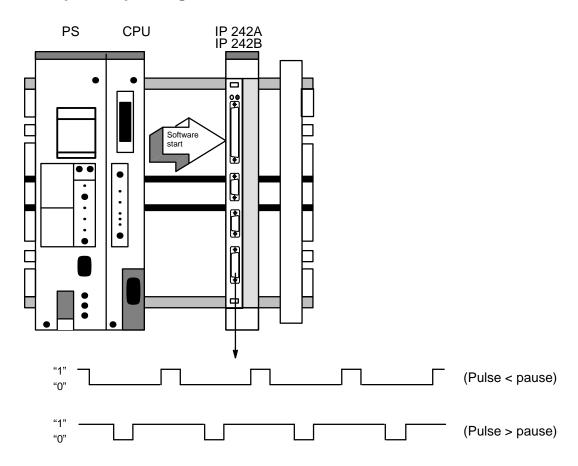

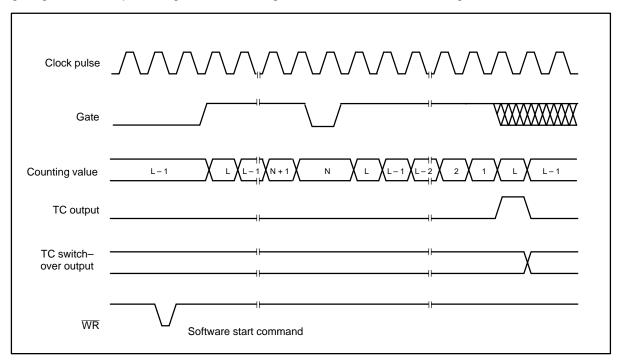

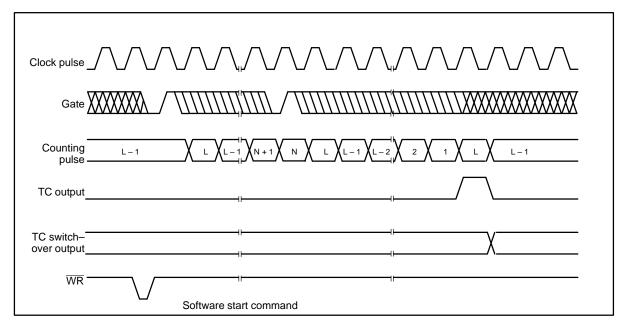

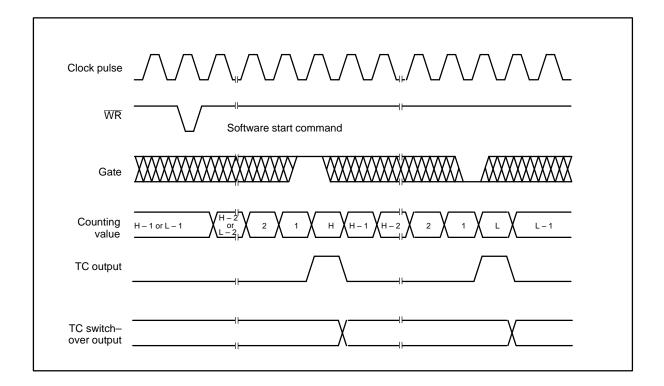

#### **Counting with Software Start (Or Software Stop)**

It is often necessary to link the pulses starting at a defined point in time depending on other input values, and to start the counter with this collective information.

This is used, for example, when you know that the first products will have a different shape, color, quality of material or other deviations from the serial product.

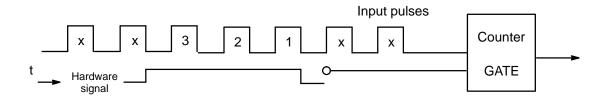

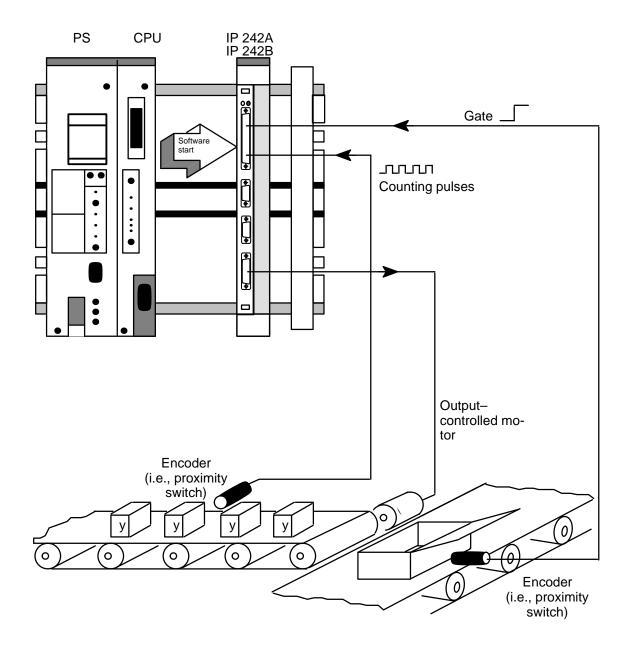

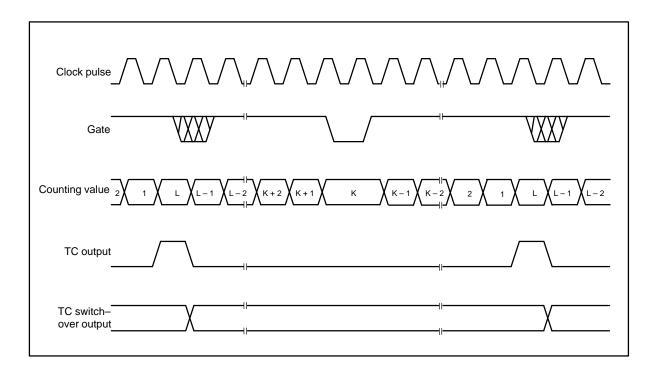

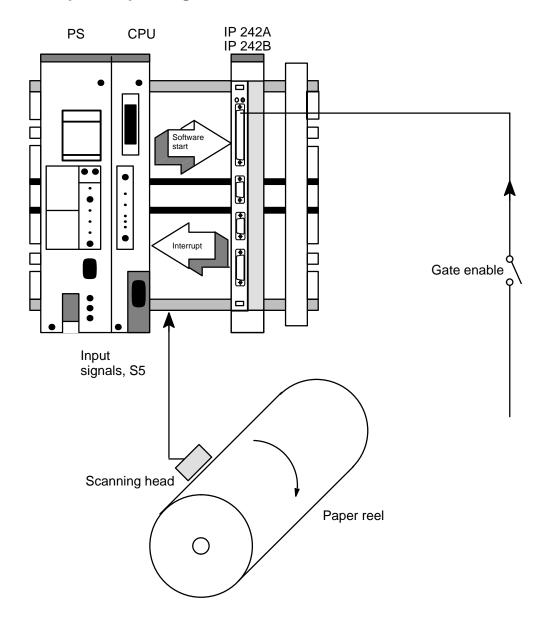

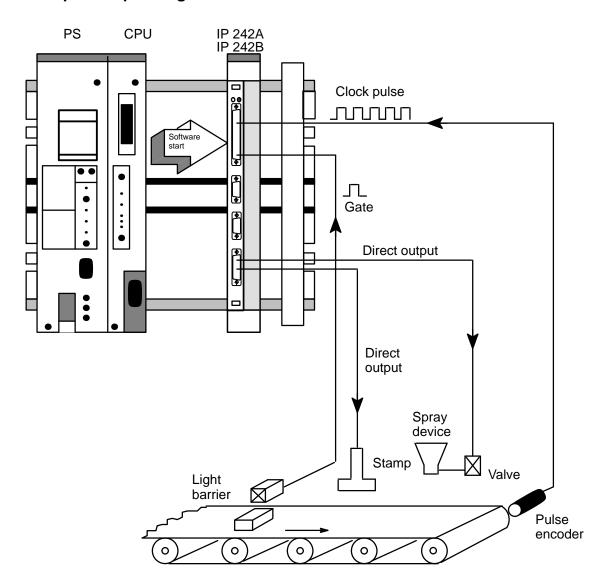

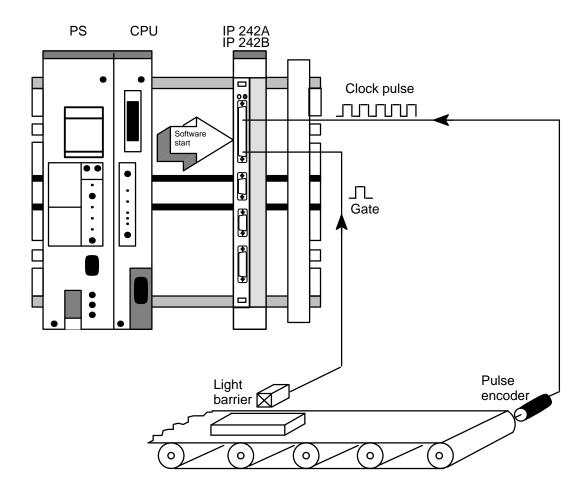

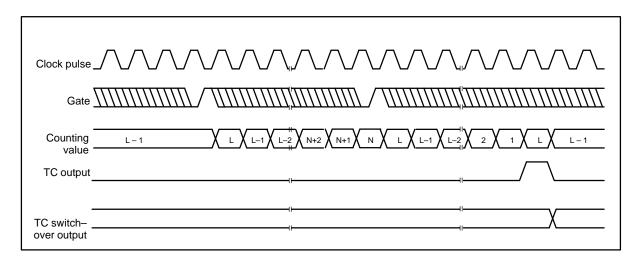

#### **Counting with Gate Signal**

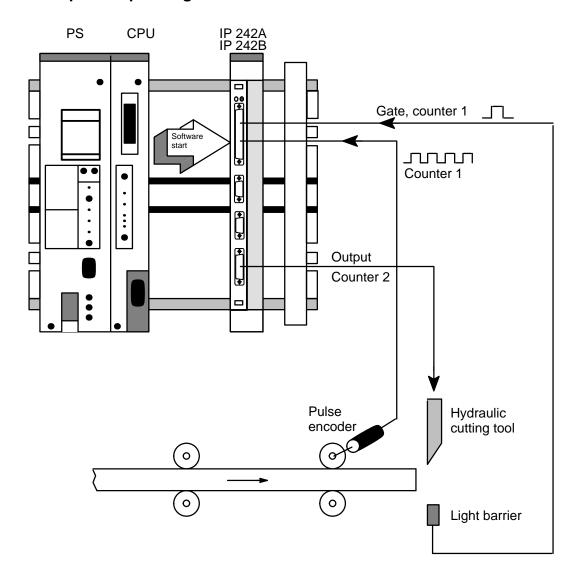

When a hardware signal directly from the system (i.e., from the process) is to start a high–speed counting procedure, it is best to connect this signal directly to the counter. This allows counting without occupying the S5 cycle.

Here, the gate provides a defined stop of the counting procedure.

#### **One-Time Counting**

After a software start, the counter is started with the value stored in the load register, and begins counting starting with this value.

The counter is stopped by the following.

- Overflow of the counter

- Underflow of the counter

The counter remains stopped until another software start occurs.

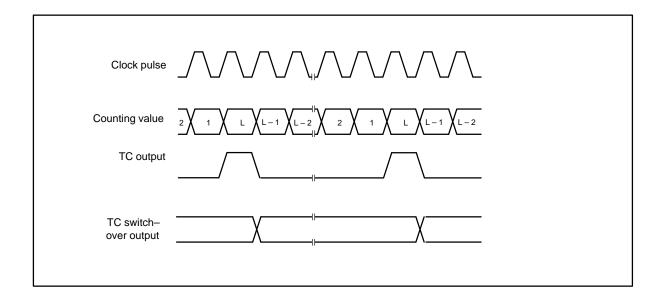

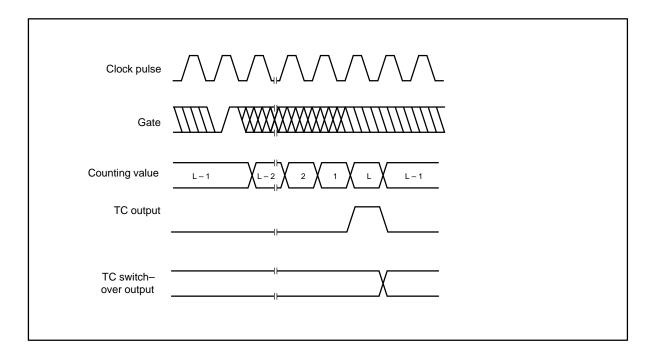

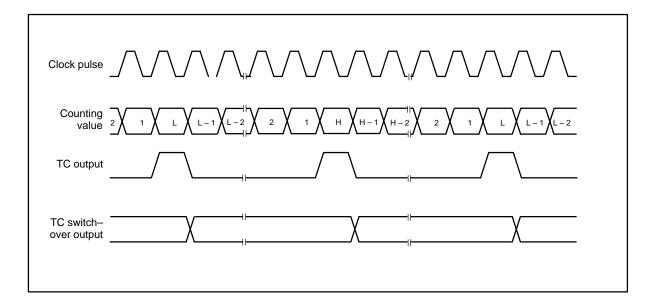

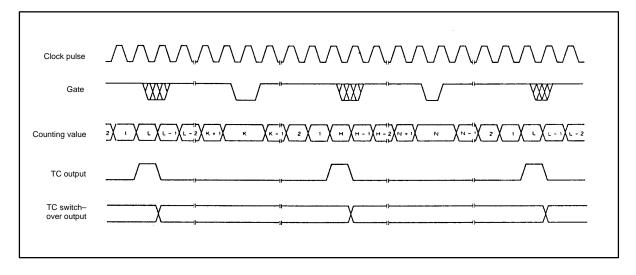

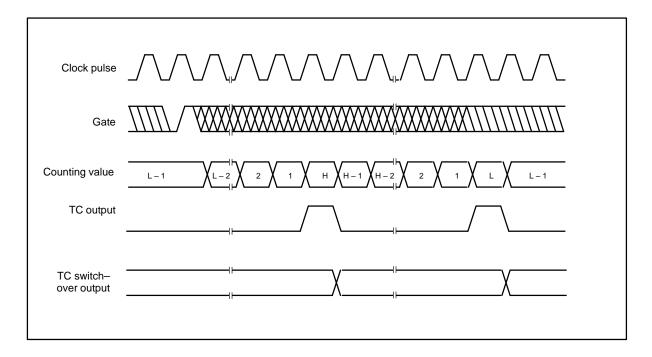

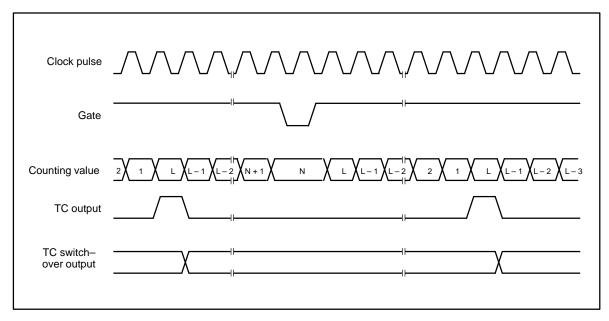

#### **Cyclic Counting**

After a software start, the counter is started with the value stored in the load register, and begins counting starting with this value.

When a counting range limit is exceeded (overflow or underflow), the counter is loaded with the load value again, and resumes counting starting with this value. Another software start is not required here.

R 02/93 Introduction

#### **Setup of This Manual**

This equipment manual furnishes extensive information on the installation and operation of the IP 242A and IP 242B modules.

Before starting work with the module, please take the time to look through this equipment manual. Feel free to spend more time on the passages which are of particular interest to you. We want to give you a general feel of the subject matter and an overview of the information this manual provides.

Each section is self-contained and provides information on one of the following aspects of the module.

- Installation

- Programming (parameterization)

- Handling (operating)

In particular, you will find information concerning your special applications of the module in the following sections.

| User group       | IP 242A                      | IP 242B                     |

|------------------|------------------------------|-----------------------------|

| First-time user  | 2, 3, 5, 6, 7, 9, 11, 12, 13 | 2, 3, 5, 6, 7, 8, 9, 14, 15 |

| Experienced user | 3, 6, 7, 11, 12, 13          | 3, 6, 7, 8, 14, 15          |

| Specialist       | IP 242A Short Instructions   | IP 242B Short Instructions  |

The following criteria have been used to divide the users into groups.

**Experienced users** have accumulated experience in handling SIMATIC S5 controllers and counter modules. **Specialists** are experienced users who have had long years of experience in handling SIMATIC S5 controllers and IP modules.

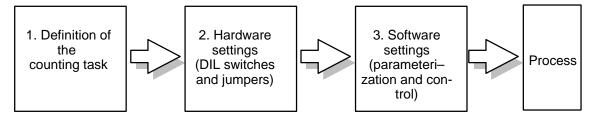

All steps required to commission the module are listed in section 5. These steps must be performed in the order given.

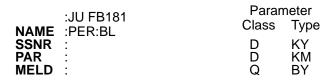

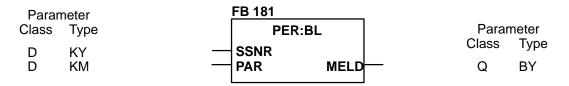

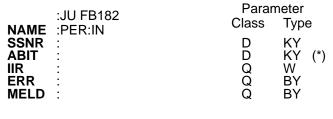

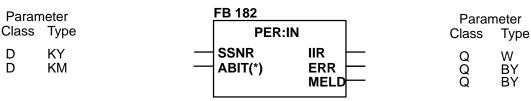

Section 13 contains the programming instructions for **standard function block FB 180**, **FB 181 and FB 182**. These blocks can be used for fast handling of the IP 242A module in the interrupt branch (e.g., OB 2). The commands which use these function blocks have significantly shorter load times than the call in standard function blocks FB 178 and FB 179.

**Function blocks FB 38 and FB 39** are used to save or load the scratchpad flags/system data, and the page frame number during interrupt processing in PLC S5–115U. They can be used for both the IP 242A and IP 242B.

Introduction R 02/93

#### Differences Between the IP 242A and IP 242B

Counter modules IP 242A and IP 242B are equipped with the same hardware.

In functionality, the IP 242B module is a direct extension of the IP 242A. This applies in particular to the following areas.

- Implementation of calculation functions directly on the IP 242B

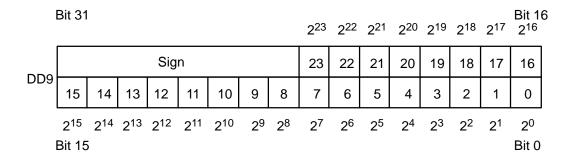

- Expansion of the counting length of counters 6 and 7 from 24 bits to 32 bits

- Storage of up to eight parameterization data records in the EEPROM of the IP 242B

- Provision of a measured value memory with trace function (collection of past values)

Standard function blocks FB 178 to FB 182 for the IP 242A cannot be used with the IP 242B. Similarly, function blocks FB 183 and FB 184 for the IP 242B cannot be used with the IP 242A.

| Module  | Corresponding FB  |

|---------|-------------------|

| IP 242A | FB 178 to FB 182  |

| IP 242B | FB 183 and FB 184 |

The IP module does not respond to function blocks other than those assigned to it as stated above.

R 02/93 Introduction

#### Upgrading an IP 242A to an IP 242B

Since the IP 242A and IP 242B modules are based on the same hardware, the firmware of the IP 242B can also be run on the IP 242A.

This requires that the firmware EPROMs on your IP 242A be replaced. In addition, FB 183 and FB 184 must also be integrated in the S5 since the firmware of one module will not accept the function blocks of the other.

To make the change easier, the structure of the parameterization data block has been retained, and the new registers make use of the previously unused positions.

An upgrading kit is available from WKF under order number 764 22 716 for "upgraders".

#### Notes for First-Time Users

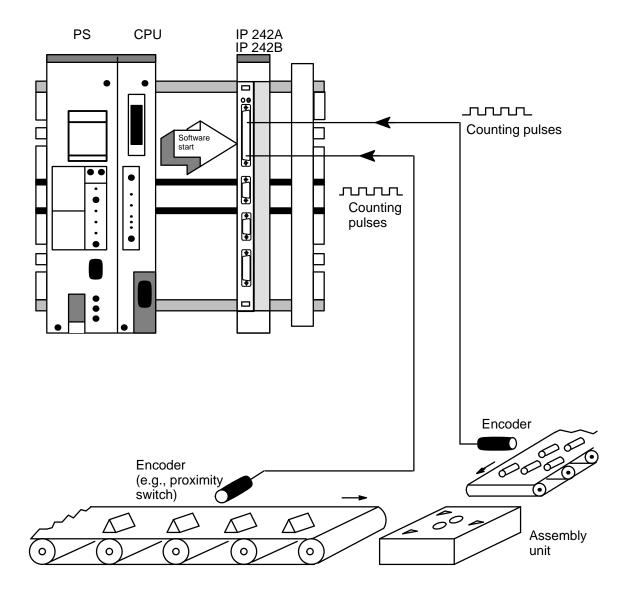

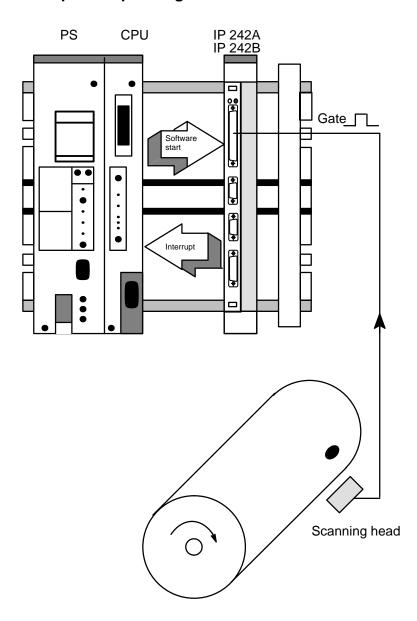

The IP 242A and IP 242B counter modules are used for the acquisition and conditioning of high–speed counting pulses.

They contain seven independent counters. Counters 1 to 5 can be switched on and off via external addressing of counting gate inputs or software starts/stops.

The initial values must be specified for the counters in the S5 program. The point in time at which these values are loaded in the counters can also made dependent directly on the external signals.

Each counter is equipped with an output with which it can report events such as, for example, overflow or end of counting. This message can be reported to the programmable controller both via an interrupt and externally via a hardware output.

This allows the counter module to be used as a link between high—speed events in the process, fast reactions and the program in the programmable controller.

However, not a single pulse is counted when counting and gate signals are applied to the front plug connector.

Introduction R 02/93

Why is such a conditioning module needed when counters programmable in STEP5 are available for all programmable controllers?

A simple consideration makes the limits of these software counters clear. For example, counting 50 Hz pulses requires that the programmable controller process the programming for the counter in time intervals of less than 10 msec. (Twice the processing speed is required since the software counter also has to acquire the falling edge of the counting signal in order to be able to recognize the rising edge of the same signal.) This means that the programming for counting (with direct access to the periphery) must be called several times.

#### Additional Reasons for Using the IP 242A/242B

- Separate gate inputs are available for each of counters 1 to 5.

- Edge or level-dependent counting procedures can be easily controlled on the counting and gate inputs.

- A choice of internal or external counting procedures is available. In addition, these can be combined.

- Counters 1 to 5 can be cascaded.

The counter module is equipped with seven counters. Each counter can be addressed externally and counters 1 to 5 can also be addressed internally.

#### **External Circuiting**

See section 2 for circuiting the inputs (from connection via signal conditioning to circuiting of the outputs).

R 02/93 Introduction

Use of the Internal Signals (For Counters 1 to 5 Only)

- Outputs of scaler 1 which scales the 1 MHz clock pulse of the quartz

- Output of scaler 2 (Possible inputs for scaler 2 are the outputs of scaler 1 or the external counting/gate inputs.)

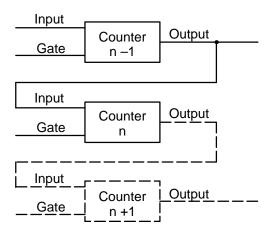

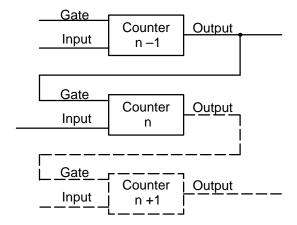

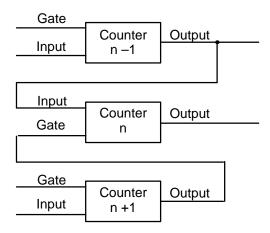

- Output of counter n-1 (counter cascading see \* below and section 7.6)

Use of the Internal Signals (For Counters 6 and 7 Only)

Introduction R 02/93

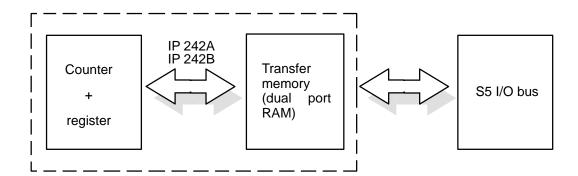

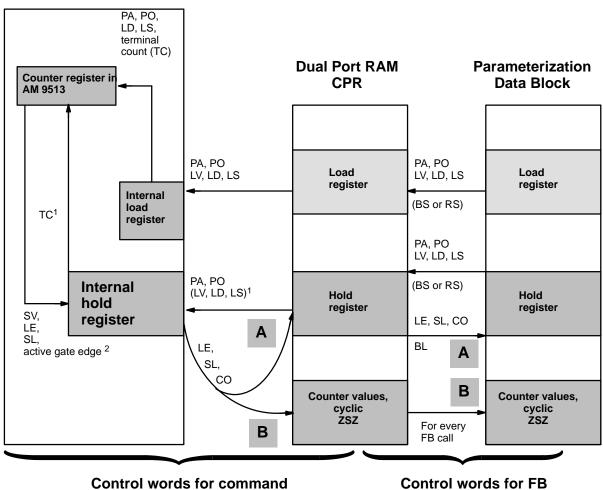

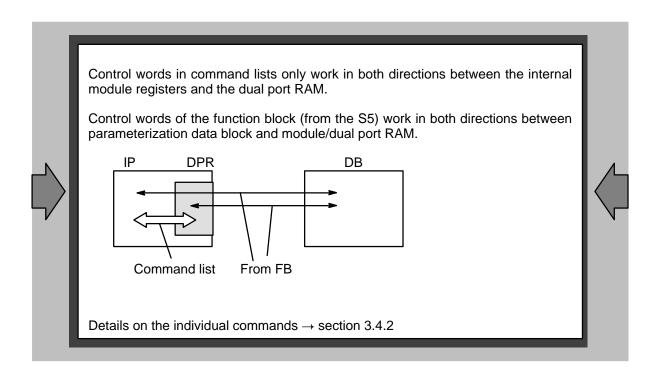

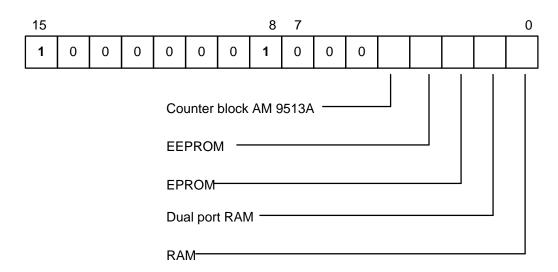

Each communication between the S5 and the IP 242A/242B is handled by a transfer memory (dual port RAM).

This data communication is handled as follows.

- Parameters are transferred from the CPU to the IP.

- Data are fetched by the CPU from the IP to the PLC.

The standard function blocks handle the organization of all accesses.

R 02/93 Introduction

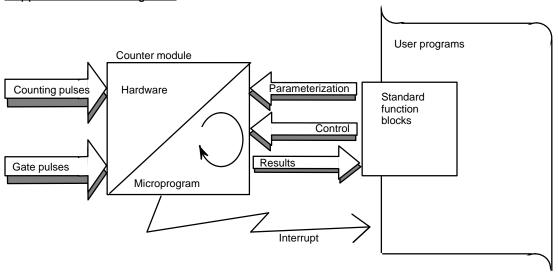

#### **Software Support**

In addition to the required hardware settings, each individual counter is supplied with the parameterization of the registers.

#### Support of the Counting Task

Because of the many conditions which must be adhered to (i.e., order, time requirements, etc.), writing your own program for the interaction between user program and counter module may cause problems.

Because of this, standard function blocks are provided for the user program—counter module interface.

Available Standard Function Blocks

IP 242A: FB 178 to FB 182 IP 242B: FB 183 and FB 184

A significant advantage of using the function blocks is the improved readability of the program. Complex relationships between user program and counter module are reduced to the defined environment of the function blocks and their calls.

The following must be specified by the user, however.

- Points in time of the call

- Conditions under which the call is made

Introduction R 02/93

#### Support of the Communication with the Programmable Controller

#### \*) With IP 242A only

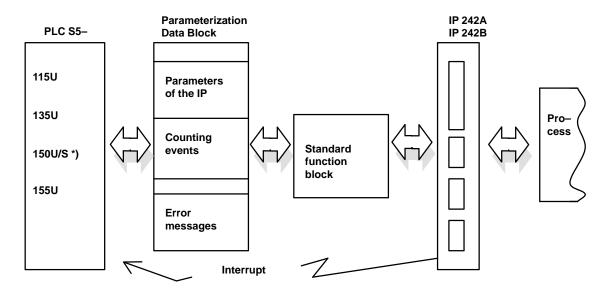

The IP 242A/242B uses standard function blocks to communicate with the programmable controller (PLC). In addition, interrupt lines (interrupt) can be used to react immediately to an event in the process (interrupt processing). The function blocks access the parameterization data block (i.e., the IP 242A/242B can be parameterized, controlled and monitored with these data blocks and the standard function blocks).

The parameterization data block must be set up in the PLC by the user, and provided with parameters.

R 02/93 Introduction

#### **Stipulations**

#### **Emphasis of Safety Notes**

Notes are identified as follows in this manual.

Texts in these boxes contain important information or instructions which must absolutely be adhered to to ensure safe functioning and protection of the module.

Texts in these boxes contain information and notes which require particular attention.

#### **Abbreviations**

Abbreviations which are not part of everyday usage are written out in full the first time they appear. See the glossary for a list of the abbreviations used.

#### **Cross References**

Cross references are not made to parts of other sections unless repetition of the information would require too much space, and it can be assumed that the description at another location is sufficient. Cross references to parts of other sections are made by specifying the section number (e.g., "→ section 2.1").

#### Symbols Used

The symbols **A** and **B** in the margin of the text indicate sections of the text which only apply to the corresponding module.

- **A** for IP 242A

- **B** for IP 242B

In addition, the title of each section includes a note to the right of the title indicating which module this section applies to (if differences exist). See examples below.

All unmarked passages apply without restrictions to both the IP 242A and the IP 242B.

# **General Function Description**

| 1.1                            | Features of Counter Module IP 242A/242B  | 1 – 1                                |

|--------------------------------|------------------------------------------|--------------------------------------|

| 1.2                            | Hardware Description                     | 1 – 3                                |

| 1.3                            | 16-Bit Counter                           | 1 – 4                                |

| 1.4                            | Inputs of Counters 1 to 5                | 1 – 5                                |

| 1.5                            | 24/32–Bit Up/Down Counter                | 1 – 6                                |

| 1.6                            | Inputs of Counters 6 and 7               | 1 – 7                                |

| 1.7                            | Gate Control Logic                       | 1 – 9                                |

| 1.8                            | Outputs of All Counters                  | 1 – 12                               |

| 1.9<br>1.9.1<br>1.9.2<br>1.9.3 | Comparator Function                      | 1 – 14<br>1 – 14<br>1 – 15<br>1 – 17 |

| 1.10<br>1.10.1<br>1.10.2       | Reference Frequency                      | 1 – 20<br>1 – 20<br>1 – 21           |

| 1.11                           | Switching of Counters Among Each Other   | 1 – 22                               |

| 1.12                           | Command Lists and Measured Value Memory  | 1 – 22                               |

| 1.13                           | Calculation Functions (For IP 242B Only) | 1 – 24                               |

#### 1.1 Features of Counter Module IP 242A/242B

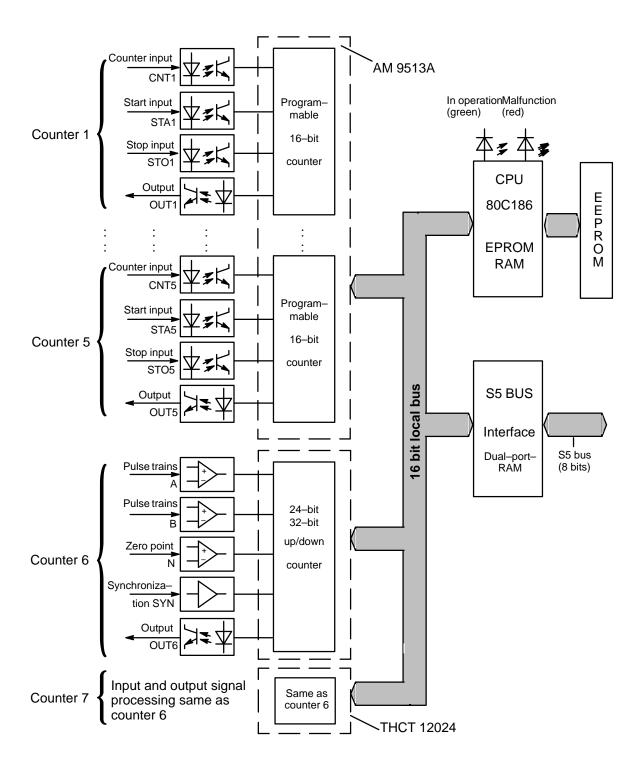

- Five 16—bit counters for general purpose operation with counter input/counter output and gate control (counting up or counting down)

- Counter inputs and gate inputs adjustable to 5 V or 24 V logic and adaptable to signal frequencies up to 480 kHz

- Counter cascading up to 80 bits, decimal counting up to 10<sup>20</sup>

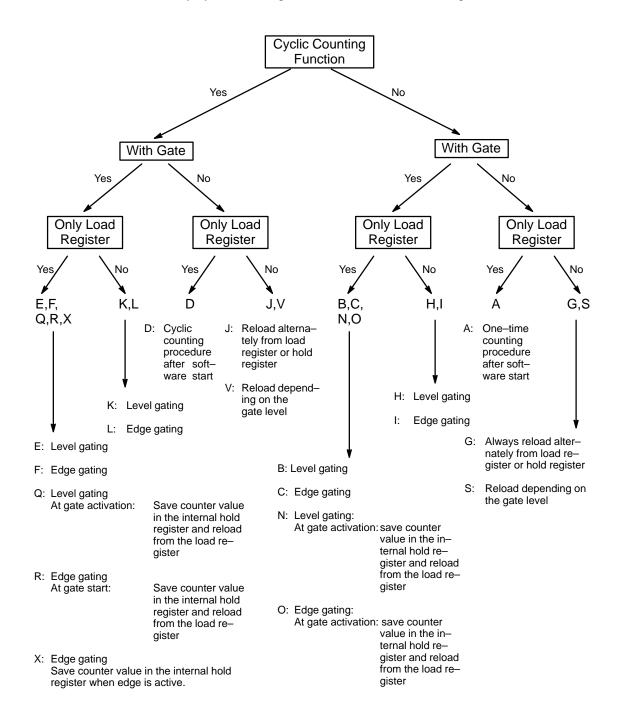

- Nineteen different operation modes for each counter

- Frequency acquisition with internal or external gate control

- Pulse counting

- Pulse counting with comparator function

- Time measurement

- Frequency scaling with programmable scaling factors

- Time delaying

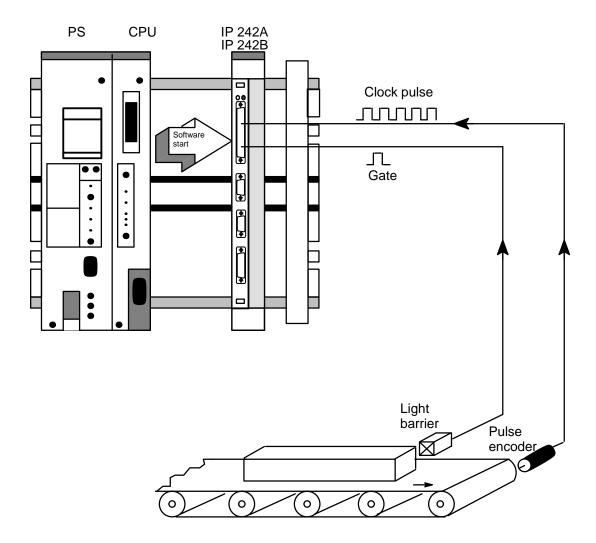

- Variable gate control (e.g., start-stop via light barriers)

- Two counters for acquisition of incremental encoder signals (counting up and down)

- Conting and gate inputs for 5 V signals (RS422) with maximum signal frequencies of 500 kHz

- Counting width: 24 bits for IP 242A

32 bits for IP 242B

- ☐ Control via 16-bit microprocessor 80C186

- Internal frequency generator with 1 mHz and various scalers

- Data exchange with the S5 via dual port RAM (page frame addressing)

- Free parameterization of special functions by the user via command lists

| Optimal process monitoring via integrated interrupt processing     |                                                                                                    |  |  |  |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|--|--|

| Easy handli                                                        | ng and system interface via standard function blocks                                               |  |  |  |

| Parameterization data can be stored on EEPROM in the IP 242A/242B. |                                                                                                    |  |  |  |

| IP 242B:                                                           | Conditioning and storing of measured values                                                        |  |  |  |

| IP 242B:                                                           | Past values can be followed by entering the results in a measured value sequence (trace function). |  |  |  |

| IP 242B:                                                           | Implementation of calculation functions to expand functionality                                    |  |  |  |

#### **Applications**

The IP 242A/B module is designed for use with SIMATIC S5 systems and is used in the following programmable controllers:

| • | S5-115U   | (CPU 941A/B to CPU 944A/B)                                                   |

|---|-----------|------------------------------------------------------------------------------|

| • | S5-135U   | (CPU 922 firmware version 9.0 and later/CPU 928A firmware version –3UA12 and |

|   |           | later/CPU 928B)                                                              |

| • | S5-150U/S | (IP 242A only)                                                               |

| • | S5-155U   | (CPU 946 and CPU 947)                                                        |

The module operates with page frame addressing when used with any of the above programmable controllers.

(When the IP 242A module is used with programmable controllers S5-115U and S5-155U, linear addressing ( $2^{10}$ -byte address volumes) is also possible.

The modules are available under the following order numbers:

IP 242A: 6ES5 242-1AA32 IP 242B: 6ES5 242-1AA41

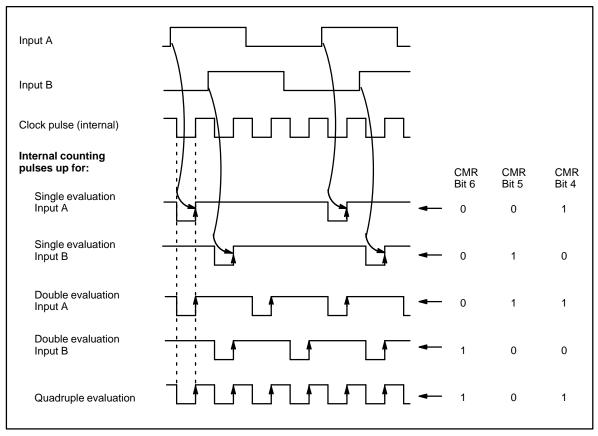

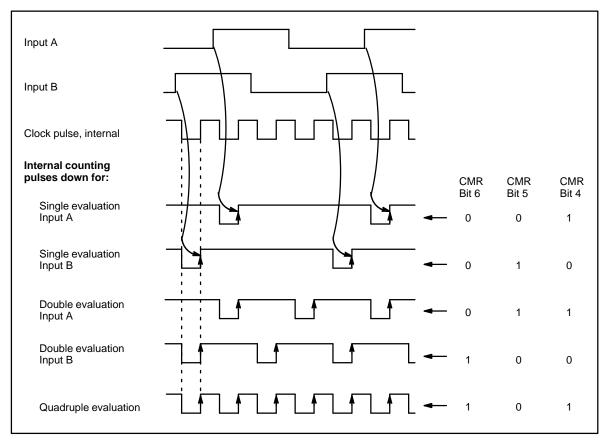

Counters 1 to 5, for which there are 19 operation modes (see section 9), are used either for counting up  $\mathbf{or}$  counting down. Counters 6 and 7 are used to count up  $\mathbf{and}$  down by processing the 90°-displaced input pulses.

Parameterization is performed via the S5 bus.

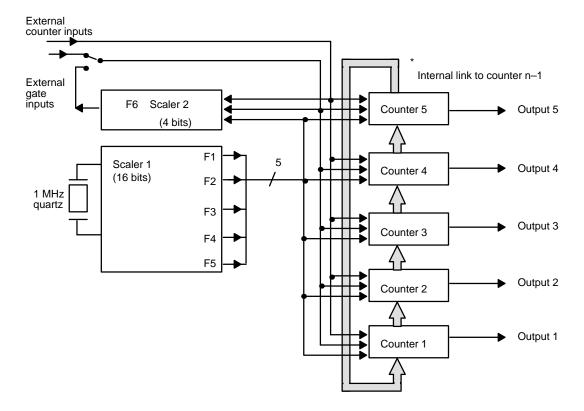

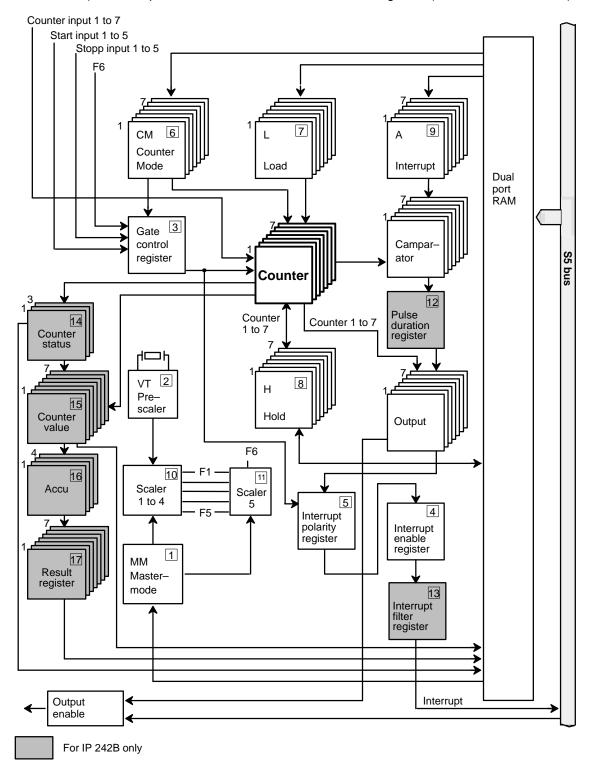

#### 1.2 Hardware Description

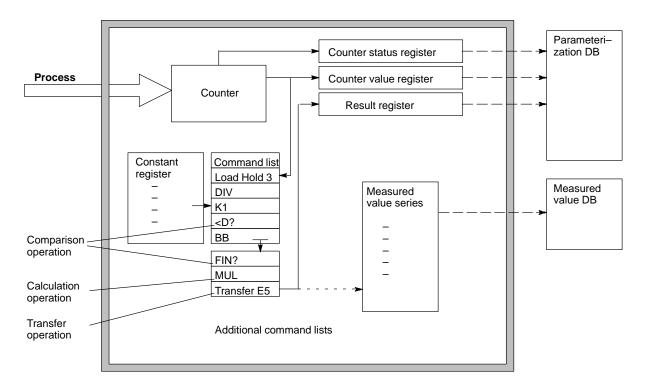

This overview shows the function blocks of the IP 242A/242B counter module.

#### 1.3 16-Bit Counter

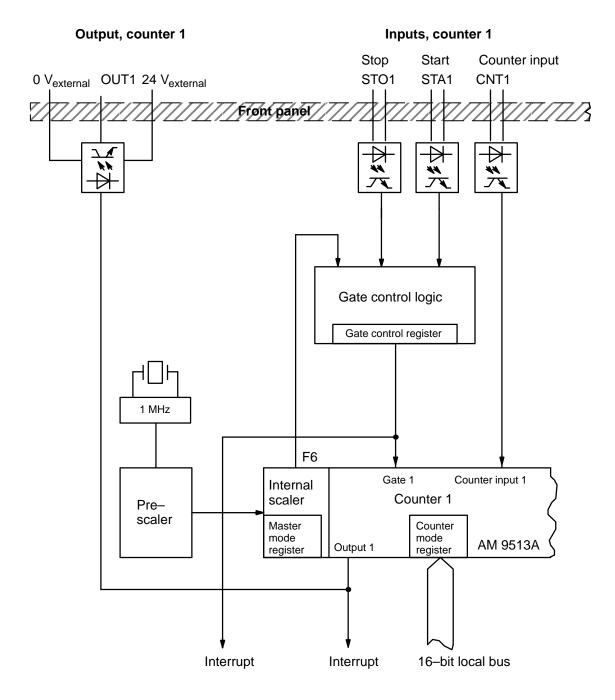

# Block Circuit Diagram of Counter 1 (Counters 2 to 5 are analogous.)

#### 1.4 Inputs of Counters 1 to 5

Five inputs, which are isolated by optocouplers, are available.

Each counter has the following inputs:

- CNT (counter input)

- STA (start input)

- STO (stop input)

The inputs are protected against polarity reversal.

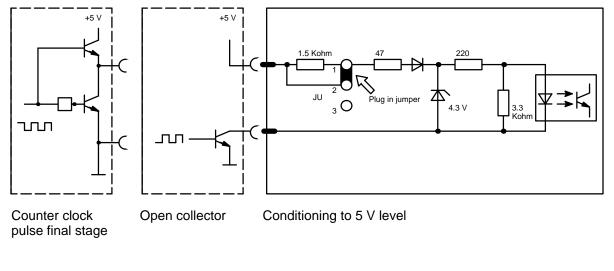

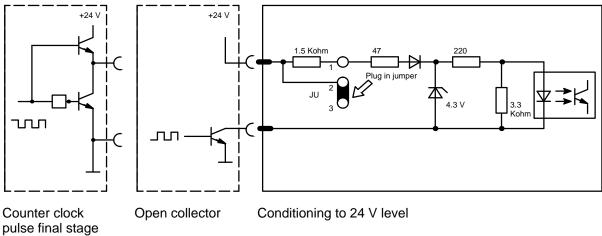

Condition each input to your signal level by using a plug in jumper as shown below:

See section 2.4 for the positions of the plug-in jumpers on the module, their designation, and allocation.

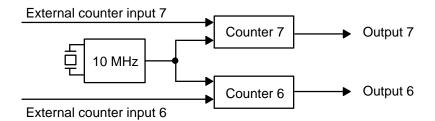

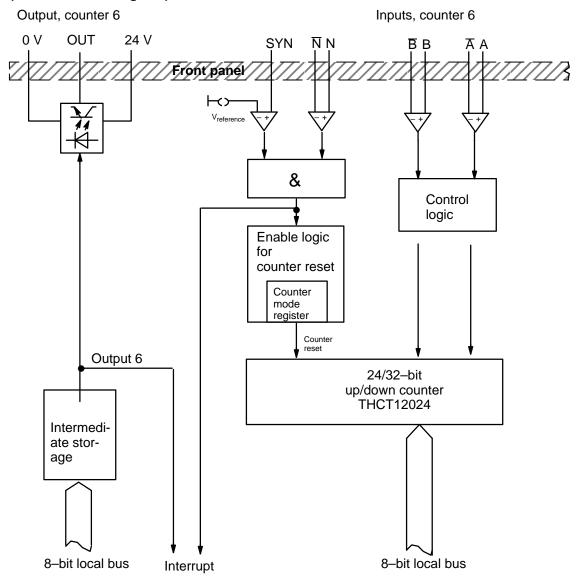

#### 1.5 24/32-Bit Up/Down Counter

Counter pulses from incremental encoders with 90  $^{\circ}$  –displaced pulse trains with RS 422 level are acquired by counters 6 and 7.

Counting width: IP 242A 24 bits IP 242B 32 bits

# Block Diagram of Counter 6 (Counter 7 is analogous.)

The inputs cannot be circuited with 24 V signals unless the "24 V asymmetric to 5 V (RS422) symmetric converter" is used ( $\rightarrow$  section. 10.11).

#### 1.6 Inputs of Counters 6 and 7

The inputs are designed for incremental encoders with two 90° displaced symmetrical output signals, zero pulse, and mechanical zero reset (synchronous pulse).

Counter channels 6 and 7 have the following inputs:

- A Differential input

- B Differential input

- N Differential input, zero marking pulse

- SYN Input for synchronous contact (preliminary contact)

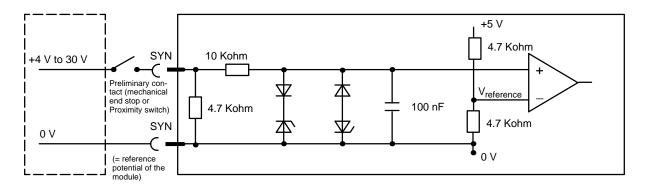

An incremental encoder with RS 422 interface (5 V level) supplies input signals A,  $\overline{A}$ , B,  $\overline{B}$ , and N,  $\overline{N}$ . The suppressor circuit limits the input voltages to approximately 13 V (against 0 V). A preliminary contact (24 V level) provides synchronous signal SYN.

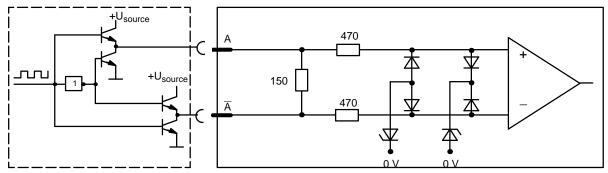

Inputs A, B, and N are designed as differential inputs as shown below:

Counter clock pulse final stage (RS422 driver)

#### Circuitry of the SYN Input:

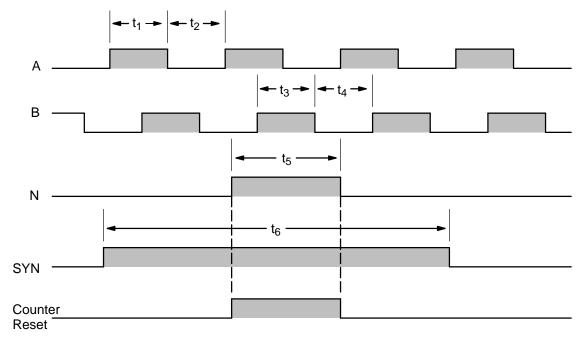

#### Pulse Diagram for Counters 6 and 7:

$$\begin{array}{lll} t_1,\,t_2,\,t_3,\,t_4,\,t_5 & & \geq & 1 \; \text{msec} \\ t_6 & & \geq & 3 \; \text{msec} \end{array}$$

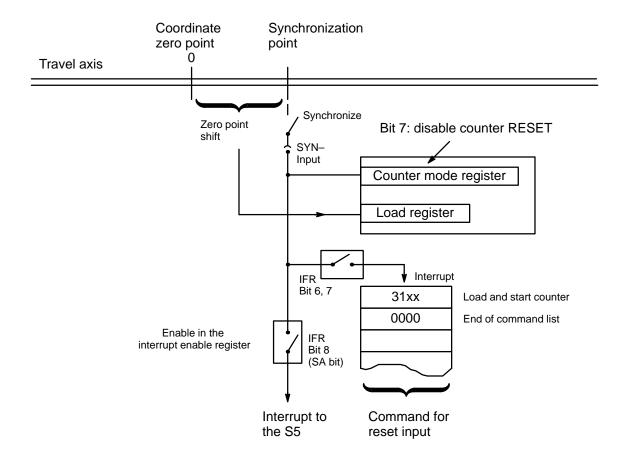

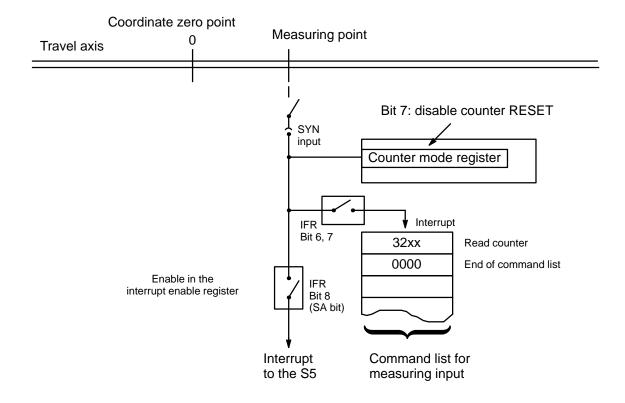

The applicable counter is reset when the zero marking pulse of the encoder coincides with the synchronous pulse. This function can be enabled separately for each counter channel in the counter mode register of counter channels 6 and 7. It is possible to trigger a group interrupt on the S5 central processing unit with the counter reset pulse ( $\rightarrow$  section 3.3.4) and/or activate a command list.

Synchronization occurs at the falling edge of the zero mark pulse. The counter is reset to zero. Section 7.6 contains an example of synchronization with zero point shift.

#### 1.7 Gate Control Logic

Four different types of gate control for counters 1 to 5 are available.

| Gate<br>Mode | Gate Control<br>Register<br>Bit 9   Bit 1<br>(to 13)   (to 5) |                 | Signal<br>Genera-<br>tion | Type of<br>Control          | Signals<br>Used | Explanation (See next page for examples)                                                                  |

|--------------|---------------------------------------------------------------|-----------------|---------------------------|-----------------------------|-----------------|-----------------------------------------------------------------------------------------------------------|

| 1            | 0                                                             | 1<br> <br> <br> | Internal                  | Level                       | F6              | Generated by scaling from the internal frequency generator (1 mHz) (Clock pulse rate is parameterizable.) |

| 2            | 0                                                             | 0               | External                  | Level or edge <sup>1)</sup> | only<br>STA     | Signal <b>only</b> at the start input of the applicable counter                                           |

| 3            | 1                                                             | 0               | External                  |                             | STA/STO         | Signals at the start <b>and</b> stop input of the applicable counter                                      |

| 4            | 1                                                             | 1<br> <br>      | External                  | 7_                          | STA/STO         | Signals at the start <b>and</b> stop input of the applicable counter                                      |

1) The settings in CMR apply when edge control is used.

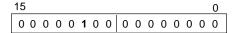

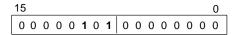

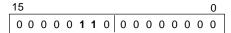

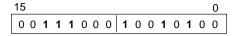

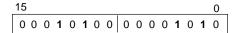

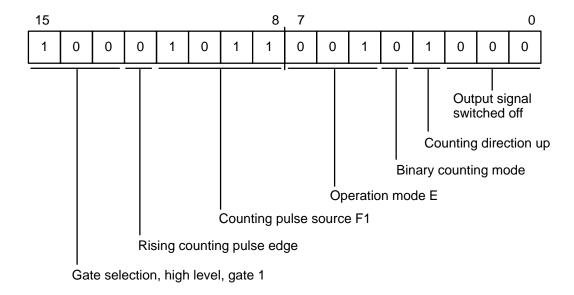

Enter the bit pattern, given in the second and third column, in the gate control register to select a certain gate mode. In the gate control register, two bits are allocated to each counter.

The below schematic drawing shows the main gate switchover logic.

The prescaler, master mode, counter mode, and gate control registers must be allocated to select the gate control.

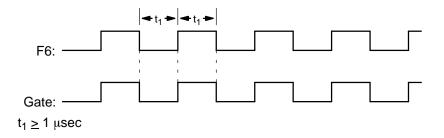

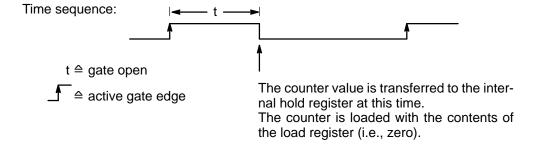

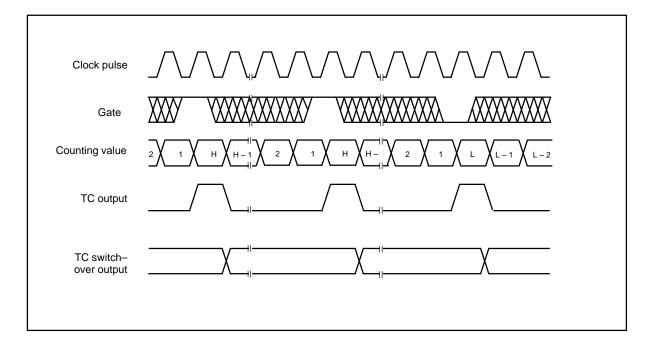

#### Gate Mode 1:

Frequency F6 is applied directly to the gate.

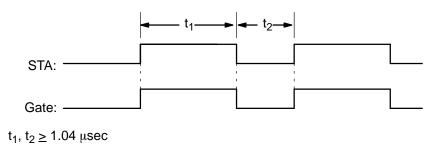

#### Gate Mode 2:

The level/edge at the start input (STA) is applied to the gate.

The appropriate settings in the counter mode register are required for edge-controlled operating modes.

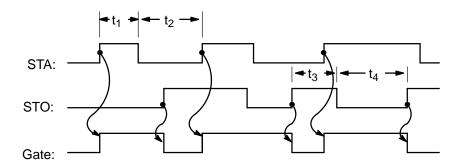

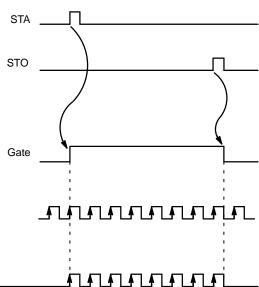

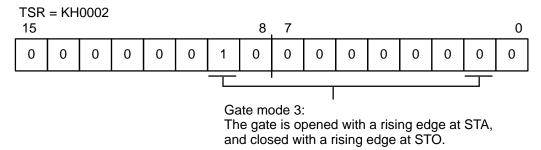

#### Gate Mode 3:

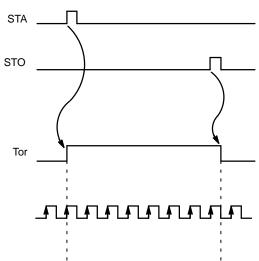

The gate is opened with a rising edge at the start input and closed again with the next rising edge at the stop input.

$t_1, t_2, t_3, t_4 \ge 1.04 \,\mu\text{sec}$

$t_1$ ,  $t_3$  = Pulse width high from STA or STO

$t_2$ ,  $t_4$  = Pulse width low from STA or STO

The start and stop signals must not occur simultaneously. There must be an interval of at least 1.04  $\mu sec$  between both rising edges.

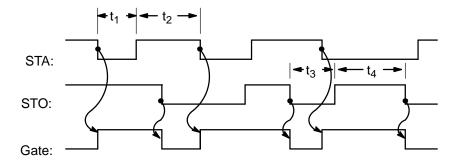

#### Gate Mode 4:

The gate is opened with a falling edge at the start input and closed again with the next falling edge at the stop input.

$t_1, t_2, t_3, t_4 \ge 1.04 \, \mu sec$

$t_1$ ,  $t_3$  = Pulse width low from STA or STO  $t_2$ ,  $t_4$  = Pulse width high from STA or STO

Start and stop signals must not occur simultaneously. There must be an interval of at least 1.04  $\mu sec$ between both falling edges.

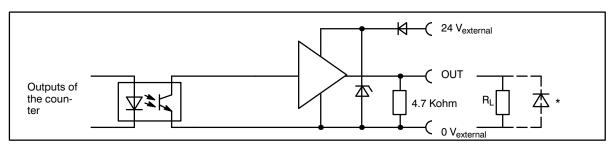

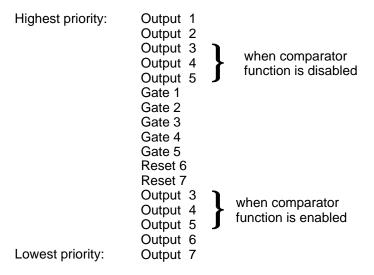

#### 1.8 Outputs of All Counters

Connect an external supply voltage of 24 V for the output signals. This applies to counters 1 to 7 jointly. The outputs are metallically separated from the internal supply voltage by optocouplers.

All counters have the same output circuitry.

The active state of the output signal can be parameterized as follows:

- High pulse (24–V pulse)

- Low pulse (0–V pulse)

- Toggle function

- (alternating between 0–V and 24–V pulses with defined initial status)

- High or low pulse with parameterizable length (IP 242B only)

The desired signal form is selected in the counter mode register of the individual counters ( $\rightarrow$  section 3.4.1).

An output signal is generated as soon as the counter reaches the value of the corresponding interrupt register ( $\rightarrow$  section 3.4.4). In addition, the comparator must be enabled in the master mode register for counters 1 to 5 ( $\rightarrow$  section 3.3.1).

When the IP 242B is used, the length of the pulse can be parameterized in the pulse duration register ( $\rightarrow$  section 3.3.10).

The outputs must be specifically enabled with the FA command (enable outputs); if not, the output of the signals is suppressed.

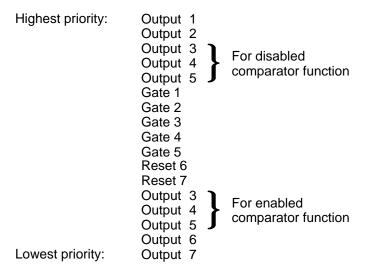

The following table shows when the individual outputs activate.

#### **Output Function**

| Counter Setting                                                  | Counters 1 and 2                              | Counters 3 to 5                                                               | Counters 6 and 7                                                             |        |   |

|------------------------------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------|---|

| Counting cycle zero Counter terminal count                       | High pulse or<br>Low pulse<br>Toggle function | High pulse or<br>Low pulse<br>Toggle function                                 | Illegal                                                                      | A      | В |

| Comparator function<br>Contents of counter =<br>comparison value | High pulse or<br>Low pulse                    | Not available  High or low pulse with parameteri— zable length <sup>2</sup> ) | Not available  High or low pulse with parameteri—zable length <sup>2</sup> ) | A<br>B |   |

| Comparator function Contents of counter ≥ comparison value       | Not available                                 | High level <sup>1)</sup> High level or low level <sup>1)</sup>                | High level <sup>1)</sup> High level or low level <sup>1)</sup>               | A<br>B |   |

- 1) See section 1.9.

- 2) The parameterizable pulse length can be used, for example, to set the minimum pulse duration for switching a contactor. Previously, a separate counter had to be used.

#### **Overload Protection of the Outputs:**

In the event of thermal overload, all outputs are disabled. A thermal overload occurs when the total current of all outputs exceeds 700 mA.

In the event of a short circuit, only the affected output is disabled and switched to low level.

In both cases, an error message is entered in the error information register, and the error LED goes on.

After correction of the short circuit, enable the disabled output again with the FA control word, (enable outputs) from the S5 central processing unit. Remember, however, that all switched on outputs are also briefly disabled by the control word (i.e.,  $\leq$  30 µsec).

#### 1.9 Comparator Function

When the comparator function is enabled, the current counter status is compared to the value stored in the interrupt register.

For counters 1 to 5, the comparator in the master mode register is enabled; for counters 6 and 7, the comparator in the respective counter mode register is enabled.

**1.9.1 Counters 1 and 2** (Only for Actual Value = Interrupt Value)

Comparators 1 and 2 are hardware comparators. When the counter values equal the interrupt values, an output pulse is generated for the period of time in which the values coincide.

| Parameterization in the Counter Mode Register       | Output Signal |  |

|-----------------------------------------------------|---------------|--|

| bit 2 / bit 1 / bit 0 = 001<br>or = 010<br>or = 011 | High pulse    |  |

| bit 2 / bit 1 / bit 0 = 101                         | Low pulse     |  |

An interrupt value of "0" is illegal.

If an interrupt value of "0" is entered in the interrupt register, a message is generated in the error information register when the counter is parameterized. (See section 6.1.22.)

An interrupt value of "0" is also **illegal** if the comparator function in the master mode register has **not** been enabled.

When the comparator function is enabled, the outputs can only be activated by the comparator. For this reason, the outputs cannot be activated at counting cycle zero and at terminal count.

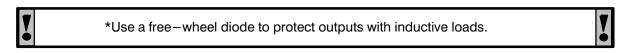

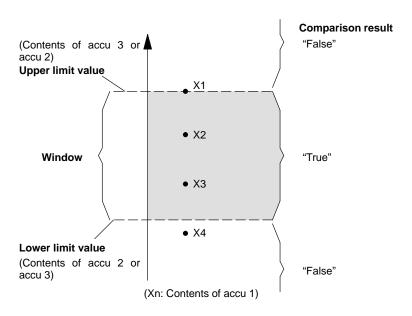

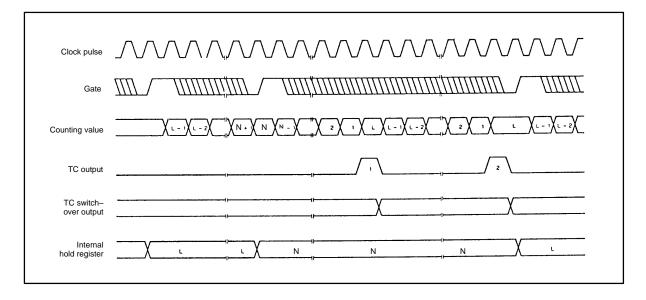

### **1.9.2 Counters 3 to 5** (for Actual Value ≥ Interrupt Value)

Comparators 3 to 5 are software comparators.

The contents of the counter are read out cyclically (approximately 10 msec) and compared with the interrupt value.

An interrupt value of "0" is illegal.

If an interrupt value of "0" is entered in the interrupt register, a message is generated in the error information register when the counter is parameterized. (See section 6.1.22.)

An interrupt value of "0" is also illegal if the comparator function in the master mode register has not been enabled.

When the comparator function is enabled, only the comparator can activate the outputs. For this reason, the outputs cannot be activated at counting cycle zero and at terminal count. Disregard the assignment of bits 0 to 2 in the respective counter mode register.

Y

The software comparator cannot be used with operation modes G, H, I, J, K, L, S, and V.

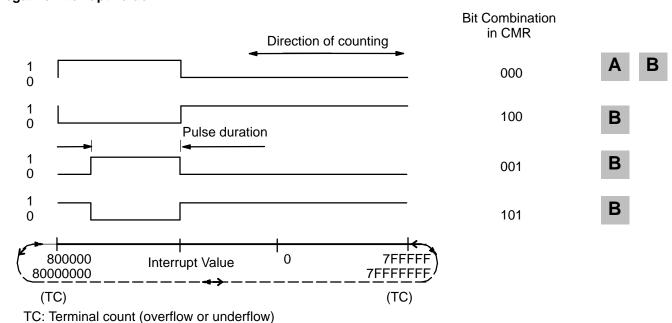

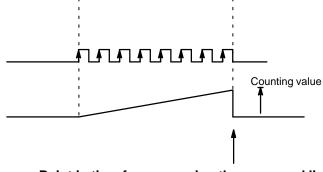

#### Output Signals for Counters 3 to 5

- The interrupt value must be at least 10 msec away from overflow/underflow.

- The output signals can be inverted for the IP 242B.

- A pulse with parameterizable length is available on the IP242B regardless of the direction of counting at the interrupt value.

L/H: Counting value is reloaded from the load or hold register. Interrupt value

IV:

TC: Terminal count (overflow or underflow)

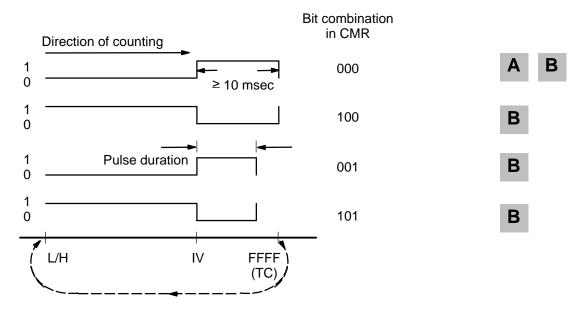

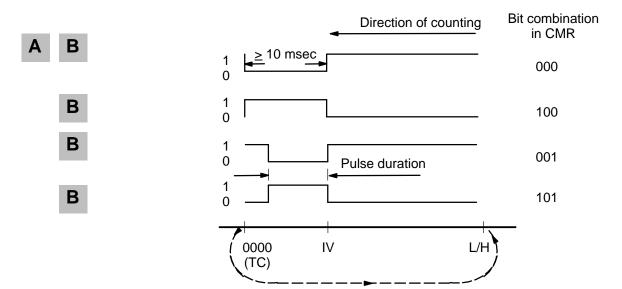

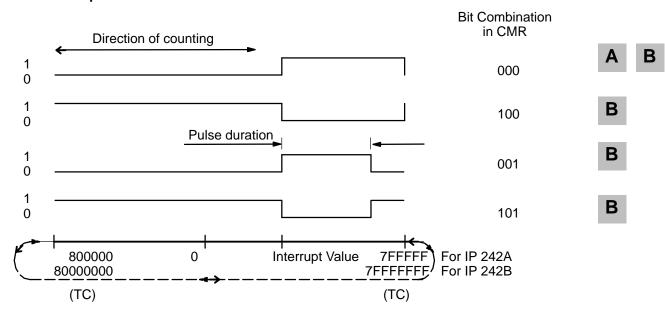

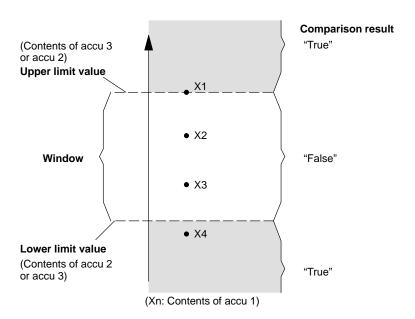

### 1.9.3 Counters 6 and 7

The contents of counters 6 and 7 are cyclically compared with the comparator values.

This comparison is always performed when control words, interrupt requests, and command lists are not being processed. The minimum scanning frequency is determined by the longest break in the processing of a control word, a string of control words (command list), or an interrupt triggered on the S5 central processor. See section 10.8 for processing times of the control words.

#### **Positive Interrupt Value:**

TC: Terminal count (overflow or underflow)

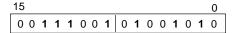

Bit combination

The output is set to "high" outside the interrupt value.

Actual value > interrupt value => output "high".

The output remains on "low" up to the interrupt value

in the range  $800000_{H}$  (= -8 388 608) for IP 242A

80000000<sub>H</sub> (= -2 147 483 648) for IP 242B

A **change in output signal** occurs at overflow/underflow, but no interrupt is generated (no command list can be activated).

The output is set to "high" below the interrupt value.

Actual value < interrupt value => output "high".

The output remains on "low" in the range from interrupt value to  $7FFFFFF_H$  (= 2 147 483 647).

A **change in output signal** occurs at overflow/underflow, but no interrupt is generated (no command list can be activated).

The output gives a high pulse with parameterizable length at the interrupt value.

Actual value = interrupt value => Output remains "high" for the parameterized pulse duration. The output remains on "low" for the remainder of the range.

**No change in output signal** occurs at overflow/underflow and no interrupt is generated (no command list can be activated).

The output gives a low pulse with parameterizable length at the interrupt value.

Actual value = interrupt value => Output remains "low" for the parameterized pulse duration. The output remains on "high" for the remainder of range.

**No change in output signal** occurs at overflow/underflow and no interrupt is generated (no command list can be activated).

#### Positive Interrupt Value (for Gate Time and Frequency Measurement):

TC: Terminal count (overflow or underflow)

Only positive interrupt values are permitted for gate time and frequency measurements. The number range is limited from 0 to FFFFF. The outputs provide the signals as for positive interrupt value (see previous page).

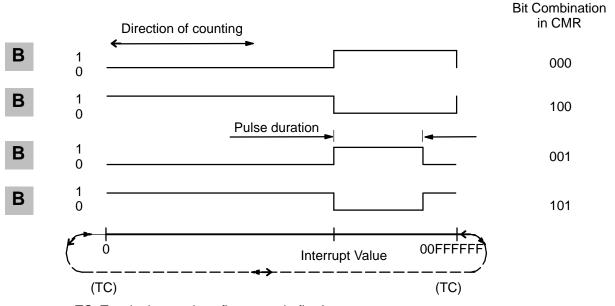

### **Negative Interrupt Value:**

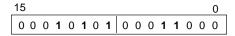

Bit combination 000

101

The output is set to "high" below the interrupt value.

Actual value < interrupt value => output "high".

Actual value ≤ interrupt value => output "high".

The output remains on "low" up to the interrupt value in the range  $7FFFF_H$  (= -8 388 607) for IP 242A

7FFFFFF<sub>H</sub> (= -2 147 483 647) for IP 242B

A **change in output signal** occurs at overflow/underflow, but no interrupt is generated (no command list can be activated).

The output is set to "high" above the interrupt value.

Actual value > interrupt value => output "high".

The output remains on "low" in the range from interrupt value to  $80000000_{\text{H}}$  (= 2 147 483 648).

A **change in output signal** occurs at overflow/underflow, but no interrupt is generated (no command list can be activated).

The output gives a high pulse with parameterizable length at the interrupt value.

Actual value = interrupt value => Output remains "high" for the parameterized pulse duration. The output remains on "low" for the remainder of the range.

**No change in output signal** occurs at overflow/underflow, and no interrupt is generated (no command list can be activated).

The output gives a low pulse with parameterizable length at the interrupt value. Actual value= interrupt value => Output remains "low" for the parameterized pulse duration. The output remains on "high" for the remainder of the range.

**No change in output signal** occurs at overflow/underflow, and no interrupt is generated (no command list can be activated).

## 1.10 Reference Frequency

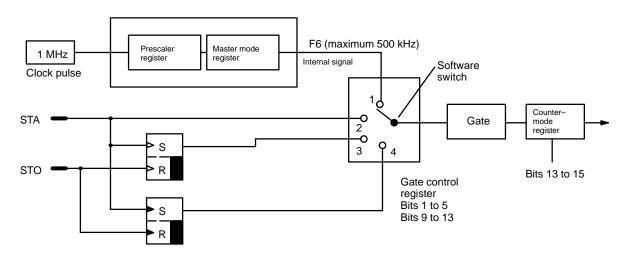

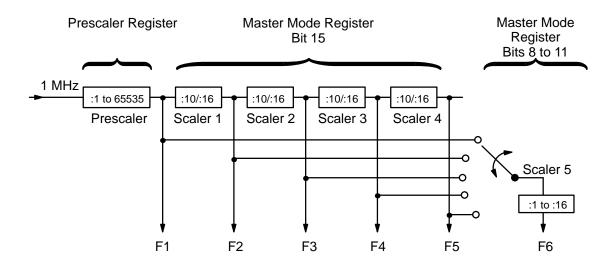

### 1.10.1 Internal Clock Pulses for Counters 1 to 5

Clock pulses F1 to F6 are generated with various frequencies for time or frequency measuring.

The basic clock pulse has a frequency of 1 mHz. This frequency is fed to a prescaler. Output signal F1 of the prescaler serves as the input clock pulse for scaler 1.

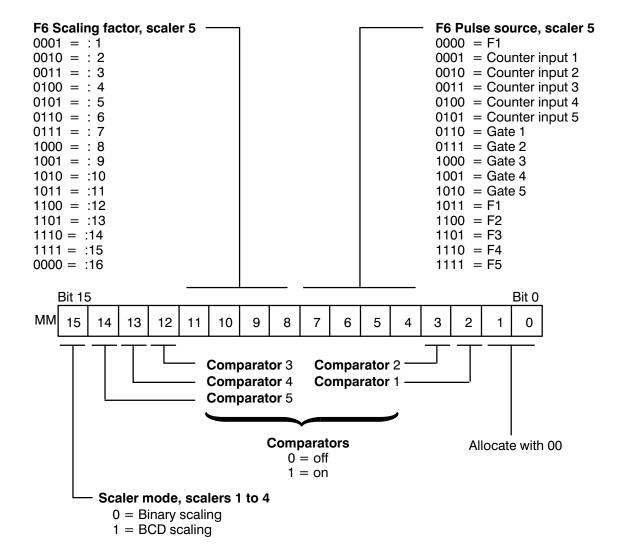

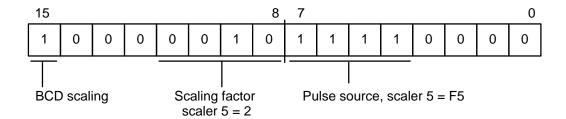

Further frequency scaling is then determined in the master mode register. The clock pulse is divided by four scalers. These scalers have a scaling factor of 10 (BCD scaling) or a scaling factor of 16 (binary scaling). The common scaling factor for scalers 1 to 4 is determined in bit 15 of the master mode register.

The output signals of scalers 1 to 4 are designated as F2, F3, F4, and F5. Together with frequency F1, these signals can be used as input or gate signals for counters 1 to 5.

Frequency F6 is derived from either frequency F1, F2, F3, F4, or F5. The determination of the frequency to be used as the basic clock pulse for frequency F6 takes place in bits 4 to 7 of the master mode register. This frequency is then conducted via scaler 5.

The scaling factor of scaler 5 can be varied from 1 to 16. The scaling factor is determined in bits 8 to 11 of the master mode register.

Frequency F6 can be applied to each gate of counters 1 to 5 via the gate control logic.

Because of the synchronization circuitry, F6 must not exceed 500 kHz (500 kHz \text{\text{\text{P1}}} μsec gate time).

### The following formula is used to calculate the frequencies:

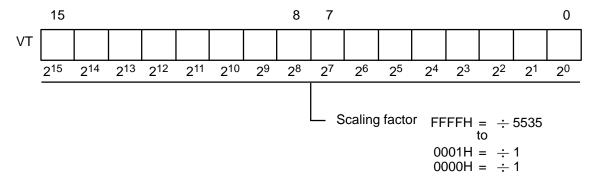

$$F1 = \frac{1 \text{ MHz}}{\text{Prescaler Register}}$$

| Master Mode Register, Bit 15 = 0<br>Binary Scaling :16 | Master Mode Register, Bit 15 = 1<br>BCD Scaling :10 |

|--------------------------------------------------------|-----------------------------------------------------|

| F2 = \frac{F1}{16}                                     | F2 = <u>F1</u><br>10                                |

| $F3 = \frac{F1}{256}$                                  | $F3 = \frac{F1}{100}$                               |

| $F4 = \frac{F1}{4096}$                                 | $F4 = \frac{F1}{1000}$                              |

| F5 = \frac{F1}{65536}                                  | F5 = \frac{F1}{10000}                               |

## The following maximum scaling factors (F6) result:

Maximum scaling factor:

$$65535 \cdot 65536 \cdot 16 = 6.8 \cdot 10^{10}$$

Maximum cycle duration:

68718 sec

Maximum gate time:

34359 sec

## 1.10.2 Internal Reference for Counters 6 and 7

**IP 242B**

The internal reference frequency of 10 MHz is available to counters 6 and 7 for time measurements with a resolution of up to 100 nsec.

## 1.11 Switching of Counters Among Each Other

Basically, counters can be operated separately.

However, more complex applications often require skilled combination of individual counters with different single functions.

Even simple cascading is an example of such a combination ( $\rightarrow$  section 7.1).

The master mode and counter mode registers for counters 1 to 5 make it possible to implement such "switching without external wiring".

This allows, for example, a signal from one single encoder to be used by one counter to acquire the number of revolutions while the second counter uses this signal to make length measurements of parts passing by in connection with the light barriers connected to the gate inputs, etc., etc. (see also section 8.2.2).

There are almost no limits to your imagination.

Remember the following points, however, when implementing your applications:

- The scaling sequence is only present once.

The settings in the MMR apply to all counters (1 to 5).

Of course, you can also give up one counter as an additional scaler.

- 2. The maximum output frequency of all counters (1 to 7) is 40 kHz.

Since there is no internal connection for counters 6 and 7 to counters 1 to 5, or the scaling sequence, circuiting of counters 1 to 5 with counters 6 and 7 always requires an adjustment of the level. A 24 V asymmetrical signal to 5 V (RS422) symmetrical signal converter is available in two–channel design for installation on a top hat rail (→ section10.11).

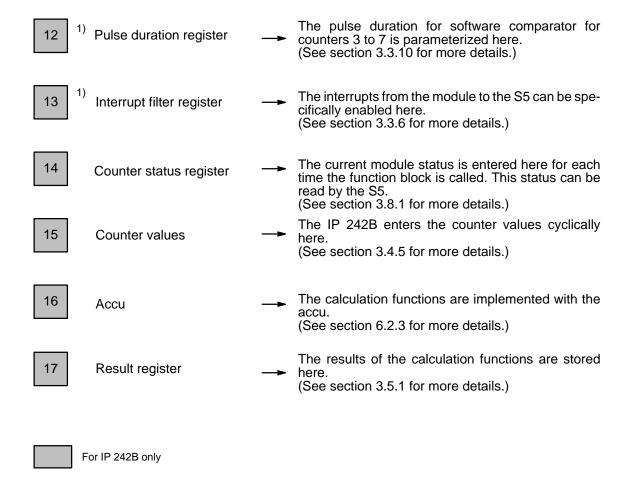

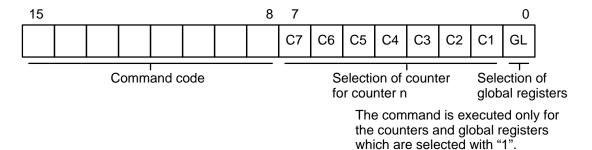

## 1.12 Command Lists and Measured Value Memory

Command lists allow you to store command sequences (i.e., the smallest of "programs") in the IP 242A/242B. The control words used here are the same as those used to address the module with the standard function block from the S5.

Section 6 gives you an overview of the command set and its uses.

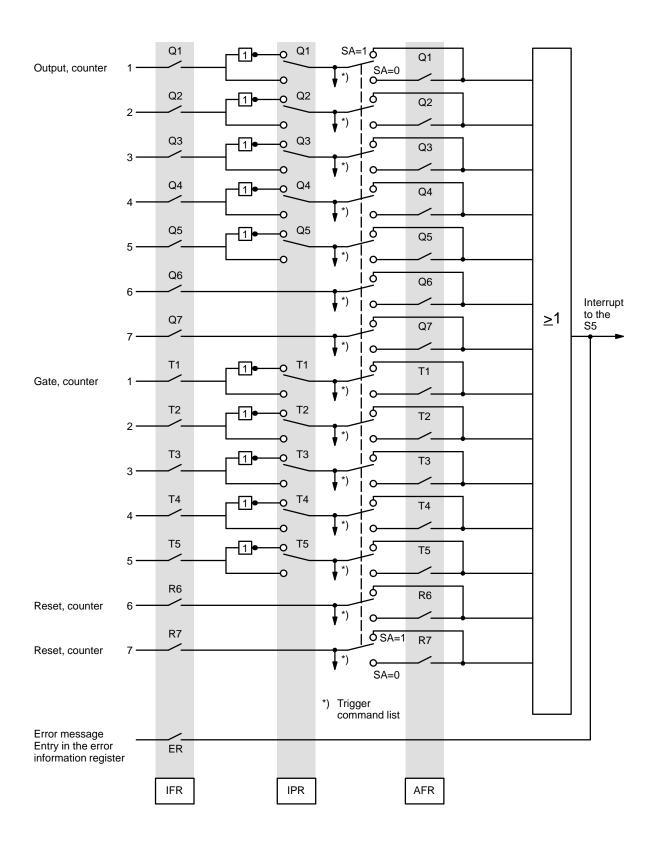

These command lists can be triggered either via the gate inputs of counters 1 to 5, the counter outputs (i.e., a counter which has expired, for example), or via reset inputs 6 and 7.

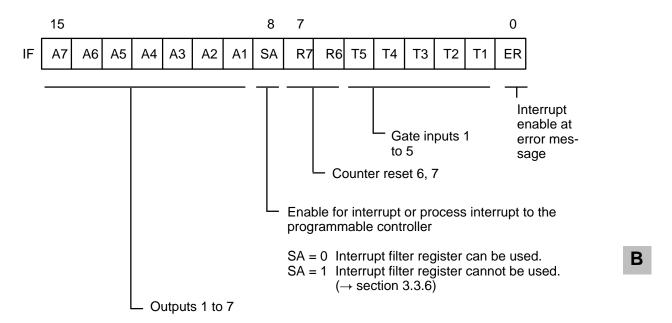

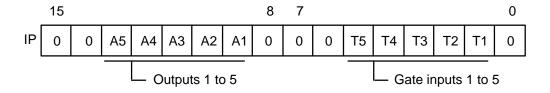

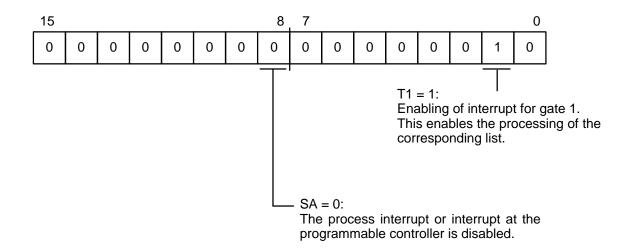

Assuming the enable in the interrupt enable register ( $\rightarrow$  section 3.3.4), you have the choice of simultaneously forwarding this interrupt to the command list or to the S5.

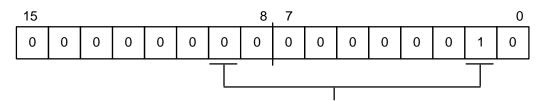

The interrupt filter register of the IP 242B offers you a specific, individual means of influence.

Store the desired command sequence in the parameterization data block. The lists are activated when you transfer the data to the module with the "parameterize counter (global register)".

Additional command lists were installed for the IP 242B since storage space for the interrupt command lists is tight.

The size of these additional command lists can be specified in a separate directory and the lists are enabled there.

They are called with a "process command list" command from one of the interrupt command lists, or by the same command in the standard function block from the S5.

Interrupt command lists must be concluded with the "command list end" command (BE) when a list contains less than five commands. The additional command lists are managed in a separate directory.

What can be accomplished with such a command list?

Individual counters can be controlled separately.

But the greatest advantage is that you can use the transfer, calculation and comparison value functions together with the constants and/or process conditions which can be specified, the counter values, etc. to combine the seven counters into a more complex "circuit" which, most importantly, is independent of the S5 ( $\rightarrow$  sections 6.2. and 1.13).

And, of course, you can also program "abbreviated" calculations with up to 5 commands in the interrupt command lists.

#### A Simple Example:

With the IP 242A, you could generate a difference of two counters directly on the module. With the IP 242B, you can now even acquire the difference of several counters on board, and use the comparison function together with the counters and their direct digital outputs to achieve very fast effects on the process.

You can also buffer the results of your calculations and links parallel to the new result registers in a measured value memory (up to  $100 \cdot 2$  DWs), and fetch all of them from the S5 when required ( $\rightarrow$  sections 1.13 and 3.7.2).

This increased flexibility makes it impossible to list all capabilities here.

For this reason, sections 7 and 8 are only an introduction to the basics, and are primarily intended to arouse your interest in the many ways in which you can now solve technological tasks.

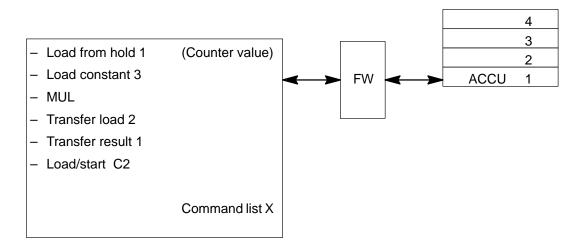

## 1.13 Calculation Functions (For IP 242B Only)

The IP 242B permits simple calculation operations to be performed directly on the module without using the S5 CPU. The required commands are grouped together in the interrupt and/or additional command lists.

Section 8 contains an example of how and when the calculation functions can be used.

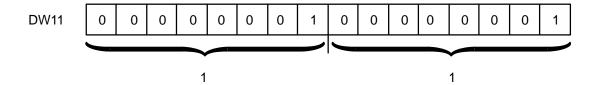

A calculation stack of 4 accumulators, all of which are updated for every load and calculation command, is used for the calculation functions.

A command list can be started via the following.

- Gate interrupt

- Output interrupt

Additional command lists can be started via the following.

- Internally in the command list with the "process command list" control word

- Externally via the control word register with the "process command list" control word

The accumulators must be appropriately loaded before the actual calculation operations are executed ( $\rightarrow$  section 6.2.4). This is done with the "load from register" or "exchange accumulators" transfer operations ( $\rightarrow$  section 6.2.3). After the calculation, the result is loaded in a result register with the "transfer in register" control word, for example. It can be accessed there with a "read" command.

The comparison operations can be used for conditional jumps in a command list ( $\rightarrow$  section 6.2.5).

R 02/93 Contents

# 2 Hardware Settings

| 2.1 | Layout of the Setting Elements                                    | 2 – 1 |

|-----|-------------------------------------------------------------------|-------|

| 2.2 | Setting of the Module Address                                     | 2 – 2 |

| 2.3 | Interrupts and Process Interrupts                                 | 2 – 4 |

| 2.4 | Level Conditioning of Counter Inputs 1 to 5                       | 2 – 7 |

| 2.5 | Frequency Conditioning for Counter Frequencies of Counters 1 to 5 | 2 – 8 |

| 2.6 | Front Panel and Front Connectors                                  | 2 – 0 |

R 02/93 Hardware Settings

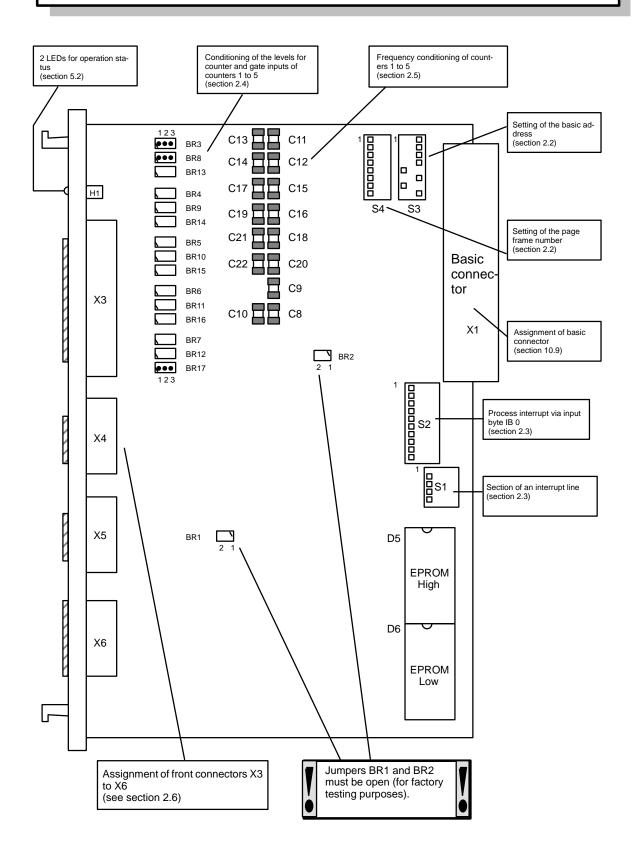

## 2.1 Layout of the Setting Elements

Hardware Settings R 02/93

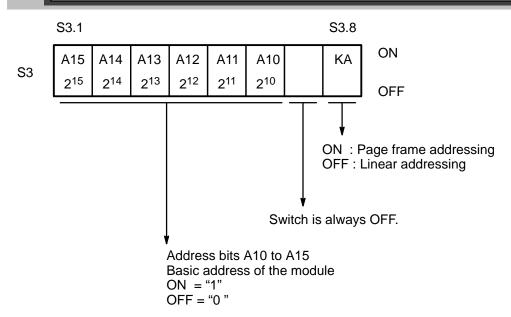

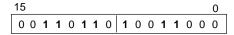

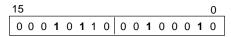

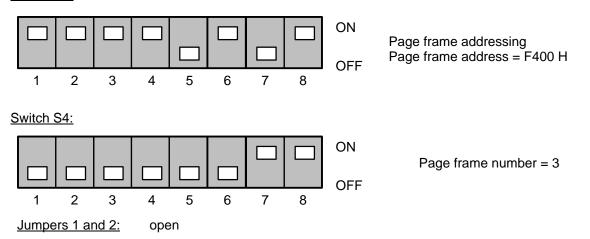

## 2.2 Setting of the Module Address

#### **Basic Address**

The IP 242A occupies one page frame or a 2<sup>10</sup>–byte area of memory in the I/O area of the programmable controller's central processing unit.

The IP 242B occupies one page frame.

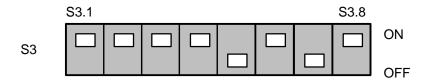

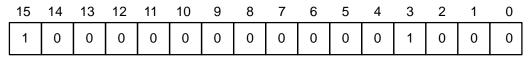

Use DIP switch S3 to set the basic address.

The module usually operates with page frame addressing.

Linear addressing is only possible with programmable controllers S5–115U and S5–155U using the IP242A.

Set the basic address to F400H (status on delivery) when using page frame addressing.

The IP 242B uses only function blocks which support page frame addressing. Switch S3.8 is always ON.

#### **Example:**

The module is addressed linearly. Basic address is E000H.

R 02/93 Hardware Settings

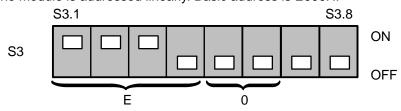

### Status on Delivery:

Page frame addressing is selected and set to F400H.

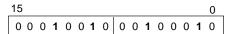

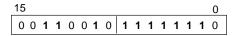

## Page Frame Number

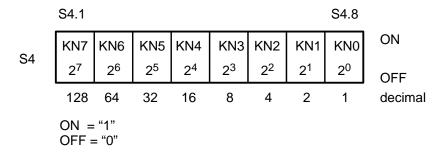

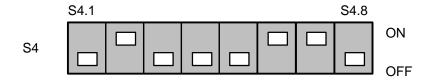

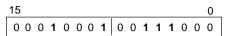

In addition to basic address F400H, the page frame number must also be set on the module for page frame addressing. The page frame number consists of 8 bits (bits 0 to 255) and is set with DIP switch S4.

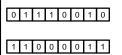

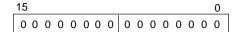

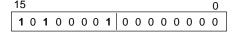

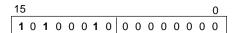

### **Example:**

Page frame number = 70 (46H)

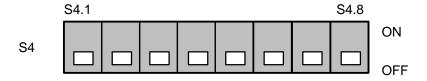

### Status on Delivery:

Page frame number = 00H

Hardware Settings R 02/93

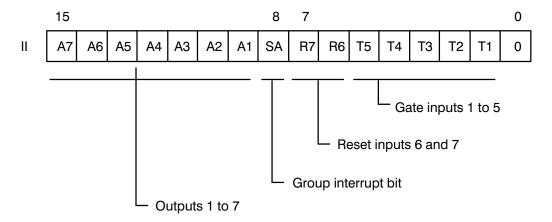

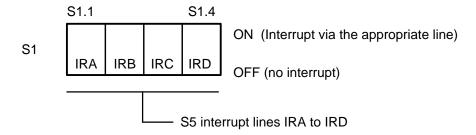

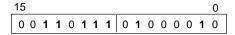

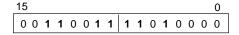

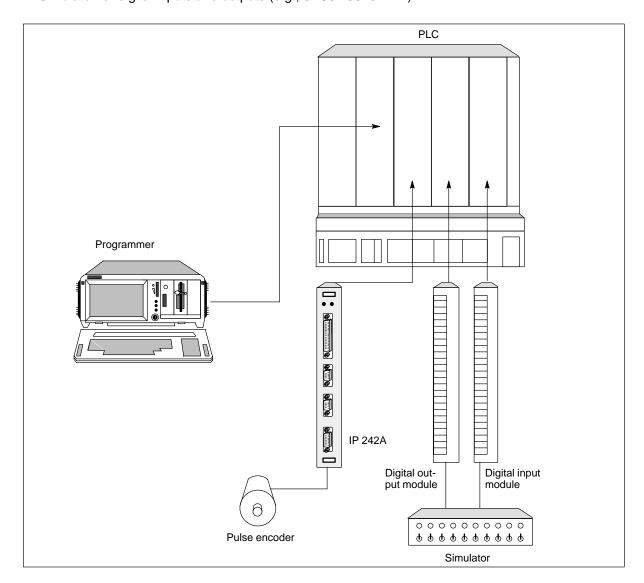

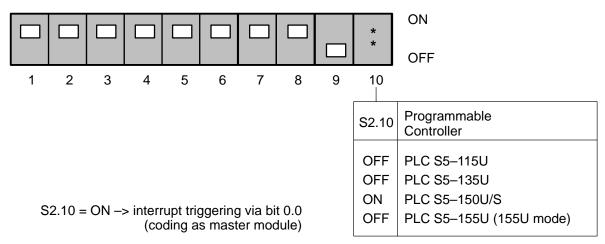

## 2.3 Interrupts and Process Interrupts

#### **Selecting an Interrupt Line**

Interrupt processing via interrupt lines or input byte IB 0 depends on the programmable controller (see section 4, "Interrupt Processing").

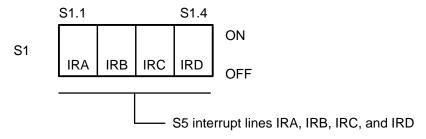

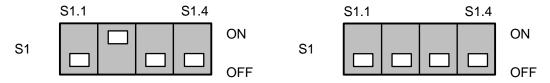

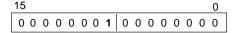

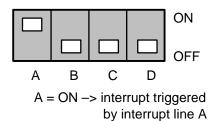

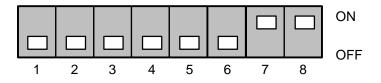

Set DIP switch S1 to select the S5 interrupt line which triggers interrupts on the S5 central processing unit.

Set only one switch to ON.

ON: Interrupt via corresponding line

OFF: No interrupt

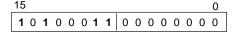

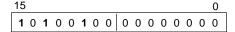

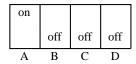

#### **Example:**

#### Status on Delivery:

Interrupt via interrupt line IRB

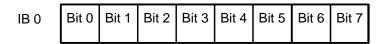

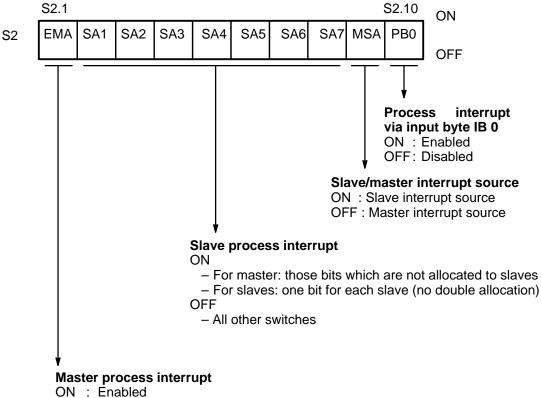

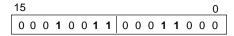

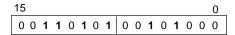

#### Process Interrupt via Input Byte IB 0

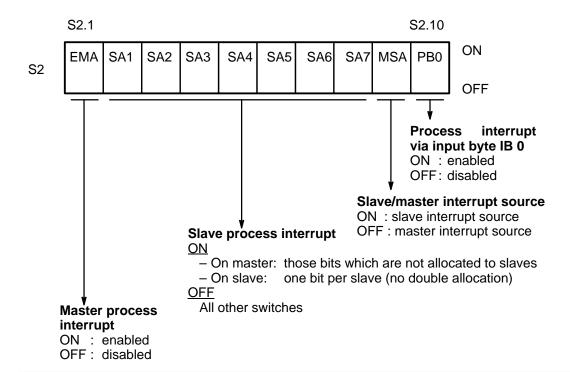

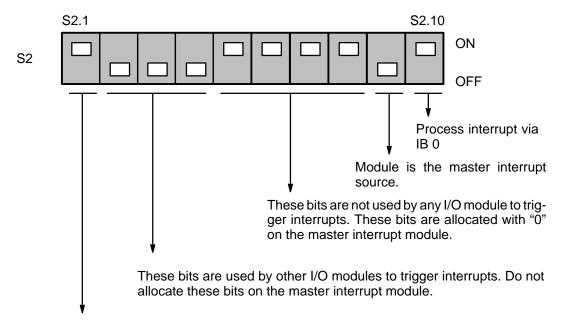

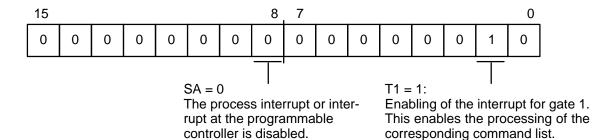

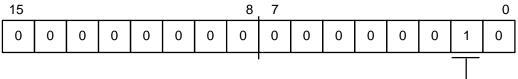

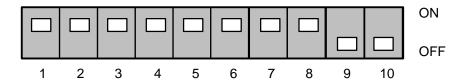

For page frame addressing and triggering of process interrupts via input byte IB 0, define the first module as master interrupt source and all other modules as slave interrupt sources. Processing of process interrupts is not possible (switch S2.10 = off) for linear addressing.

Set this configuration with DIP switch S2.

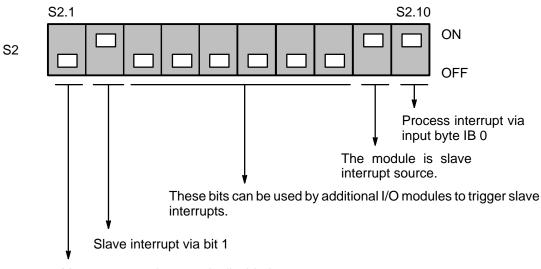

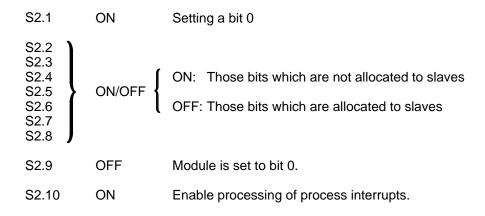

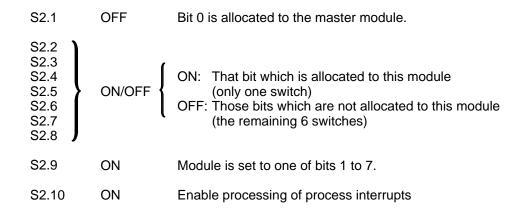

#### Slave:

For every module defined as a slave interrupt source, close only switches S2.9, S2.10, and one of switches S2.2 to S2.7 (no double allocation). The corresponding bit of input byte IB 0 is thus assigned to this module.

#### Master:

For the module defined as master interrupt source, close only switches to which no slave interrupt sources are assigned (i.e., do not use the corresponding bits of input byte IB 0 in your S5 system).

R 02/93 Hardware Settings

Do not use input/output modules with input bytes IB 0 and IB 1 when DIP switch S2.10 is ON.

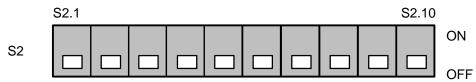

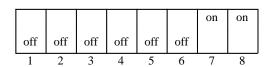

### Status on Delivery:

The following table shows the switch positions for three counter modules which are to operate as master, slave 1, and slave 6:

|       |            |                   | x = ON | _       | = OFF   |

|-------|------------|-------------------|--------|---------|---------|

| IB 0  | DIP Switch | Type of Interrupt | Master | Slave 1 | Slave 6 |

| Bit 0 | S2.1       | Master interrupt  | х      | _       | _       |

| Bit 1 | S2.2       | Slave interrupt   | _      | х       | _       |

| Bit 2 | S2.3       | No interrupt      | х      | _       | _       |

| Bit 3 | S2.4       | No interrupt      | х      | _       | _       |

| Bit 4 | S2.5       | No interrupt      | х      | _       | _       |

| Bit 5 | S2.6       | No interrupt      | х      | _       | _       |

| Bit 6 | S2.7       | Slave interrupt   | _      | _       | х       |

| Bit 7 | S2.8       | No interrupt      | Х      | _       | _       |

|       | S2.9       |                   | _      | Х       | х       |

|       | S2.10      |                   | х      | х       | х       |

Hardware Settings R 02/93

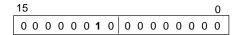

### Example 1:

The group interrupt is triggered via input byte IB 0. The IP 242A/242B is the master interrupt source. The programmable controller uses 3 additional interrupts.

The master process interrupt is enabled.

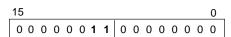

#### Example 2:

The IP 242A/242B triggers process interrupts via input byte IB 0 (SA1). The module is a slave interrupt source.

Master process interrupt is disabled.

R 02/93 Hardware Settings

## 2.4 Level Conditioning of Counter Inputs 1 to 5

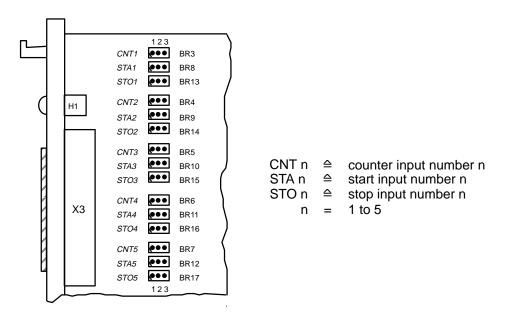

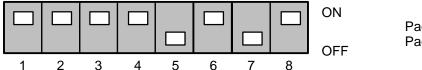

Use plug in jumpers BR3 to BR17 to set each of the inputs to 5 V level or to 24 V level.

The following section of the printed circuit board shows the location and designation of the plug in jumpers.

| Jumper          | Jump   | oer Alloc | Input Level |      |

|-----------------|--------|-----------|-------------|------|

| BR <sub>X</sub> | 1<br>o | 2         | 3<br>O      | 5 V  |

| BR <sub>X</sub> | 1<br>0 | 2         | 3           | 24 V |

| BR <sub>X</sub> | 1      | 2<br>0    | 3<br>O      | 24 V |

$$x = 3 \text{ to } 17$$

### Example:

Insert jumpers BR5, BR10, and BR15 in position 1-2 to condition the count, start, and stop inputs of counter 3 to a 5-V level.

#### Status on Delivery:

Jumpers BR3 to BR17 are inserted in position 2-3 (24 V).

Hardware Settings R 02/93

## 2.5 Frequency Conditioning for Counter Frequencies of Counters 1 to 5

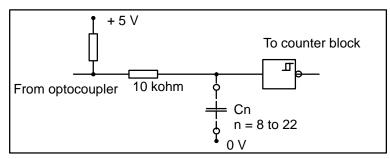

If there is a danger of interference signals occurring despite external shielding, use capacitors C8 to C22 to reduce interference susceptibility.

The count, start, and stop inputs are then conditioned to the maximum counter frequency.

High frequency interference pulses are thus blanked out, particularly when processing relatively low frequencies.

The below drawing shows the position of one of these capacitors in the input circuitry.

Use the following table to determine what size capacitors to select. The specified values are intended as guide lines. Other values are also possible.

| Maximum<br>Counting Frequer                                                      | C8 to C22                                         |

|----------------------------------------------------------------------------------|---------------------------------------------------|

| Approximately 48 Approximately 20 Approximately 2 Approximately Approximately 20 | 00 kHz   100 pF<br>20 kHz   1 nF<br>2 kHz   10 nF |

Now solder the selected capacitors in the corresponding slots.

#### Status on Delivery:

**No** capacitors are soldered in when your module is delivered from the factory (i.e., counting frequency up to 480 kHz).

Please be careful not to get soldering tin and wire clippings on the printed circuit board while soldering. This can cause short circuits which not only affect the functions but also destroy your module.

Use 5-mm capacitors.

R 02/93 Hardware Settings

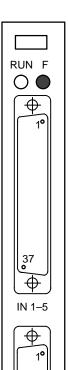

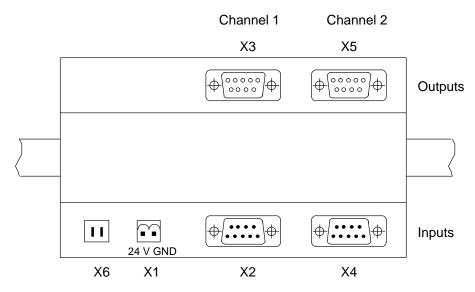

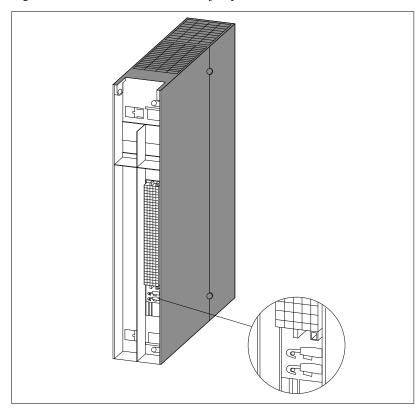

## 2.6 Front Panel and Front Connectors

The illustration shows the front panel with labelling and connectors.

IN 6

•9

RUN LED (green) / F LED (red) (operating) (malfunction)

X3: 37–way sub D connector (pins)

Counter and gate inputs (start, stop) of counters 1 to 5

X5: 9-way sub D connector (pins) Inputs for counter 7 (incremental encoder)

X6: 15–way sub D connector (sockets) Outputs for counters 1 to 7

15

Hardware Settings R 02/93

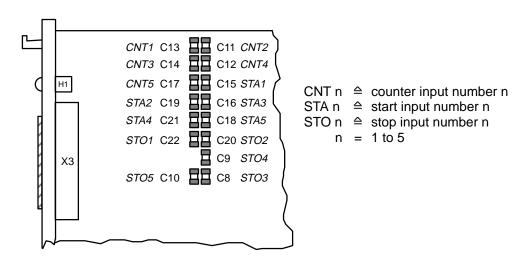

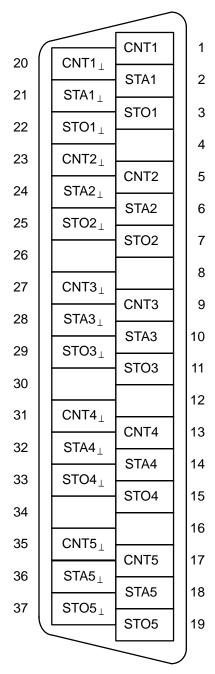

#### 1. Allocation of Front Connector X3:

Start, Stop, and Count Inputs of Counters 1 to 5:

Signal Designation: CNTn: counter input, counter n

STAn : start input, counter n STOn: stop input, counter n

reference potential of the corresponding input xxxn⊥ :

R 02/93 Hardware Settings

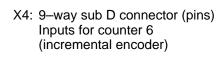

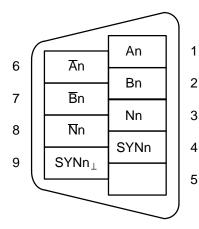

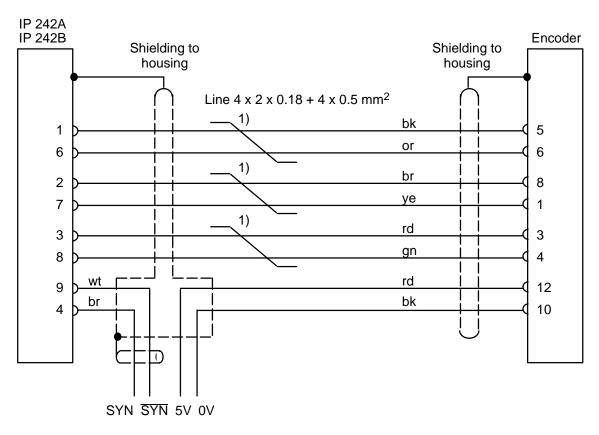

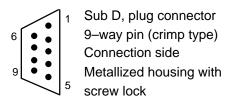

#### 2. Allocation of Front Connectors X4 and X5:

Inputs of Counters 6 and 7:

Signal Designation:

An,  $\overline{A}$ n : differential counter input, counter n Bn,  $\overline{B}$ n : differential counter input, counter n Nn,  $\overline{N}$ n : differential input, zero marking pulse

3 SYNn : input, synchronous pulse

SYNn<sub>⊥</sub> : reference potential, synchronous input

(= reference potential of the counter module)

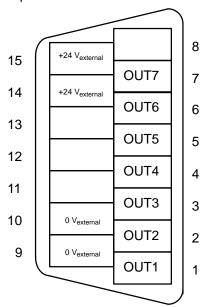

## 3. Allocation of the 15-Way Sub D Socket Connector X6:

Outputs of All Counters:

Signal Designation:

OUTn : output of counter n +24 V<sub>external</sub> : external supply voltage

0 V<sub>external</sub> : external reference potential for +24 V<sub>external</sub>

Follow the SIMATIC S5 configuration guidelines when connecting the front plug connectors to ensure smooth IP 242A/242B operation.

Since interferences can also occur on the external supply voltage lines:

- Keep the lines short.

- Use a filter for longer lines.

# **3 Software Settings (Registers)**

| 3.1                                                                                            | Overview of the Registers                                                                                                                                                                                                                                                                                                                        | 3 – 1                                                                             |

|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| 3.2                                                                                            | Definition of the Registers                                                                                                                                                                                                                                                                                                                      | 3 – 2                                                                             |

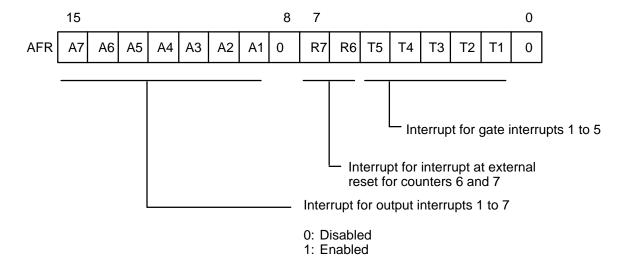

| 3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.3.7<br>3.3.8<br>3.3.9<br>3.3.10 | Description of the Global Registers  Master Mode Register (MMR)  Prescaler Register (VTR)  Gate Control Register (TSR)  Interrupt Enable Register (IFR)  Interrupt Polarity Register (IPR)  Interrupt Filter Register (AFR)  Difference Register (DR)  Version Number Register (VNR)  FB Version Identifier (FBV)  Pulse Duration Register (PDR) | 3 - 4<br>3 - 5<br>3 - 6<br>3 - 7<br>3 - 8<br>3 - 10<br>3 - 11<br>3 - 12<br>3 - 12 |

| 3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5                                               | Description of the Counter Registers Counter Mode Register (CMR) Load Register (LR) Hold Register (HR) Interrupt Register (AR) Cyclic Counter States (ZSZ)                                                                                                                                                                                       | 3 - 13<br>3 - 13<br>3 - 16<br>3 - 18<br>3 - 19<br>3 - 19                          |

| 3.5<br>3.5.1<br>3.5.2                                                                          | Description of the Registers for the Calculation Functions Result Register (ERG) Constant Register (KON)                                                                                                                                                                                                                                         | 3 - 20 $3 - 20$ $3 - 20$                                                          |

| 3.6<br>3.6.1<br>3.6.2                                                                          | Description of the Registers for Additional Command Lists  Directory of the Additional Command Lists (DZB)  Additional Command Lists (ZB)                                                                                                                                                                                                        | 3 – 21<br>3 – 21<br>3 – 22                                                        |

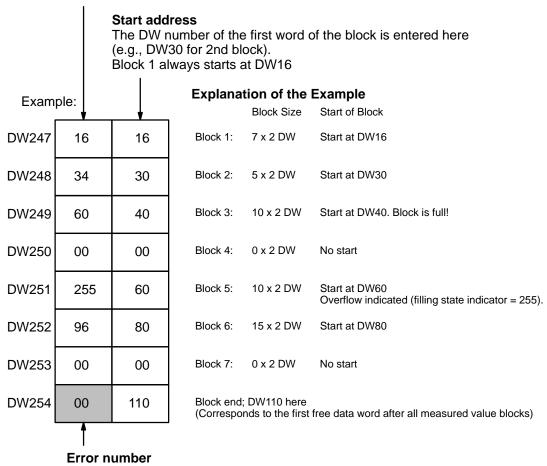

| 3.7<br>1.6.1<br>3.7.2                                                                          | Description of the Registers for Measured Values  Directory of the Measured Value Memory (DM)  Measured Value Memory (M)                                                                                                                                                                                                                         | 3 – 22<br>3 – 22<br>3 – 24                                                        |

| 3.8<br>3.8.1<br>3.8.2<br>3.8.3<br>3.8.4                                                        | Description of the Information Registers Counter Status Register (ZSR) Interrupt Information Register (IIR) Error Information Register (ERR) Error Address Command List (FAB)                                                                                                                                                                    | 3 - 25 $3 - 25$ $3 - 26$ $3 - 27$ $3 - 29$                                        |